Изобретение относится к вычислительной технике и может быть использовано в аппаратуре для магнитной записи цифровой информации.

Целью изобретения является упроще- ние устройства.

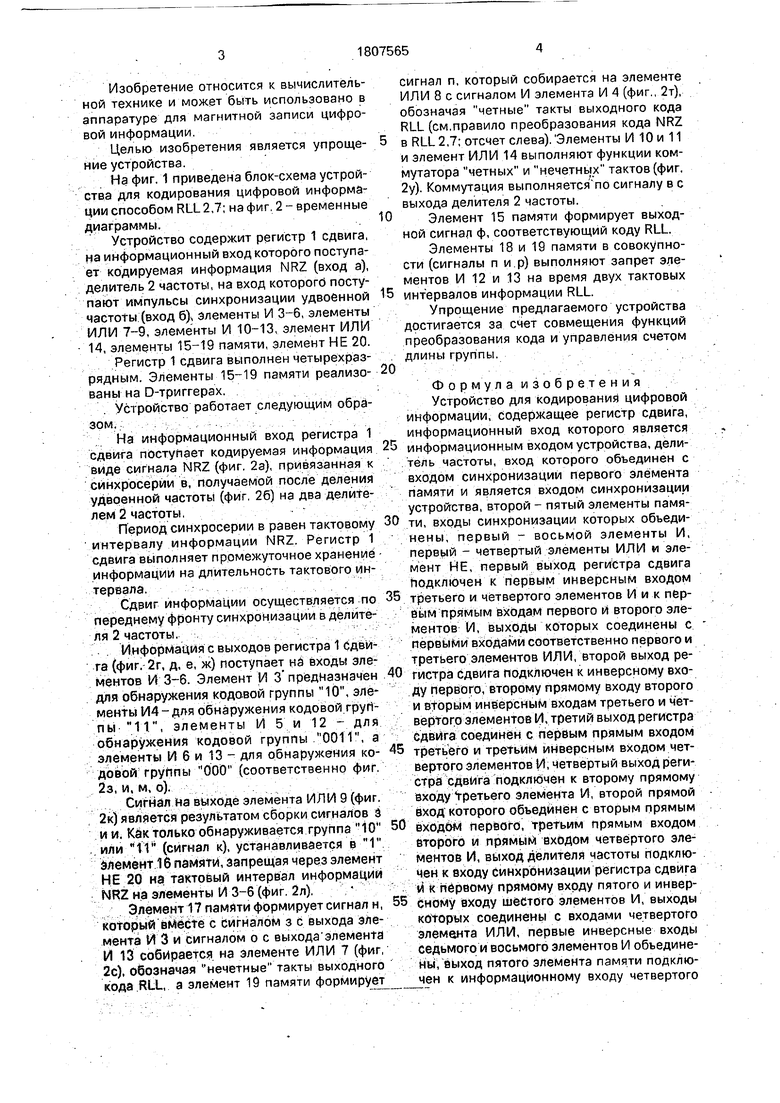

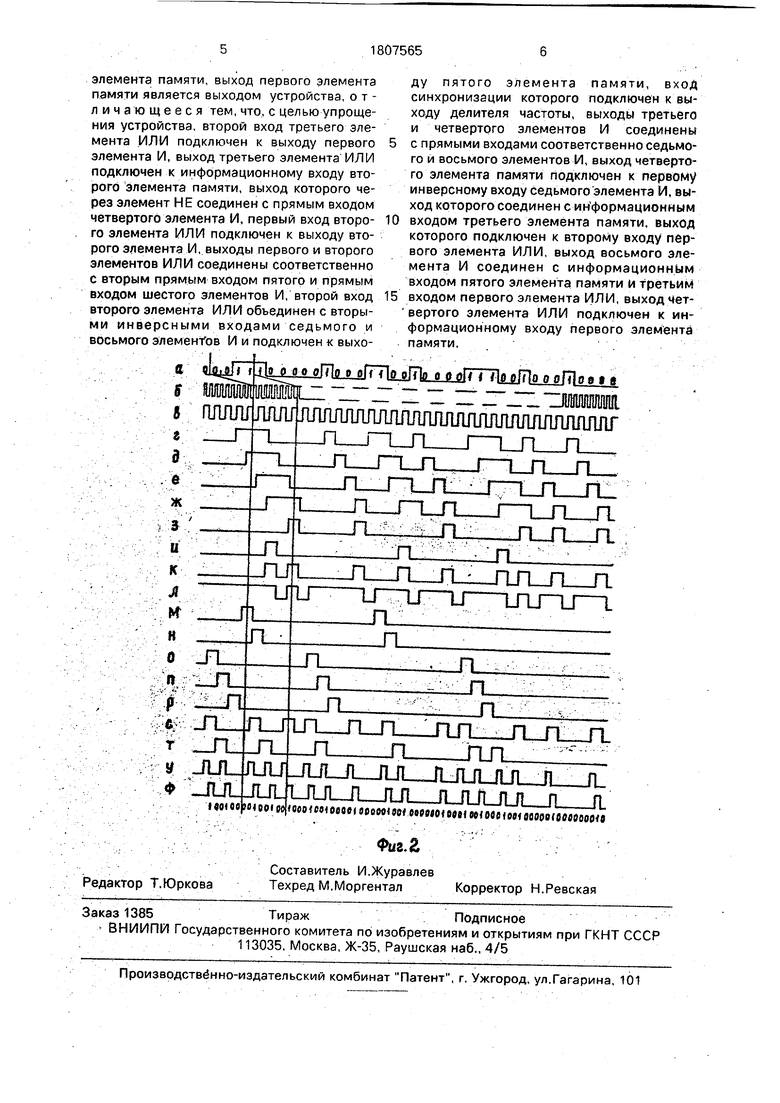

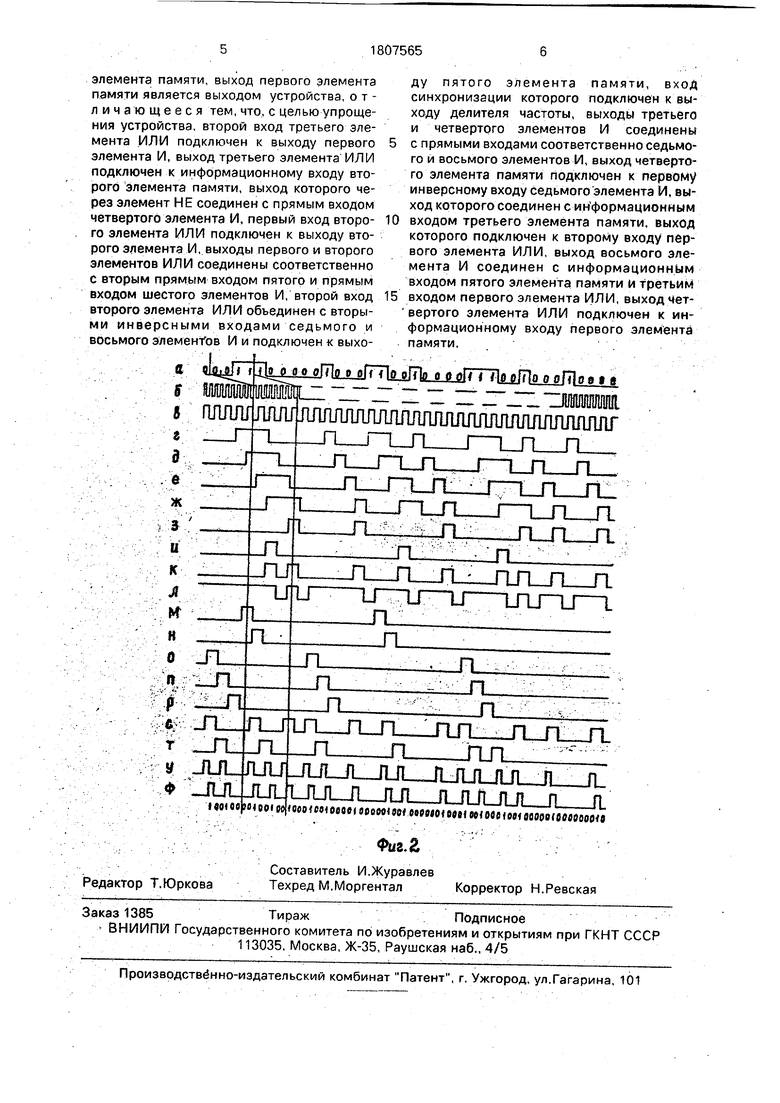

На фиг. 1 приведена блок-схема устройства для кодирования цифровой информации способом RLL2J; на фиг. 2-временные диаграммы..

Устройство содержит регистр 1 сдвига, на информационный вход которого поступает кодируемая информация NRZ (вход а), делитель 2 частоты, на вход которого поступают импульсы синхронизации удвоенной частоты (вход б)ч элементы И 3-6, элементы ИЛИ 7-9, элементы И 10-13, элемент ИЛИ 14, элементы 15-19 памяти, элемент НЕ 20.

Регистр 1 сдвига выполнен четырехразрядным. Элементы 15-19 памяти реализо- ваны на D-триггерах.

. Устройство работает следующим обра- : зом. -. - ,4...-, , ..-.. .-. .-:......... . ..

На информационный вход регистра 1 сдвига поступает кодируемая информация виде сигнала NRZ (фиг. 2а), привязанная к сйнхросерйи в, получаемой после деления удвоенной частоты (фиг, 26) на два делителем 2 частоты,

Период сйнхросерйи в равен тактовому интервалу информации NRZ. Регистр 1 сдвига выполняет промежуточное хранение информации на длительность тактового интервала...., .

Сдвиг информации осуществляется по переднему фронту синхронизации в делителя 2 частоты.

.. . Информация с выходов регистра 1 Сдвига (фиг. 2г, д, е, ж) поступает на входы элементов И 3-6. Элемент И 3 предназначен для обнаружения кодовой группы 10, элементы И4-для обнаружения кодовой груп- пы 11, элементы И 5 и 12 - для обнаружения кодовой группы 0011, а злементы И 6 и 13 - для обнаружения ко- довой группы 000 (соответственно фиг. 2з, и, м, о).

Сигнал на выходе элемента ИЛИ 9 (фиг. 2к) является результатом сборки сигналов з ии. Кик только обнаруживается группа 10 .или 11 (сигнал к), устанавливается в 1 элемент.16 памяти, запрещая через элемент НЕ 20 на. тактовый интервал информации NRZ на элементы Й3-6(фиг. 2л).

Элемент 17 памяти формирует си гнал н, который вместе с Сигналом з с выхода элемента ИЗ и сигналом о с выхода элемента И 13 собирается на элементе ИЛИ 7 (фиг, 2с), обозначая нечетные такты выходного кода RLL, а элемент 19 памяти формирует

сигнал п, который собирается на элементе ИЛИ 8 с сигналом И элемента И 4 (фиг., 2т), обозначая четные такты выходного кода RLL (см,правило преобразования кода NRZ в RLL 2,7; отсчет слева). Элементы И 10 и 11 и элемент ИЛИ 14 выполняют функции коммутатора четных и нечетных тактов (фиг. 2у). Коммутация выполняется по сигналу в с выхода делителя 2 частоты.

Элемент 15 памяти формирует выходной сигнал ф, соответствующий коду RLL.

Элементы 18 и 19 памяти в совокупности (сигналы п и.р) выполняют запрет элементов И 12 и 13 на время двух тактовых интервалов информации RLL

Упрощение предлагаемого устройства достигается за счет совмещения функций преобразования кода и управления счетом длины группы.

Форм у.лаизобре.тения Устройство для кодирования цифровой информации, содержащее регистр сдвига, информационный вход которого является информационным входом устройства, делитель частоты, вход которого объединен с входом синхронизации первого элемента памяти и является входом синхронизации устройства, второй - пятый элементы памяти, входы синхронизации которых объединены, первый - восьмой злементы И, первый - четвертый элементы ИЛИ и элемент НЕ, первый выход регистра сдвига подключен к первым инверсным входом третьего и четвертого элементов И и к первым прямым входам первого И второго элементов И, выходы которых соединены с первыми входами соответственно первого и третьего элементов ИЛИ, второй выход регистра сдвига подключен к инверсному входу первого, второму прямому входу второго и вторым инверсным входам третьего и четвертого элементов И, третий выход регистра сдвига соединен с первым прямым входом третьего и третьим инверсным входом четвертого элементов И, четвертый выход регистре сдвига подключен к второму прямому входу третьего элемента И, второй прямой вход которого объединён с вторым прямым входом первого, третьим прямым входом второго и прямым входом четвёртого элементов И, выход делителя частоты подключен к входу синхронизации регистра сдвига и к первому прямому входу пятого и инверсному входу шестого элементов И, выходы которых соединены с входами четвертого элемелта ИЛИ, первые инверсные входы седьмого и восьмого элементов И объединены, выход пятого элемента памяти подключен к информационному входу четвертого

элемента памяти, выход первого элемента памяти является выходом устройства, отличающееся тем, что, с целью упрощения устройства, второй вход третьего элемента ИЛИ подключен к выходу первого элемента И, выход третьего элемента ИЛИ подключен к информационному входу второго элемента памяти, выход которого через элемент НЕ соединен с прямым входом четвертого элемента И, первый вход второго элемента ИЛИ подключен к выходу второго элемента И, выходы первого и второго элементов ИЛИ соединены соответственно с вторым прямым входом пятого и прямым входом шестого элементов И, второй вход второго элемента ИЛИ объединен с вторыми инверсными входами седьмого и восьмого элементов И и подключен к выхо0

ду пятого элемента памяти, вход синхронизации которого подключен к выходу делителя частоты, выходы третьего и четвертого элементов И соединены с прямыми входами соответственно седьмого и восьмого элементов И, выход четвертого элемента памяти подключен к первому инверсному входу седьмого элемента И, выход которого соединен с информационным входом третьего элемента памяти, выход которого подключен к второму входу первого элемента ИЛИ, выход восьмого элемента И соединен с информационным входом пятого элемента памяти и третьим входом первого элемента ИЛИ, выход четвертого элемента ИЛИ подключен к информационному входу первого элемента памяти..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования цифровой информации | 1991 |

|

SU1791960A1 |

| УСТРОЙСТВО БУФЕРИЗАЦИИ И СИНХРОНИЗАЦИИ ДЛЯ ОБРАБОТКИ НЕПРЕРЫВНОГО СИГНАЛА | 1990 |

|

SU1812885A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1354232A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ КОДОВЫХ СЛОВАРЕЙ НЕЛИНЕЙНЫХ РЕКУРРЕНТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2009 |

|

RU2439657C2 |

| Устройство для выдачи команд об изменении движения транспорта | 1986 |

|

SU1446640A1 |

Изобретение относится к вычислительной технике/Его использование в аппаратуре для магнитной записи цифровой информации позволяет упростить устройство, содержащее регистр 1 сдвига, делитель 2 частоты, элементы И 3-6, 10-13, элементы ИЛИ 7-9, 14, элементы 15-19 памяти и элемент НЕ 20. Цель достигается благодаря совмещению функций преобразования кода NRZ в код RLL 2,7 и управлению счетом длины кодовой группы. 2 ил.

Редактор Т.Юркова

Составитель И.Журавлев Тех ре д М, М о р ген та л

Фиг.Е

Корректор Н.Ревская

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3689899, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-04-07—Публикация

1990-11-16—Подача