11

Изобретение относится к вычислительной технике и предназначено для использования во входных цепях систем сбора и обработки информации.

Цель изобретения - расширение области применения устройства за счет приема различных видов последовательного кода.

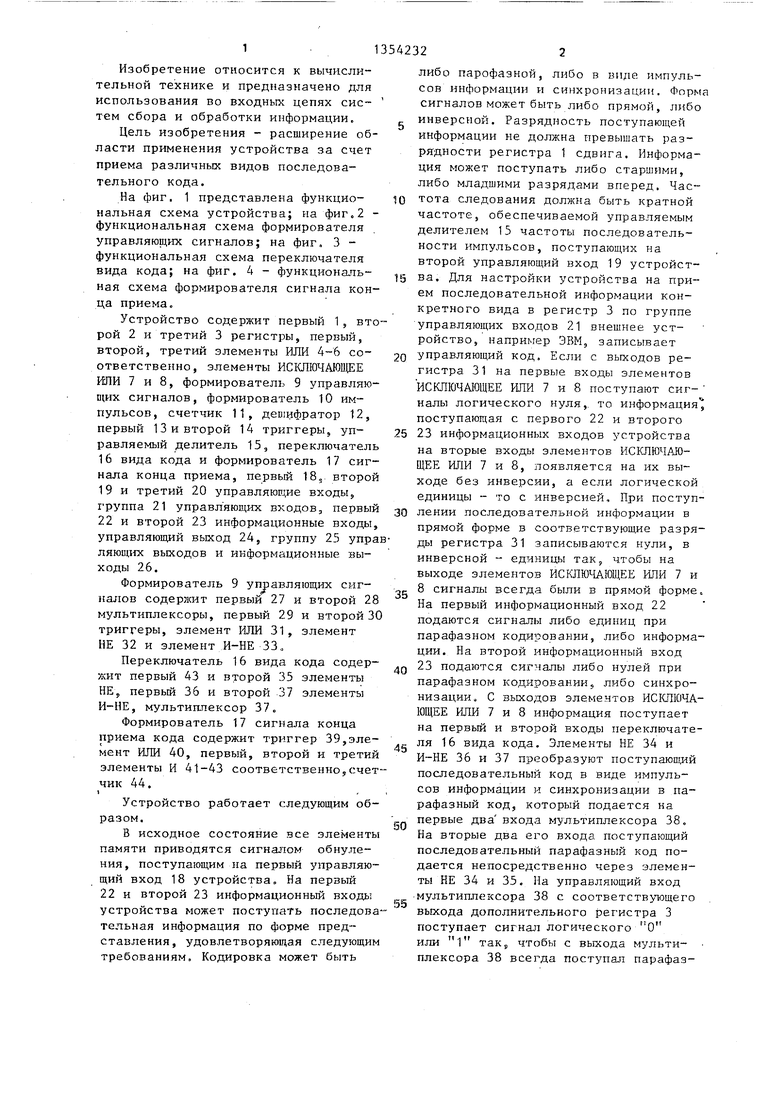

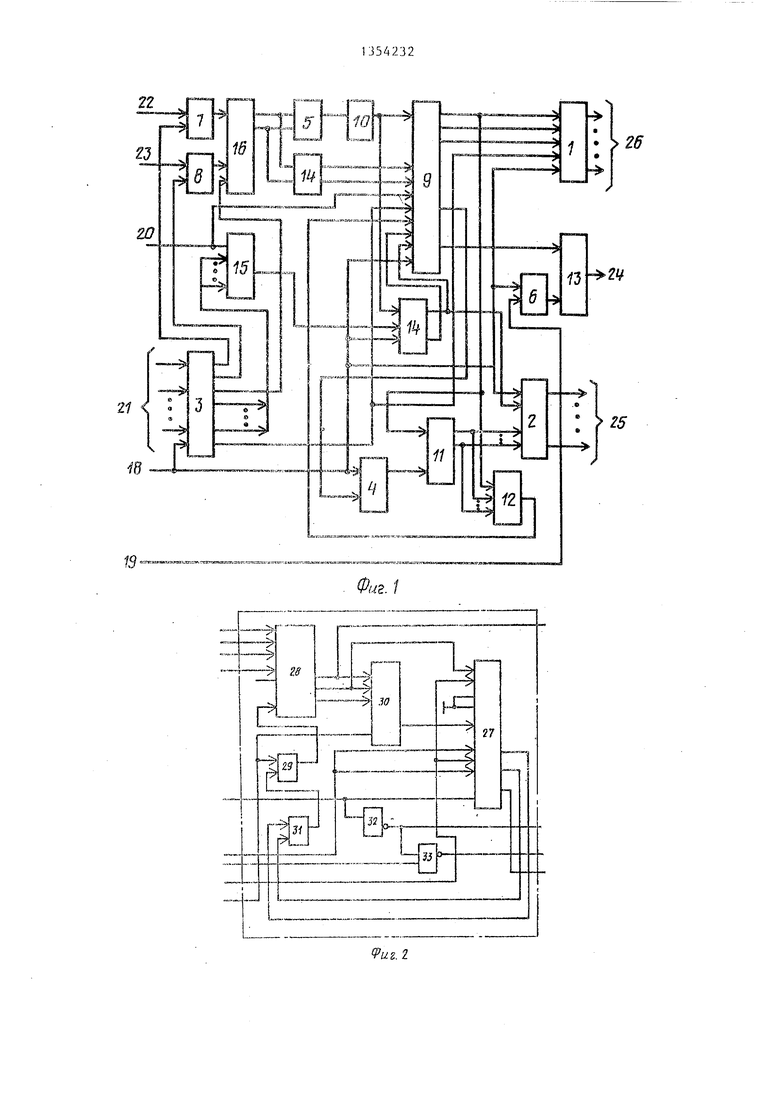

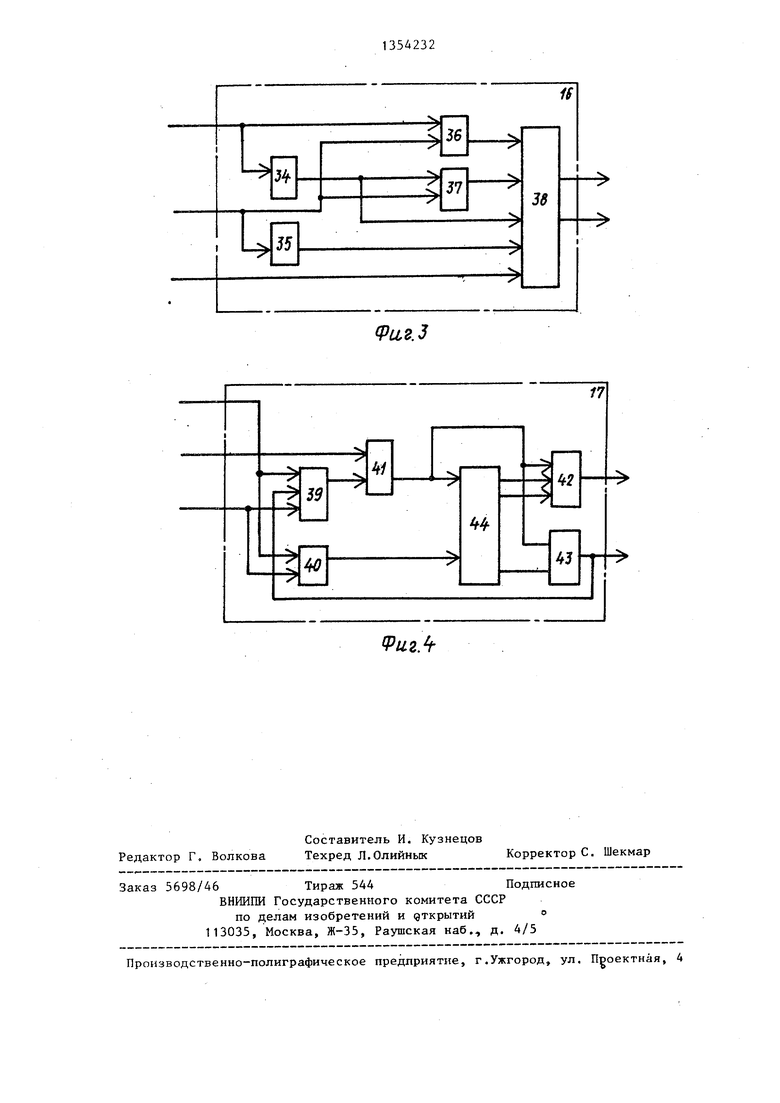

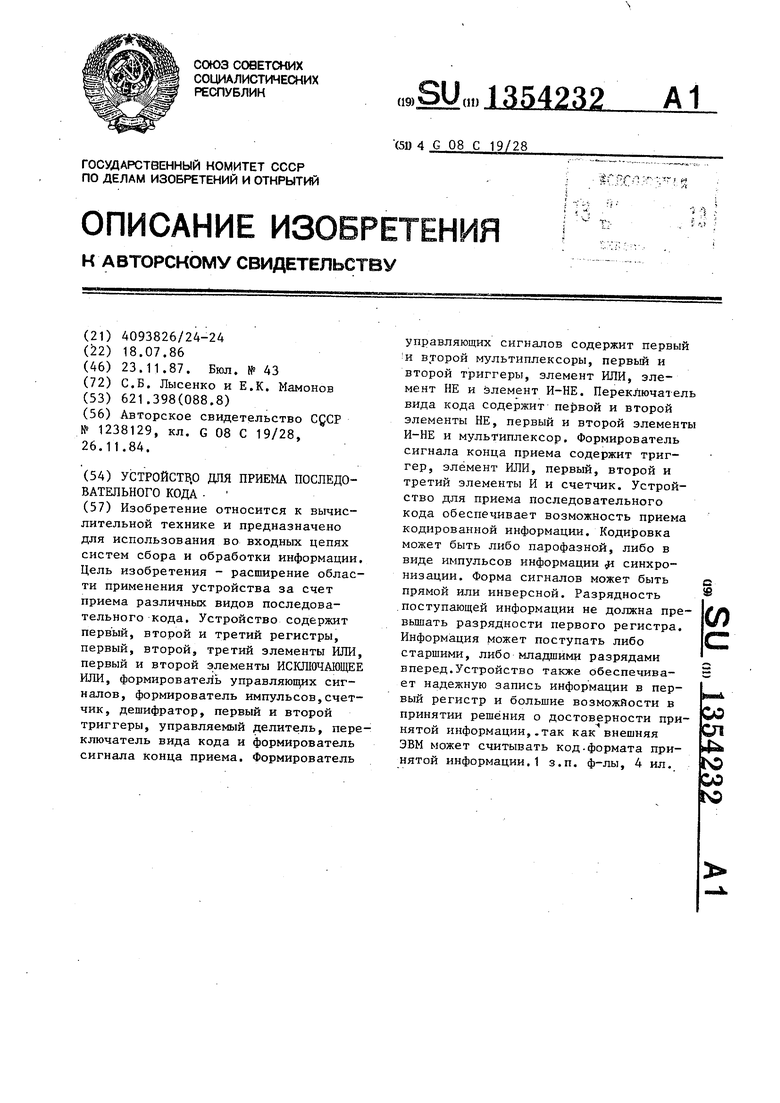

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - функциональная схема формирователя управляющих сигналов; на фиг, 3 - функциональная схема переключателя вида кода; на фиг, 4 - функциональная схема формирователя сигнала конца приема.

Устройство содержит первый 1, второй 2 и третий 3 регистры, первый, второй, третий элементы ИЛИ 4-6 соответственно, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и 8, формирователь 9 управляго- DiHX сигналов, формирователь 10 импульсов, счетчик 11, дешифратор 12, первый 13 и второй 14 триггеры, управляемый делитель 15, переключатель 16 вида кода и формирователь 17 сигнала конца приема, первый 18, второй 19 и третий 20 управляюпдие входы, группа 21 управляющих входов, первый 22 и второй 23 информационные входы, управляющий выход 24, группу 25 упра ляющих выходов и информационные выходы 26.

Формирователь 9 управляющих сиг

налов содержит первый 27 и второй 28 мультиплексоры, первый 29 и второй 3 триггеры, элемент ИЛИ 31, элемент НЕ 32 и элемент И-НЕ 33 о

Переключатель 16 вида кода содержит первый 43 и вт орой 35 элементы HEj, первый 36 и второй 37 элементы И-НЕ, мультиплексор 37,

Формирователь 17 сигнала конца приема кода содержит триггер 39,элемент ИЛИ 40, первый, второй и третий элементы И 41-43 соответственно,счетчик 44.

1

Устройство работает следующим образом.

В исходное состояние все элементы памяти приводятся сигналом обнуления, поступающим на первый управляющий вход 18 устройства На первый 22 и второй 23 информационный входы устройства может поступать последовтельная информация по форме представления, удовлетворяющая следующи требованиям. Кодировка может быть

0

5

0

либо парофазной, либо в виде импульсов информации и синхронизации. Форма сигналов может быть либо прямой, либо инверсной. Разрядность поступающей информации не должна превышать разрядности регистра 1 сдвига. Информация может поступать либо старшими, либо младшими разрядами вперед. Частота следования должна быть кратной частоте, обеспечиваемой управляемым делителем 15 частоты последовательности импульсов, поступающих на второй управляющий вход 19 устройства. Для настройки устройства на прием последовательной информации конкретного вида Б регистр 3 по группе управляющих входов 21 внешнее устройство, например ЭВМ, записывает управляющий код. Если с выходов регистра 31 на первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и 8 поступают сиг- налы логического нуля,, то информация поступающая с первого 22 и второго 5 2,3 информационных входов устройства на вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и 8, появляется на их выходе без инверсии, а если логической единицы - то с инверсией. При поступлении последовательной информации в прямой форме в соответствующие разряды регистра 31 записываются нули, в инверсной - едмницы так, чтобы на выходе элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и 8 сигналы всегда были в прямой форме. На первый информационный вход 22 подаются сигналы либо единиц при парафазном кодировании, либо информации. На второй информационный вход 23 подаются сигналы либо нулей при парафазном кодировании, либо синхронизации. С выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7 и 8 информация поступает на первый и второй входы переключателя 16 вида кода. Элементы НЕ 34 и И-НЕ 36 и 37 преобразуют поступаюпщй последовательный код в виде импульсов информации и синхронизации в па- рафазный код, который подается на первые два входа мультиплексора 38. На вторые два его входа поступающий последовательный парафазный код подается непосредственно через элементы НЕ 34 и 35. На управляющий вход Мультиплексора 38 с соответствующего выхода дополнительного регистра 3 поступает сигнал логитгеского О или 1 таКр чтобы с выхода мультиплексора 38 всегда поступал парафаз30

35

40

45

50

55

ный код. На входе второго элемента ИЛИ 5 из импульсов единиц и нулей парафазного кода формируются импульсы синхронизации, по заднему фронту которых формирователь 10 импульсов вы- рабатывает импульсы фиксированной длительности. На выходах RS-триггера 14 из импульсов единиц и нулей пара- фазного кода формируются прямой и инверсный сигналы информации, причем импульсы синхронизации с выхода формирователя 10 импульсов по времени всегда расположены в середине импульсов информации, что гарантирует надежную запись в регистр 1 сдвига.

Формирователь 9 управлякяцих сигна лов производит необходимую коммутаци сигналов при настройке устройства на прием кода младшими или старшими раз рядами вперед. На пятый вход мульти- f5 плекс бра 27 и на вход элемента НЕ 32 с соответствующего выхода регистра 3 поступает сигнал логического О при приеме старшими разрядами вперед или логической 1

С выхода формирователя 10 импульсов сигналы синхронизации входного кода поступают на вход установки в

единичное состояние триггера 39 и на 20 разрядами вперед. При приеме старши- первый вход элемента ИЛИ 40 формиро- ми разрядами вперед сигналы информапри приеме младшими

вателя сигнала конца приема. Триггер 39 устанавливается в единичное состояние и разрешает прохождение импульсов тактовой частоты с выхода управляемого делителя 15 частоты последовательности импульсов через элемент И 41 на вход синхронизации счетчика 44 и на стробирующие входы дешифраторов на элементах И 42, 43. Через элемент ИЛИ 40 импульсы синхронизации входного кода поступают на вход обнуления счетчика 44, периодически устанавливая его в исходное состояние. На группу управляющих входов управляемого делителя 15 частоты последовательности импульсов с выхода регистра 31 поступает код, в соответствии с которым поступающая с входа 20 опорная частота делителя до значе

ния, в два раза превышающего, частоту синхронизации входного кода. При этом за время периода частоты синхронизации входного кода счетчик 44 не успевает сосчитать количество импульсов тактовой частоты, устанавливаемое дешифраторами на элементах И 40 и 43. После прихода последнего разряда входного кода периодическое обнуление счетчика 44 прекращается. На выходе элемента И 42 формируется импульс, поступающий на третий вход формирователя 9 управляющих сигналов и на второй вход синхронизации регистра 2, записывая в него код числа принятых разрядов с выхода счетчика 11. После этого на выходе элемента И 43 формируется импульс конца прие- ма, поступающий на шестой вход форми

рователя 9 управляющих сигналов, по заднему фронту которого обнуляется триггер 29, запрещая прохождение импульсов тактовой частоты через элемент И 41 на вход синхронизации счетчика 44. Схема устанавливается в исходное состояние с приходом первого импульса синхронизации следующей кодовой посылки.

Формирователь 9 управлякяцих сигналов производит необходимую коммутацию сигналов при настройке устройства на прием кода младшими или старшими разрядами вперед. На пятый вход мульти- плекс бра 27 и на вход элемента НЕ 32 с соответствующего выхода регистра 3 поступает сигнал логического О при приеме старшими разрядами вперед или логической 1

при приеме младшими

Q

ции на первый выход мультиплексора поступают с его шестого входа, а сигнал с первого выхода формирователя

5 17 импульса конца приема, поступая на третий и четвертый входы мультиплексора 27, появляется на пятом выходе формирователя 9 управляющих сигналов и устанавливает триггер 3 в

0

единичное состояние.

С выхода 24 устройства во внешнюю ЭВМ поступает сигнал Принято, который может быть снят выдачей импульса на вход 18 устройства. Импульс,

с снимаемый со второго выхода формирователя 17 импульса конца приема,проходит через элемент И-НЕ 33, на н.то- ром входе которого при этом присутствует сигнал логической 1 с выхода элеме нта КЕ 32, проходит через второй элемент ИЛИ 4 и сбрасывает счетчик 11, Подготавливая его к новому циклу приема. При приеме старшими разрядами вперед разряды информации

в конце приема попадают в соответствующие разряды регистра 1 сдвига и никакой дополнительной обработки информации не требуется. При приеме младшими разрядами вперед, если коQ личество принятых разрядов меньше разрядности регистра 1 сдвига, необходимо дополнительно сдвинуть принятую информацию до младшего разряда регистра 1 сдвига. Для этого при наf личии сигнала логической единицы на пятом входе формирователя Т9 управляющих с,игналов импульс с первого выхода формирователя 17 сигнала конца приема через третий и четвертый входы

и второй вьгход мультиплексора 27 и элемент Ш1И 32 поступает на второй вход триггера 29, устанавливая его в единичное состояние. Под действием сигнала с выхода триггера 29 мультиплексор 28 подключает к своему первому выходу сигнал опорной частоты с входа 20 устройства, которая, поступая на входы синхронизации регистра 1 сдвига и счетчика 11,сдвигает информацию до младшего разряда регистра 1 сдвига. При установке всех разрядов счетчика 11 в состояние логической единицы на выходе дешифратора 12 появляется импульс, поступающий на первый и второй вход1з1 мультиплексора 27 и появляющийся на его третьем и четвертом выходах. Импульс с Т1: етьего выхода через элемент ИЛИ 31 устанавливает триггер 29 в нулевое состояние по его второму входу, а импульс с четвертого выхода устанавливает триггер 13 в единичное состояние, формируя сигнал Принято.Приче число дополнительных импульсов на единицу больше, чем нужно для сдвига информации в регистре 1 сдвига до младшего разряда., что объясняется необходимостью сохранения длитель- ности последнего импульса, синхронизации, устанавливающего счетчик 11 в нулевое состояние. В этом случае необходимо сигнал информации задержать на один такт. Для этого между мультиплексорами 27 и 29 в цепь сигнала информации включен второй триггер 30, сигнал с выхода которого через седьмой вход и первый выход мультиплексора 27 поступает на третий вход регистра 1 сдвига. Сигнал с выхода элемента НЕ 32, поступающий на четвертый вход регистра 1 сдвига, обеспечивает переключение его на

режимы сдвига в сторону старших или

младших разрядов.

Считав сигнал Принято с выхода 24 устройства, внешняя ЭВМ с группы управляющих выходов 25 устройства считывает код формата принятого информационного слова, а с выходов 26 информацию.

Предлагаемое устройство для прием последовательного кода обеспечивает возможность приема различных видов последовательного кода надежную информацию в регистр сдвига и большие возможности в принятии решения о до товарности принятой информации, так

о Q

..

о

5

как внешняя ЭВМ может считывать код формата принятой информации.

Формула изобретения

1. Устройство для приема последовательного кода, содержащее первый регистр, выходы которого являются информационными выходами устройства, первые входы первого и второго регистров, первого элемента ИЛИ и формирователя сигнала конца приема объединены и являются первым управляющим входом устройства, выход первого элемента ИЛИ подключен к первому входу счетчика, выходы которого подключены к входам, объединенным в группу, дешифратора, второй элемент ИЛИ, выход которого подключен к формирователю импульсов, отличающееся тем, что, с целью расширения области применения за счет приема различных видов последовательного кода, в него введены третий регистр, третий элемент ИЛИ, первый и второй элементы ИСКПЮЧАНИЦЕЕ ИЛИ, формирователь управляющих сигналов, первый и второй триггеры, управляемый делитель, переключатель вида кода, формирователь сигнала конца приема, первые входы, третьего элемента ИЛИ, третьего регистра и формирователя управляющих сигналов объединены и являются первым управляющим входом устройства, второй вход третьего элемента ИЛИ является вторым управляющим входом устройства, выход третьего элемента ИЛИ подключен к первому входу первого триггера, первый вьгход формирователя управляющих сигналов подключен к- второму входу первого элемента ИЛИ, второй выход формирователя управляющих сигналов подк.шочен к вторым входам первого регистра, счетчика и к входу дешифратора, выход которого подключен к второму входу формирователя управляющих сигналов, третий и четвертый выходы которого подключены к третьему и четве ртому входам первого регистра, пятый выход формирователя управляющих сигналов подключен к второму входу первого триггера, выход которого является управляющим выходом устройства, выходы счетчика подключены к входам, объединенным в группу, второго регистра, выходы которого являются группой управляющих выходов устройства, первый выход фор

мирователя сигнала конца приема подключен к второму входу второго регистра и к третьему входу формировател управляющих сигналов, первый и второ выходы третьего регистра подключены к первь1м входам первого и второго элементов ИСКЛЮЧАЩЕЕ ИЛИ соответственно, вторые входы последних являются первым и вторым информационными входами устройства соответственно, выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подк.пючены к первому и второму входам переключателя вида кода соответственно, третий выход третьего регистра подключен к третьему входу переключателя вида кода, первый и второй выходы которого подключены к первым и вторым входам вторьтх элементов ИЛИ и триггера соответственно, выход формирователя импульсов подключен к второму входу формирователя сигнала конца приема и к четвертому входу формирователя управляющих сигналов, четвертый выход третьего регистра подключен к пятым входам первого регистра и формирователя управляющих сигналов, выходы группы третьего регистра подключены к входам группы управляемого делителя, выход которого подключен- к третьему входу формирователя сигнала конца приема, второй выход которого подключен к шестому входу формирователя управляющих сигналов, вход управляемого делителя и седьмой вход формирователя управляющих сигналов объединены и являются третьим управляющим входом устройства, входы группы третьего регистра являются управляющими входами, объединенными в группу, устройства, первый и второй выходы второго триггера подключены .к восьмому и девятому входам формирователя управляющих сигналов.

2. Устройство по П.1, отличающееся тем, что формирователь управляющих сигналов содержит первый и второй мультиплексоры,первы

O

5

0

5

и второй триггеры, элемент ИЛИ,элемент НЕ и элемент И-НЕ, первые входы первого и второго триггеров объединены и являются первым входом формирователя, первый и второй входы первого мультиплексора объединены и являются вторым входом формирователя, третий и четвертый входы первого мультиплексора объединены и являются третьим входом формирователя, первый вход второго мультиплексора является четвертым входом формирователя, вход элемента НЕ и пятый вход первого мультиплексора объединены и являются пятым входом формирователя, первый вход элемента И-НЕ является шестым входом формирователя, второй, третий и четвертый входы второго мультиплексора являются седьмым, восьмым и девятым входами формирователя, выход элемента И-НЕ является первым выходом формирователя, первый выход второго мультиплексора и второй вход второго триггера объединены и являются вторым 5 выходом формирователя, второй выход д второго мультиплексора и третий вход второго триггера объединены и подключены к шестому входу первого мультиплексора, первый выход которого явля- 0 ется третьим выхрдом формирователя, третий выход второго мультиплексора подключен к четвертому входу второго триггера, выход которого подключен к седьмому входу первого мультиплексора, второй выход которого подключен к первому входу элемента ИЛИ, восьмой и девятый входы первого мультиплексора объединены и подключены к нулевой шине, третий выход первого мультиплексора подключен к второму входу элемента ИЛИ, выход которого подключен к второму входу первого триггера,выход которого подключен к пятому входу второго мультиплексора, выход элемен- 5 та НЕ объединен с вторым входом элемента И-НЕ и является четвертым выходом формирователя, четвертый выход первого мультиплексора является пятым выходом формирователя.

0

7P

OSKEUerJ

&

20

r;

e

L

5

.,„ „,„

Л

г

1

f

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для контроля | 1985 |

|

SU1293739A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для отображения информации на экране цветного телевизионного индикатора | 1985 |

|

SU1363296A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1427564A1 |

Изобретение относится к вычислительной технике и предназначено для использования во входных цепях систем сбора и обработки информации. Цель изобретения - расширение области применения устройства за счет приема различных видов последовательного кода. Устройство содержит первый, второй и третий регистры, первый, второй, третий элементы ИЛИ, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, формирователь управляюпщх сигналов, формирователь импульсов,счетчик, дешифратор, первый и второй триггеры, управляемый делитель, переключатель вида кода и формирователь сигнала конца приема. Формирователь управляющих сигналов содержит первый и второй мультиплексоры, первый и второй триггеры, элемент ИЛИ, элемент НЕ и элемент И-НЕ. Переключатель вида кода содержит первой и второй элементы НЕ, первый и второй элементы И-НЕ и мультиплексор. Формирователь сигнала конца приема содержит триггер, элемент ИЛИ, первый, второй и третий элементы И и счетчик. Устройство для приема последовательного кода обеспечивает возможность приема кодированной информации. Кодировка может быть либо парофазной, либо в виде импульсов информации синхронизации. Форма сигналов может быть прямой или инверсной. Разрядность .поступающей информации не должна превышать разрядности первого регистра. Информация может поступать либо старшими, либо младшими разрядами вперед.Устройство также обеспечивает надежную запись информации в первый регистр и большие возможйости в принятии решения о достоверности принятой информации,.так как внешняя ЭВМ может считывать код-формата принятой информации.1 з.п. ф-лы, 4 ил. (Л

21

™

25

11

J

-ЭД

18

К.......

,.

Фиг. 1

Составитель И. Кузнецов Редактор Г, Волкова Техред Л.Олийнык Корректоре. Шекмар

Заказ 5698/46 Тираж 544Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий ° 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

fPu2.3

Vuz.

| Устройство для приема последовательного кода | 1984 |

|

SU1238129A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1987-11-23—Публикация

1986-07-18—Подача