Щ-

(Л

с

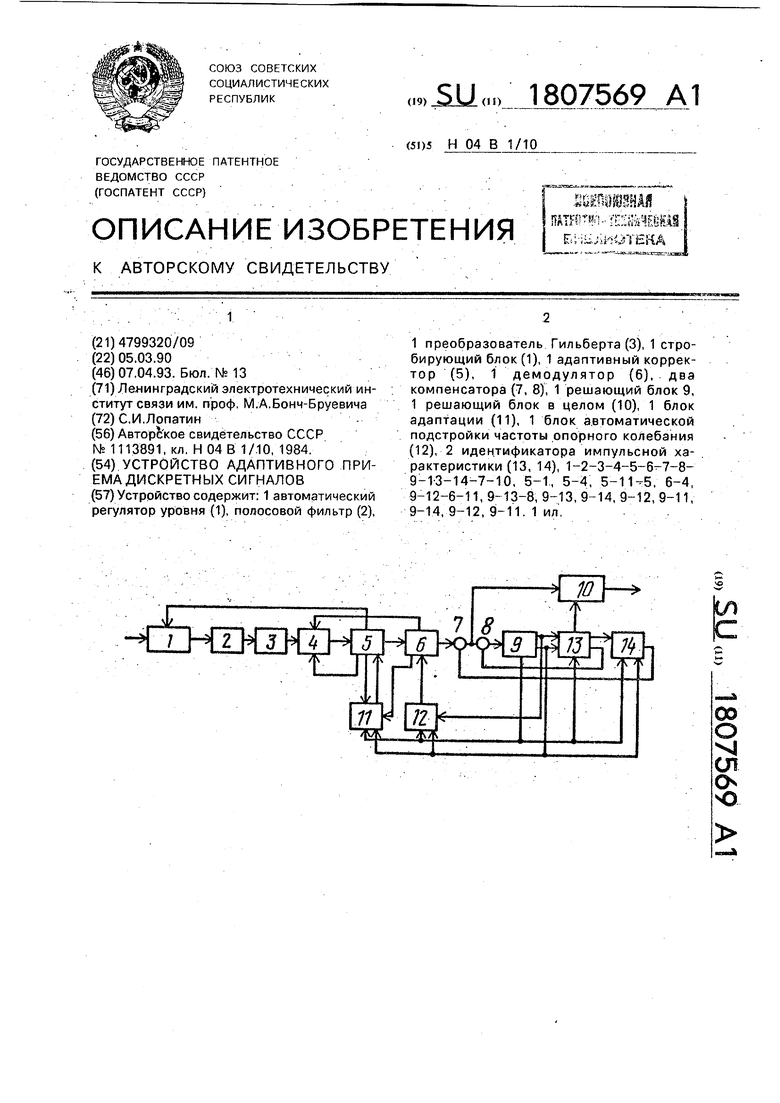

Изобретение относится к электросвязи.

Цель изобретения - повышения помехоустойчивости приема при произвольных искажениях амплитудно-частотной характеристики канала связи.

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство содержит автоматический регулятор уровня 1,.полосовой фильтр 2, преобразователь 3 Гильберта, стробирую- щий блок 4, адаптивный корректор 5, демодулятор б, первый, второй компенсаторы 7, 8 импульсной характеристики, решающий блок 9, решающий блок 10 в целом, блок 11 адаптации, блок 12 автоматической подстройки частот опорного колебания, первый, второй идентификаторы 13, 14 импульсной характеристики. . Устройство работает следующим обра-

ЗОМ. ....

Принятый сигнал поступает на вход автоматического регулятора уровня 1 принимаемого сигнала, который обеспечивает нормальное функционирование устройства при изменении уровня входного сигнала в определенных пределах. Далее сигнал поступает на вход полосового фильтра 2, обеспечивающего подавление внеполосного аддитивного шума. С выхода полосового фильтра 2 сигнал подается на вход преобразователя 3 Гильберта, в котором образуются квадратурный и синфазный каналы, Сигналы синфазного и квадратурного подканалов стробируют и преобразуют в цифровую фор- му в стробирующем блоке 4. Стробирующмй блок 4 выполнен в виде аналого-цифрового преобразователя. Далее сигнал подвергается коррекции в адаптивном корректоре 5, который представляет из себя адаптивный нерекурсивный фильтр, настраиваемый по критерию минимума среднеквадратической ошибки. Он реализован на линии задержки с отводами, расположенными через интервалы, равные Т/2 (Т-единичный интервал). Регуляторы адаптивного корректора выполнены на умножителях.

Сигналы с выходов регуляторов а дапти НогоЧсорректора 5 объединяются в сумматоре корректора и поступают для дальнейшей обработки в демодулятор 6. В демодуляторе б осуществляется перенос принятого сигнала в полосу частот эквивалентного низкочастотного канала и компенсируются искажения, обусловленные расхождением частот и фаз несущего и опорного колебаний, а также качанием фазы несущего коле- бания (фазовым джиттером). Для этого подстраивают фазу опорного колебания в соответствии с выражением

Р + 1 /) + (Р ft - 1 + Al. Ir

ef aj + A2 m ef- 1 -a)- 1

0)

где р - оценка фазы несущего колебания на j-рм такте,.

Јj - отсчёт сигнала на первом выходе решающего блока 9,

AI, Да - весовые коэффициенты,

lm(.) - мнимая составляющая комплексной функции,.

ej - ошибка оценки информационного параметра в решающем блоке 9.

Данное выражение описывает работу цифровой системы фазовой автоподстройки частоты второго порядка.

С выхода блока демодуляции б принятый сигнал поступает в компенсатор 7, в котором производится компенсация каузальной мёжсимвольной интерференции .без первых 3-4 отсчетов в соответствии с выражением

Zj yj-2 йп-м -qj-n .4 (2)

п - М.

где {qj} - коэффициенты второго идентификатора 14,

yj - отсчет сигнала на выходе демодулятора б.;

; С выхода компенсатора 7 сигнал поступает в решающий блок 10, где производится оценка и вынесение решения о принятом сигнале по критерию максимального правдоподобия. Также сигнал с выхода компенсатора 7 поступает на первый вход компенсатора 8, в котором производится компенсация первых 3-4 отсчетов импульсной характеристики канала связи, исключая первый, в соответствии с выражением

.. м - 1 л -.-. П Zi - X an qi - п (3)

: п - 2 ....

В результате этой операции на входе решающего блока 9 имеется сигнал, зависящий лишь от информационных параметров, что позволяет обеспечить требуемую помехоустойчивость решающего блока, не зависящую от амплитудно-частотных характеристик канала. .

В решающем блоке 9 сигнал сравнива-. ется с эталонными значениями передаваемого сигнала. Принятому сигналу сопоставляется наиболее близкий ему эталонный сигнал, который далее поступает на выход блока 9. Этот процесс эквивалентен сопоставлению хаждому принятому сигналу

соответствующего переданного символа, поскольку на передающей стороне имеется однозначное соответствие передаваемого сигнала информационному параметру. Решающий блок выполнен в виде программируемого постоянного запоминающего устройства. Такая реализация решающего блока 9 позволяет здесь же осуществлять вычисление сигнала ошибки, необходимого для подстройки фазы опорного колебания, а также, коэффициентов адаптивного корректора .5 и идентификаторов 13, 14 импульсной характеристики, и сигнал запрета постройки адаптивных блоков в случае, когда разность между сигналами на его входе и выходе становится меньше наперед заданного порога, определяемого требуемой остаточной среднеквадратической ошибкой

С выхода решающего блока 9 сигнал поступает на вход идентификатора 13 импульсной характеристики, а с его второго выхода на вход второго идентификатора 14 импульсной характеристики. Идентификаторы импульсной характеристики 13 и 14 в совокупности с решающим блоком 9 образуют систему адаптивной идентификации импульсной характеристики канала связи. Сигнал на выходе решающего блока 10 появляется со значительной задержкой (5-10 единичных интервалов) и его нецелесообразно использовать для управления адаптивным корректором 5, блоком 12, идентификаторами 13,и 14, так как при этом невозможно оперативно отслеживать изменение частотных характеристик канала,ча- стоты, фазы и дрожания фазы несущего колебания. В то же время поэлементно вынесенное решение о принятом информационном параметре в решающем блоке 9 содержит достаточную статистику для подстройки адаптивных систем устройства даже при весьма значительных линейных искажениях канала связи. Так.удовлетворительная подстройка адаптивных блоков 5, 13 и 14,12 возможна при вероятности ошибки в решающем блоке 9 порядка .

Компенсаторы реализуются на операционных усилителях в режиме включения суммирования.

Вычисленный в решающем блоке 9 сигнал запрета на подстройку адаптивных блоков снимается с его выхода и подается на соответствующие входы блока 12, блока 11 адаптации, идентификаторов 13,14 импульсной характеристики,соответственно,

Формулаизобретенйя

Устройство адаптивного приема дискретных сигналов, содержащее последовательно соединенные автоматический регулятор уровня, полосовой фильтр, преобразователь Гильберта, стробирующий блок, адаптивный корректор, демодулятор и блок 5 адаптации, выход которого соединен с вторым входом адаптивного корректора, второй, третий и четвертый выходы которого соединены соответственно с входом автоматического регулятора уровня, вторым вхо0 дом стробирующего блок и вторым входом блока адаптации, третий вход стробирую- . щего блока соединен с первым выходом демодулятора, второй вход которого соединен с выходом блока фазовой автоподстройки

5 частоты опорного колебания,-а также решающий блок, первый выход которого соединен с первыми входами первого идентификатора импульсной характеристики и блока фазовой автоподстройки частоты

0 опорного колебания, второй вход которого и второй вход первого идентификатора им- . пульсной характеристики соединены с вторым выходом решающего блока, третий выход которого соединен с третьим входом

5 блока фазовой автоподстройки частоты опорного колебания, первый выход первого идентификатора импульсной характеристи- . ки соединен с первым входом решающего блока в целом, о т л и ч а ю.щ е е с я тем, что, с целью повышения помехоустойчивости

0 приема при произвольных искажениях амп- литудногчастотной характеристики канала связи, введены первый, второй компенсаторы импульсной характеристики и второй идентификатор импульсной характеристи5 ки, причем второй выход демодулятора соединен с первым входом первого компенсатора импульсной характеристики, выход которого соединен с вторым входом решающего блока в целом и первым

0 входом второго компенсатора импульсной характеристики, выход и второй вход которого соединены соответственно с входом решающего блока и вторым выходом первого идентификатора импульсной характери5 стики, второй выход которого соединен с первым входом второго идентификатора импульсной характеристики, выход которого соединен с вторым входом первого компенсатора импульсной характеристики,

0 третий выход решающего блока соединен с третьим входом первого, вторым входом . второго идентификатора импульсной характеристики и третьим входим блока адаптации, четвертый вход которого и третий вход

5 второго идентификатора импульсной характеристики соединены с вторым выходом ре- . шающего блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приема дискретных сигналов с относительно-фазовой модуляцией низкой кратности | 1987 |

|

SU1467786A1 |

| Устройство для адаптивного приема цифровых однополосных сигналов | 1989 |

|

SU1663776A2 |

| Устройство для адаптивного приема дискретных сигналов | 1982 |

|

SU1083396A1 |

| Устройство адаптивного приема дискретных сигналов с амплитудно-фазовой модуляцией | 1986 |

|

SU1309319A1 |

| Устройство адаптивной обработки дискретных сигналов | 1982 |

|

SU1116542A2 |

| Устройство адаптивного приема дискретных сигналов | 1982 |

|

SU1113891A1 |

| Устройство для преобразования сигналов | 1984 |

|

SU1234991A1 |

| Устройство преобразования сигналов для передачи данных по первичному сетевому тракту | 1989 |

|

SU1739503A1 |

| Корректор с автоматической настройкой групповых трактов системы многоканальной связи | 1977 |

|

SU734885A1 |

| ЦИФРОВОЙ ПРИЕМНИК ДИСКРЕТНЫХ СИГНАЛОВ С "ВРАЩАЮЩЕЙСЯ ФАЗОЙ" | 1991 |

|

RU2038703C1 |

Устройство содержит: 1 автоматический регулятор уровня (1), полосовой фильтр (2), 1 преобразователь Гильберта (3), 1 стро- бирующий блок(1), 1 адаптивный корректор (5), 1 демодулятор (6), два компенсатора (7, 8), 1 решающий блок 9, 1 решающий блок в целом (10), 1 блок адаптации (11), 1 блок автоматической подстройки частоты опорного колебания

| Устройство адаптивного приема дискретных сигналов | 1982 |

|

SU1113891A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-04-07—Публикация

1990-03-05—Подача