Изобретение относится к импульсной технике и может быть использовано в радиолокации и связи.

Целью изобретения является повышение надежности за счет исключения сбоев, возникающих при обращении к последним ячейкам блока памяти и упрощение.

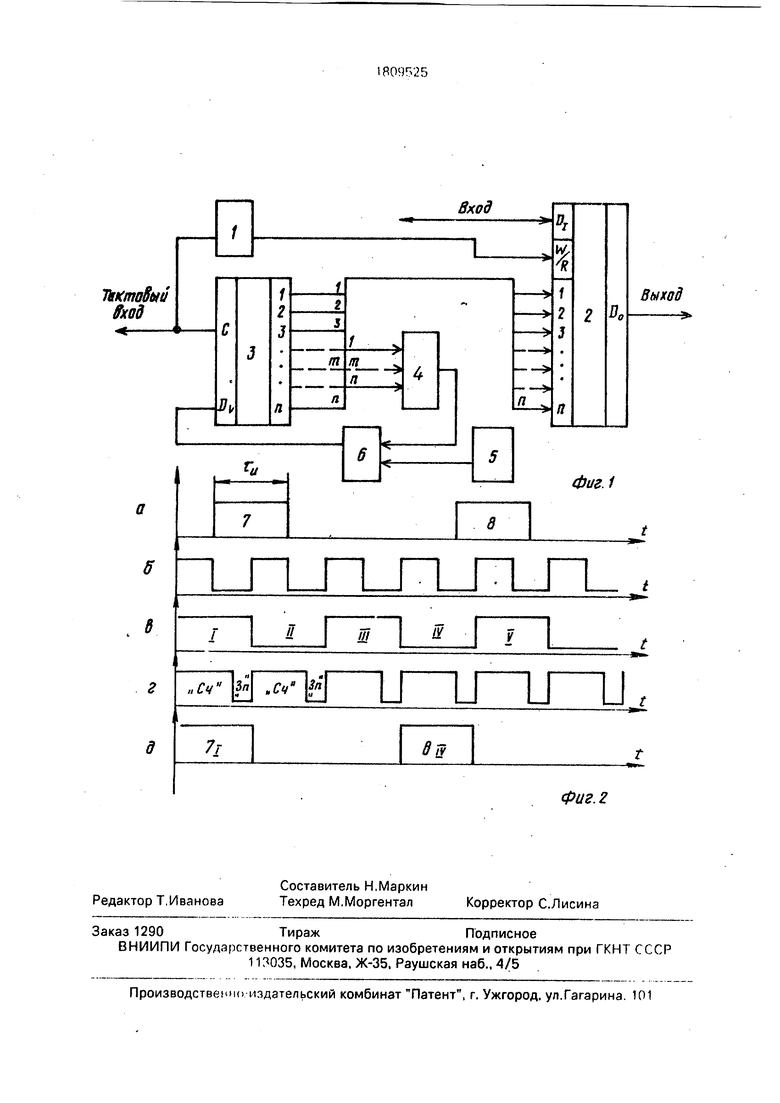

На фиг. 1 изображена схема устройства задержки; на фиг. 2 - диаграммы, поясняющие его работу.

Устройство задержки содержит блок 1 формирования сигналов Запись-считывание, блок 2 памяти (оперативно запоминающее устройство ОЗУ), регистр 3 сдвига, элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ. блок 5 пуска и элемент 6.ИЛИ, при этом входом устройства является информационный вход блока 2 памяти, тактовым входом устройства является вход блока 1 формирования сигналов Запись-считывание, который соединен со сдвиговым входом регистра 3 сдвига, а выход блока 1 формирования сигналов Запись-считывание соединен с одноименным входом блока 2 памяти, выходы регистра 3 сдвига соединены с адресными входами блока 2 памяти и со входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4, выход которого подключен к одному из входов элемента ИЛИ 6, другой вход которого подключен к выходу блока 5 пуска, а выход - к установочному входу регистра 3 сдвига, при этом выход блока 2 памяти (ОЗУ) является выходом устройства,

Устройство работает следующим образом.

На второй вход элемента ИЛИ 6 подается кратковременный сигнал начальной установки, формируемый блоком 5 пуска в начале работы устройства для установки выходов регистра 3 сдвига в исходное ненулевое состояние.

С тактового входа устройства импульсы типа меандр поступают на управляющий вход регистра 3 сдвига и на блок 1 формирования сигналов Запись-считывание, выходы регистра 3 сдвига, на которых

ел С

00

о

ю

01

ю

СП

формируется двоичный код, подключены к адресным входам блока 2 памяти. Для формирования этого двоичного кода на выходах регистра 3, с заданным числом цикла повторяемости m используется элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, входы которого подключены к определенным разрядам регистра 3 сдвига. Выход элемента 4 ИСКЛЮ- ЧАЮЩЕЕ ИЛИ определяет значение устанавливаемого при сдвиге левого разряда в двоичном коде и подключен к входу элемента 6 ИЛИ,

Величина сигнала на установочном входе регистра 3 сдвига определяется выходом элемента б ИЛИ. С выходов блока 1 формирования сигналы Запись-считывание поступают на соответствующий вход блока 2 памяти. При поступлении информационного сигнала на вход блока 2 памяти по сигналу Запись производится запись этого сигнала в ОЗУ по адресу, сформированному к этому моменту времени на регистре 3 сдвига.

Так как ОЗУ работает .таким образом, что при одном и том же выбранном адресе на его ячеек сначала считывается информация, затем записывается новая, то поток информационных битов, поступающих на вход этого запоминающего устройства, будет задержан на время Т, причем время Т определяется длиной повторяющейся двоичной кодовой последовательности, формируемой на каждом из выходов регистра 3 сдвига/Т n.t, где п - длина кодовой последовательности или число перебираемых ячеек ОЗУ, t - период тактового сигнала.

На диаграмме а) изображены входные сигналы 7 и 8, имеющие различную длительность и разное временное положение.

На диаграмме б) изображены тактовые сигналы, вырабатываемые генератором тактовых импульсов.

На диаграмме в) показана кодовая последовательность, сформированная на одном из выходов сдвигового регистра 3 и поступающая на соответствующий вход (разряд) адреса блока 2 памяти.

На диаграмме г) представлены сигналы, поступающие на входы Запись-считывание ОЗУ с выхода блока формирования сигналов Запись-считывание.

На диаграмме д) показаны сигналы на выходе устройства.

Из диаграммы следует, что импульс 7, длительностью записывается в ячейку 1 (ОЗУ), считывается из нее через время равное и проявляется на выходе устройства как импульс 7-I. Импульс 8 записывается в 4 - ячейку ОЗУ, считывается из нее через время равное Т и появляется на выходе устройства как импульс 8-IY (см. диаграмму д).

Снижение аппаратурных затрат в заявленном устройстве по сравнению с устройством прототипом достигается за счет объединения на регистре 2 сдвига функций перебора адресов блока памяти (осуществляемом в устройстве-прототипе счетчиком) и задание времени задержки (осуществляемом в устройстве-прототипе времязадаю- щим блоком).

Формула изобретения

- Устройство задержки, содержащее блок памяти и формирователь сигналов Запись- считывание, вход которого является тактовым входом устройства, а выход соединен с входом Запись-считывание блока памяти,

информационный вход которого является входом устройства, а выход блока памяти - выходом устройства, отличающееся тем, что, с целью повышения надежности за счет исключения сбоев, возникающих при

обращении к последним ячейкам блока памяти и упрощения, в него введены регистр сдвига, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, блок пуска и элемент ИЛИ, при этом выходы регистра сдвига соединены с адресными

входами блока памяти и входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом элемента ИЛИ, второй вход последнего подключен к блоку пуска, а выход элемента ИЛИ - к информационному входу регистра сдвига, сдвигающий вход которого подключен к входу формирователя сигналов Запись-считывание.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки | 1987 |

|

SU1610595A1 |

| Система формирования и приема телевизионного сигнала при передаче изображения | 1988 |

|

SU1555909A2 |

| Способ формирования и приема телевизионного сигнала при передаче изображения и система для его осуществления | 1986 |

|

SU1453619A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Цифровой коррелятор | 1985 |

|

SU1251107A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1988 |

|

SU1667075A1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1679487A1 |

Изобретение относится к импульсной технике и может быть использовано в радиолокации и связи. Цель - повышение надеж- ности. Устройство задержки содержит блок 1 формирования сигналов А3апись-считыва - ние, блок 2 памяти (ОЗУ), регистр 3 сдвига, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, блок 5 пуска и элемент ИЛИ 6. Задержка сигнала осуществляется путем запоминания входной информации, поступающей на вход блока 2 памяти, хранения ее и считывания через время, определенное циклом повторения двоичного адреса на выходах регистра 3 сдвига. Цель достигается за счет исключения сбоев, возникающих при обращении к последним ячейкам некоторых ОЗУ в момент формирования сигнала Установка времязадающим блоком. 2 ил.

| Авторское свидетельство СССР №1182647, кл.Н 03 К 5/13, 1982. |

Авторы

Даты

1993-04-15—Публикация

1989-05-03—Подача