Изобретение относится к радиолока- . ции, связи и т.д., а именно к устройствам задержки импульсных сигналов..

Целью изобретения является повышение надежности.

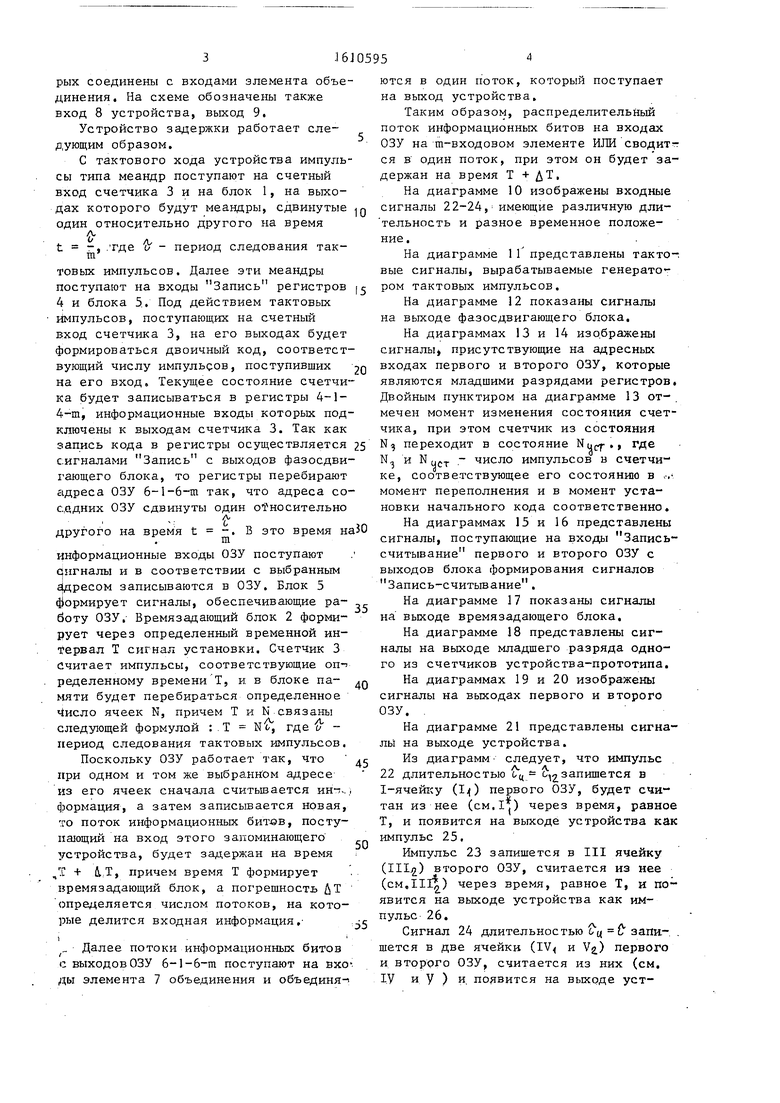

На фиг.1 изображена структурная схема предлагаемого устройства задерж-, ки; на фиг.2 - диаграммы, поясняющие его работу.

Устройство содержит фазосдвиганлций блок 1, времязадающий блок 2, счетчик 3, m регистров 4-1-4-т, блок 5 формирования сигналов Запись-считывание, блок памяти, содержащий m оперативных запоминающих устройств 6-1-6-т, и элемент объединения.

Вход устройства соединен с входами блока памяти. Тактовый вход устройства соединен с входом фазосдвигающего блока 1, выходы которого соединены с входами блока 5 формирования сигналов Запись-считырание соединены с одноименными входами ОЗУ. Счетчик 3 соединен с времязадающим блоком 2. Информационные входы регистров 4 соединены . между собой соответственно и подключе- нь: к выходам счетчика 3, счетный вход которого подключен к тактовому входу устройства. Входы Запись регистров подключены к выходам фазосдвигающего блока 1. Выходы регистров соединены с адресными входами ОЗУ, выходы котоел

СО

ел

рых соединены с входами элемента объединения. На схеме обозначены также вход 8 устройства, выход 9.

Устройство задержки работает следующим образом,

С тактового хода устройства импульсы типа меандр поступают на счетный вход счетчика 3 и на блок 1, на выходах которого будут меандры, сдвинутые один относительно другого на время

t -, , где - период следования такта

товых импульсов. Далее эти меандры поступают на входы Запись регистров 4 и блока 5. Под действием тактовых импульсов, поступающих на счетный вход счетчика 3, на его выходах будет формироваться двоичный код, соответствующий числу импульсов, поступивших на его вход. Текущее состояние счетчика будет записываться в регистры 4-1- 4-т, информационные входы которых подключены к выходам счетчика 3. Так как запись кода в регистры осуществляется сигналами Запись с выходов фазосдви 1 ающего блока, то регистры перебирают адреса ОЗУ 6-1-6-т так, что адреса соседних ОЗУ сдвинуты один относительно

другого на время t -. В это время н

информационные входы ОЗУ поступают qигнaлы и в соответствии с выбранным Адресом записываются в ОЗУ. Блок 5 формирует сигналы, обеспечивающие ра- боту ОЗУ.- Времязадающий блок 2 формирует через определенный временной интервал Т сигнал установки. Счетчик 3 Считает импульсы, соответствующие оп- ределенному времени Т, и в блоке па- мяти будет перебираться определенное Число ячеек N, причем Т и N связаны следующей формулой : . Т No, где v - период следования тактовых импульсов.

Поскольку ОЗУ работает так, что при одном и том же выбранном адресе из его ячеек сначала считьшается . формация, а затем записывается новая, то поток информационных битов, поступающий на вход этого запоминающего устройства, будет задержан на время ,Т + Ь Т, причем время Т формирует нремязадающий блок, а погрешность ДТ определяется числом потоков, на которые делится входная информация.-

1.

Далее потоки информационных битов

с выходов ОЗУ 6-1-6-т поступают на вхо ды элемента 7 объединения и объединя-i

ются в один поток, который поступает на выход устройства.

Таким образом, распределительный поток информационных битов на входах ОЗУ на та-входовом элементе ИЛИ сводиться в один поток, при этом он будет задержан на время Т + ДТ,

На диаграмме 10 изображены входные сигналы 22-24, имеющие различную дли- тельность и разное временное положение .

На диаграмме 1 1 представлены такто-т вые сигналы, вырабатываемые генерато«г ром тактовых импульсов.

На диаграмме 12 показаны сигналы на выходе фазосдвигающего блока.

На диаграммах 13 и 14 изображены сигналы присутствующие на адресных входах первого и второго ОЗУ, которые являются младшими разрядами регистров. Двойным пунктиром на диаграмме 13 от-. мечен момент изменения состояния счетчика, при этом счетчик из состояния N переходит в состояние Nu(., где N и N (,(4 - число импульсов в счетчике, соответствующее его состоянию в .-.-. момент переполнения и в момент установки начального кода соответственно.

На диаграммах 15 и 16 представлены сигналы, поступающие на входы Запись- считывание первого и второго ОЗУ с выходов блока формирования сигналов Запись-считьшание.

На диаграмме 17 показаны сигналы на выходе времязадающего блока.

На диаграмме 18 представлены сигналы на выходе младшего разряда одного из счетчиков устройства-прототипа.

На диаграммах 19 и 20 изображены сигналы на выходах первого и второго ОЗУ. .

На диаграмме 21 представлены сигналы на выходе устройства.

Из диаграмм следует, что импульс 22 длительностью , - с,2запишется в 1-ячейку (1) первого ОЗУ, будет считан из нее (см,it) через время, равное Т, и появится на выходе устройства как импульс 25,

Импульс 23 запишется в III ячейку (111) второго ОЗУ, считается из нее (cM.III) через время, равное Т, и появится на выходе устройства как импульс 26.

Сигнал 24 длительностью t y С запи.- . шется в две ячейки (IV и Vg.) первого и второго ОЗУ, считается из них (см. IV и у ) и, появится на выходе уст51610595

ройства (см. импульс 27) через время,

равное Т,

Из диаграммы 17 следует, что если бы врёмязадшощий блок был подключен к установочным входам всех счетчиков, т.е. согласно формуле устройства-прототипа, то это привело бы к тому, что время обращения к ячейке I было бы

5

равно 0,2 (см. пунктир на диаграмме 13). Сигнал Запись-считывание этого ОЗУ не меняется (см. диаграмму 15), поэтому к последней ячейке, которая также является укороченной, обращение бьшо бы только в режиме считьюания.

На диаграмме 18 видно, что в мо- мент появления сигнала Установка на выходе времязадающего блока один из счетчиков устройства-прототипа меняет

Для обоснования эффективности данн го технического решения проведем срав нительный анализ его с устройством-пр тотипом.

Из анализа работы устройства-прото типа следует, что при обращении к пос ледним ячейкам ОЗУ в работе устройства прототипа возникают сбои. Причиной воз

Q никновения сбоев является то, что в устройстве-прототипе применен один . времязадающий блок, выход которого соединен с установочными входами всех счетчиков. Такое подключение вывода

5 времязадающего блока приводит к тому, что при выборе последних ячеек блоков ОЗУ, младший разряд адреса которых меняется после появления сигнала Установка, в их работе происходят сбои.

свое состояние, то есть в течение вре-20 Происходит это потому, что в момент

формирования адреса последней ячейки обращение к ней производится лишь в

мени состояние счетчика меняется дважды. Это отмечено импульсами 28 и 29. Так как в предлагаемом техническом решении счетный вход счетчика

одном из режимов, так как состояние счетчика меняется одним фронтом, а

подключен к тактовому входу устройст- 25 сигнал на выходе вр.емязадающего бло35

ва, а входы Запись регистров - к выходам фазосдвигающего блока, т.е. запись кода в регистры производится тог да, когда переходные процессы в счетчике закончились, то в течение фор- зо мирования этих импульсов (28 и 29) - в первый .регистр будет записано состояние, соответствующее импульсу 28 (см. диаграмму 14), а во второй - им пульсу 29 (см. диаграмму 14).

Фазосдвигающий блок.1 может содержать, например, элемент согласования по входу (МС 155ЛАВ), многоотводньй элемент задержки (МЛЗ-0, 25-600-Н), элементы согласования по выходу (МС 155ЛАЗ), имеющие прямые и инверсные входы.

В качестве многоотводного элемента задержки могут быть использованы линии задержки с- распределенными параметрами, линии задержки с сосредоточенными параметрами, регистры, счетчики С дешифраторами и т.д.

Блок 5 формирования сигналов .

ка появляется в момент формирования другого фронта. При нормальной работе блока памяти длительность адресного сигнала равна периоду следования тактовых импульсов. При выборке последней, ячейки в момент

t га .

где р порядковый номер выхода фазосдвигающего блока, подключенного к счетному входу соответствующего счетчика, появляется сигнал установки всех счетчиков в исходное состояние. Это при. водит к тому, что длительность адресного сигнала первых и последних яче- 4Q ек будет меньше периода следования .- тактовых импульсов. Так как сигнал Запись-считывание вырабатьшается синхронно с адресным сигналом и всегда равен длительности периода следования, то это приводит к тому, что обращение к последним ячейкам некоторых: ОЗУ будет лишь в одном из режимов. Вероятность появления сбоя можно определить по формуле 1/2N, где

45

-а-- - Г

пись-считыбание вырабатывает импульсыJQ N - число ячеек, пропорциональное треспециальной формы и может быть выполнен, .например, в виде элементов НЕ- ИЛИ, на первые входы которых подается

сигнал частоты f(t + -), на второй

- ,-. р вход - сигнал f (t + --) с cooTBeTCT - ,m

вующих инверсных выходов фазосдвигаю- (цего блока, где ,2,. . .т.

буемой величине задержки Т}ад. N можно определить из формулы T.jg|.NC , где - период следования тактовых имл. пульс ов.

г В предлагаемом техническом решении формирование величины задержки осуществляется также одним времязадаю- щим блоком, соединенным со счетчиком, Но при этом счетчик освобожден от

Для обоснования эффективности данног го технического решения проведем сравнительный анализ его с устройством-прототипом.

Из анализа работы устройства-прототипа следует, что при обращении к последним ячейкам ОЗУ в работе устройства- прототипа возникают сбои. Причиной возникновения сбоев является то, что в устройстве-прототипе применен один . времязадающий блок, выход которого соединен с установочными входами всех счетчиков. Такое подключение вывода

времязадающего блока приводит к тому, что при выборе последних ячеек блоков ОЗУ, младший разряд адреса которых меняется после появления сигнала Установка, в их работе происходят сбои.

одном из режимов, так как состояние счетчика меняется одним фронтом, а

ка появляется в момент формирования другого фронта. При нормальной работе блока памяти длительность адресного сигнала равна периоду следования тактовых импульсов. При выборке последней, ячейки в момент

t га .

где р 35

зо

порядковый номер выхода фазосдвигающего блока, подключенного к счетному входу соответствующего счетчика, появляется сигнал установки всех счетчиков в исходное состояние. Это приводит к тому, что длительность адресного сигнала первых и последних яче- 4Q ек будет меньше периода следования . тактовых импульсов. Так как сигнал Запись-считывание вырабатьшается синхронно с адресным сигналом и всегда равен длительности периода следования, то это приводит к тому, что обращение к последним ячейкам некоторых: ОЗУ будет лишь в одном из режимов Вероятность появления сбоя можно определить по формуле 1/2N, где

45

-а-- - Г

буемой величине задержки Т}ад. N можно определить из формулы T.jg|.NC , где - период следования тактовых имл. пульс ов.

В предлагаемом техническом решении формирование величины задержки осуществляется также одним времязадаю- щим блоком, соединенным со счетчиком, Но при этом счетчик освобожден от

функции перебора ячеек ОЗУ, которая нозложена на вновь введеннью регистры, включенные между выходами счетчика и адресными входами ОЗУ. Такое-включе-;) , нив регистров позволяет избавиться от i сбоев, возникающих в устройстве-прото- тиде, так сигналы Запись на входах регистров сдвинуты одинотносгг- ; tefijiHo другод о на время и /т, т.е. ус- ||0 тановка кода в каждом из. регистров j :i:. j производится через время, равное длительности периода следования тактовых импульсов.. Сигнал Установка, формиг:

При этом достигается.синхронность адресных сигналов и сигналов Запись- считьшание при выборе последней ячейки, формирование которой не зависит от сигнала Установка.

Формула изобретения

Устройство задержки, содержащее элемент объединения блок памяти, сог,. держащий m оперативных запоминающих устройств,- блок фбрмирования сигналов Запись-считывание, фазосдвигающий

руемый на выходе времязадающего бло- 15 лок, счетчик и подключенный к нему

времязадающий блок, тактовый вход устка, не влияет на состояние регистров (как это имело место в устройстве- Прототипе, где сигналом Установка менялось состояние всех счетчиков) . Обусловлено это тем, что в момент по- 20 явления сигнала Установка с выхода времязадающего блока счетчик меняет

сво е состояние, то есть в течение Времени 2 состояние счетчика меняется

ройства соединен с входом счетчика и входом фазосдвигающего блока, выходы которого через блок формирования сигналов Запись-считьшание соединены с первыми входами m оперативных запоминающих устройств блока памяти, вторые входы которых подключены к информационному входу, а выходы через эледваады. Это отмечено импульсами 28 и 5 нт объединения соединены с выходной 29. Но так как счетный вход счетчика шной устройства, отличающе подключен к тактовому входу устройст- с я тем, что, с целью повышения на- ва, а входы Запись регистров - к вы- дежности, в него введены m регист- ходам фазосдвигающего блока, т.е. за- Ров. информационные входы которых сое- пись кода в регистры производится пос-30 динены между собой соответственно и ле окончания переходньк процессов вподключены к вькоду счетчика, входы

счетчике, то в течение формирования Запись подключень. к выходам фазосдэтих импульсов (28 и 29) в первый per вигающего блока, а выходы подключены гистр будет записано состояние, соот- третьим входам оперативньк запоми- . бететвующее импульсу 28 (см. диаграм- 35 « устройств блока памяти. му 13), а во второй - импульсу 29.

При этом достигается.синхронность адресных сигналов и сигналов Запись- считьшание при выборе последней ячейки, формирование которой не зависит от сигнала Установка.

Формула изобретения

Устройство задержки, содержащее элемент объединения блок памяти, сог,. держащий m оперативных запоминающих устройств,- блок фбрмирования сигналов Запись-считывание, фазосдвигающий

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки | 1989 |

|

SU1809525A1 |

| Устройство задержки | 1989 |

|

SU1698966A1 |

| Способ формирования и приема телевизионного сигнала при передаче изображения и система для его осуществления | 1986 |

|

SU1453619A1 |

| Система формирования и приема телевизионного сигнала при передаче изображения | 1988 |

|

SU1555909A2 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Устройство задержки | 1990 |

|

SU1750036A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

Изобретение относится к импульсной технике и может использоваться в радиолокации. Цель изобретения - повышение надежности за счет исключения сбоев, возникающих при обращении к последним ячейкам некоторых блоков ОЗУ, в момент формирования сигнала "Установка" времязадающим блоком. Устройство содержит фазосдвигающий блок, времязадающий блок, счетчик, N регистров, блок формирования сигналов "Запись-считывание", блок памяти, содержащий оперативных запоминающих устройств, элемент ИЛИ. Устройство позволяет задержать сигналы длительностью Τи/Τ с высокой точностью. Задержка осуществляется путем разделения входной информации на M потоков, сдвинутых относительно друг друга на время T=Τ/M. В каждом потоке информация запоминается, хранится и считывается через время, формируемое времязадающим блоком. Введение регистров позволяет исключить сбои. Регистры перебирают адресные ячейки блока памяти, на входы которого подаются тактовые импульсы, задержанные друг относительно друга на Τ/M. С выхода блока памяти потоки информации объединяются в один поток с помощью ячейки ИЛИ, выход которой является выходом устройства. 2 ил.

| Авторское свидетельство СССР № 1182647, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-11-30—Публикация

1987-09-08—Подача