Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах контроля цифровых блоков в процессе эксплуатации.

Целью изобретения является повышение достоверности контроля.

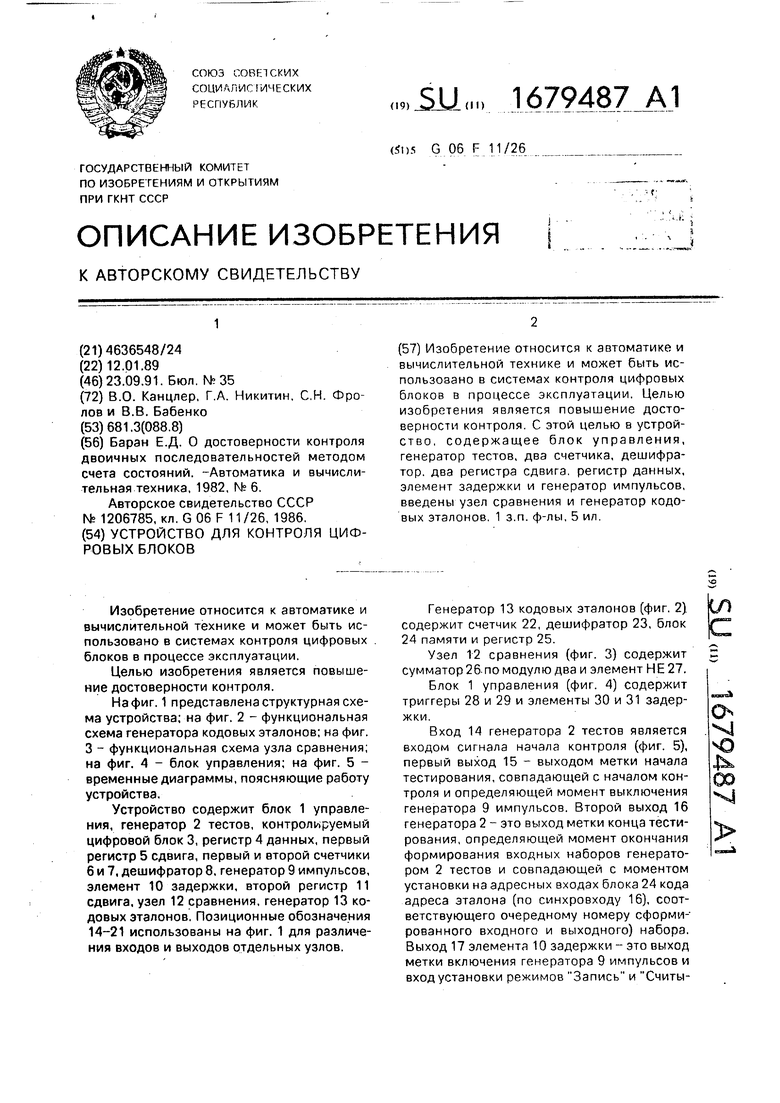

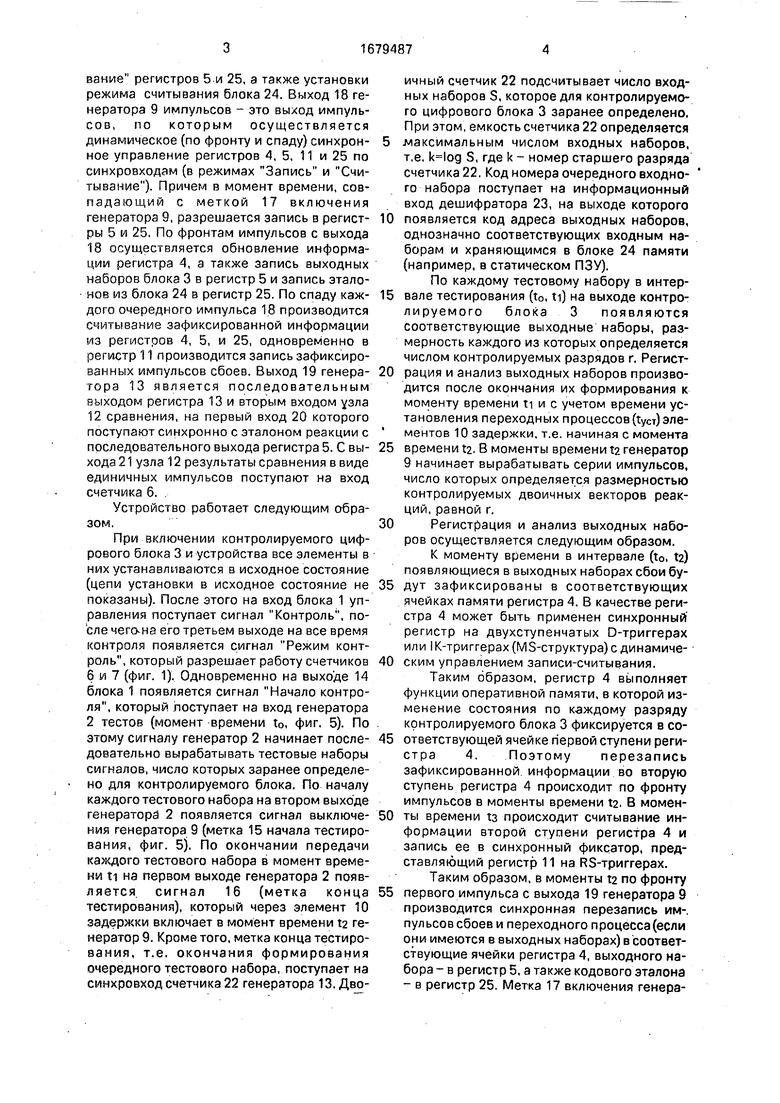

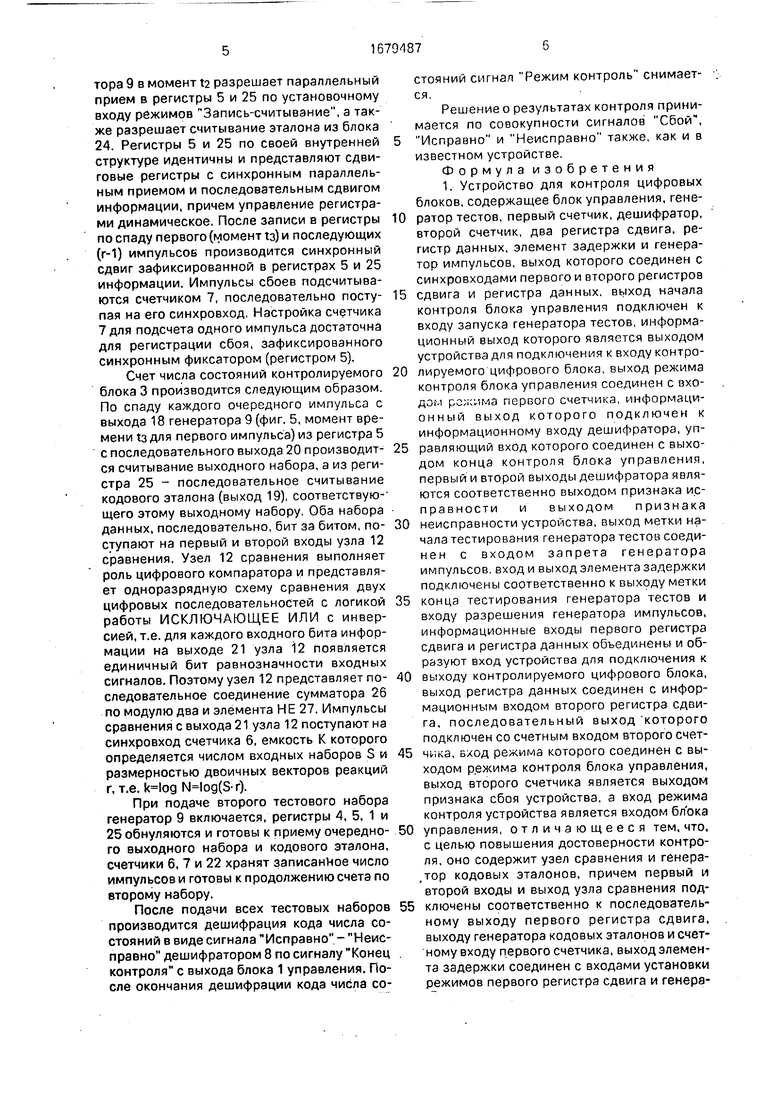

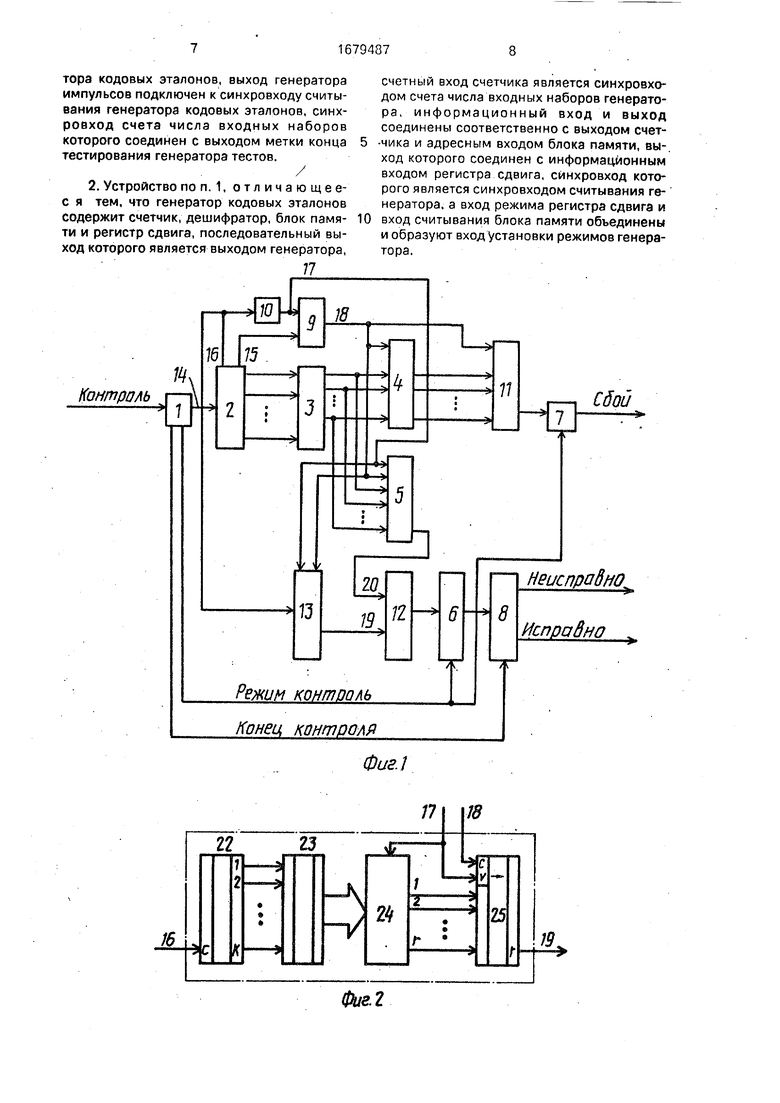

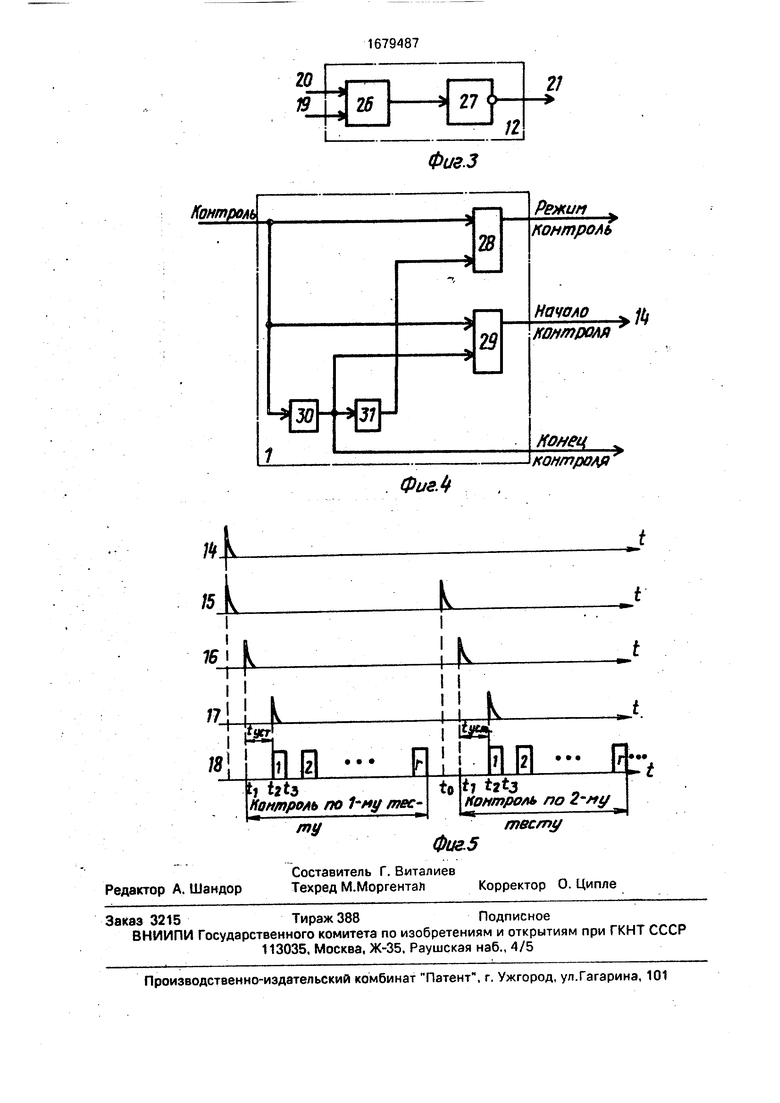

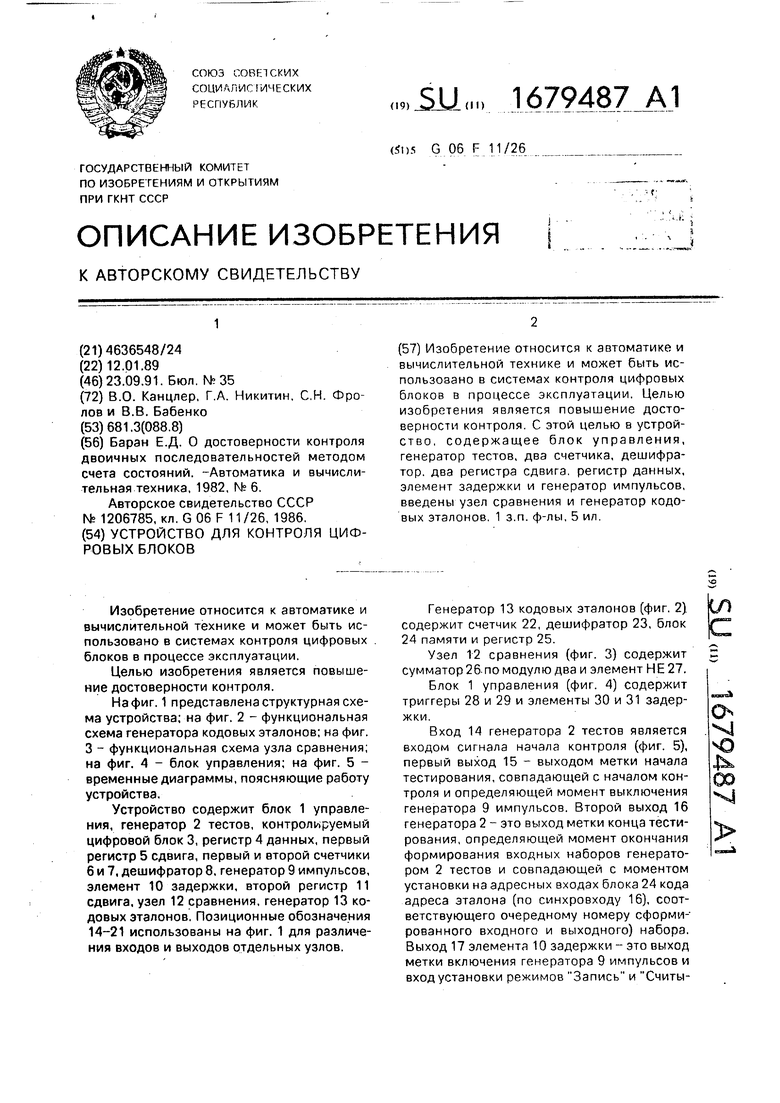

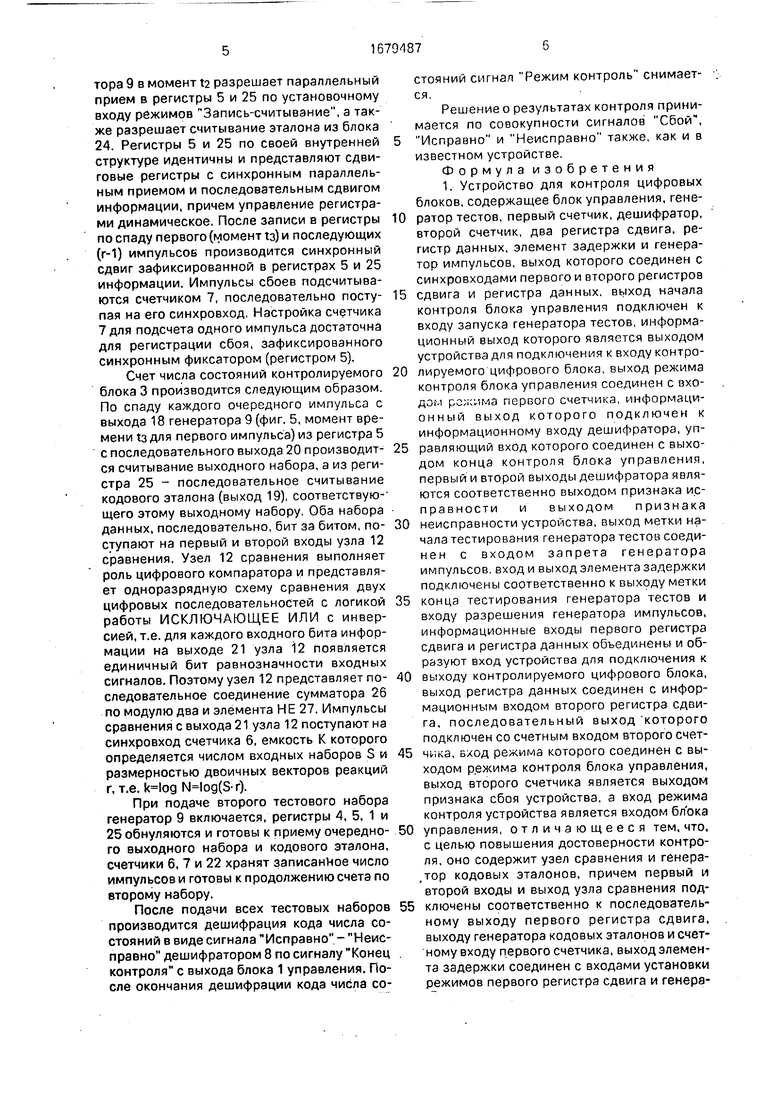

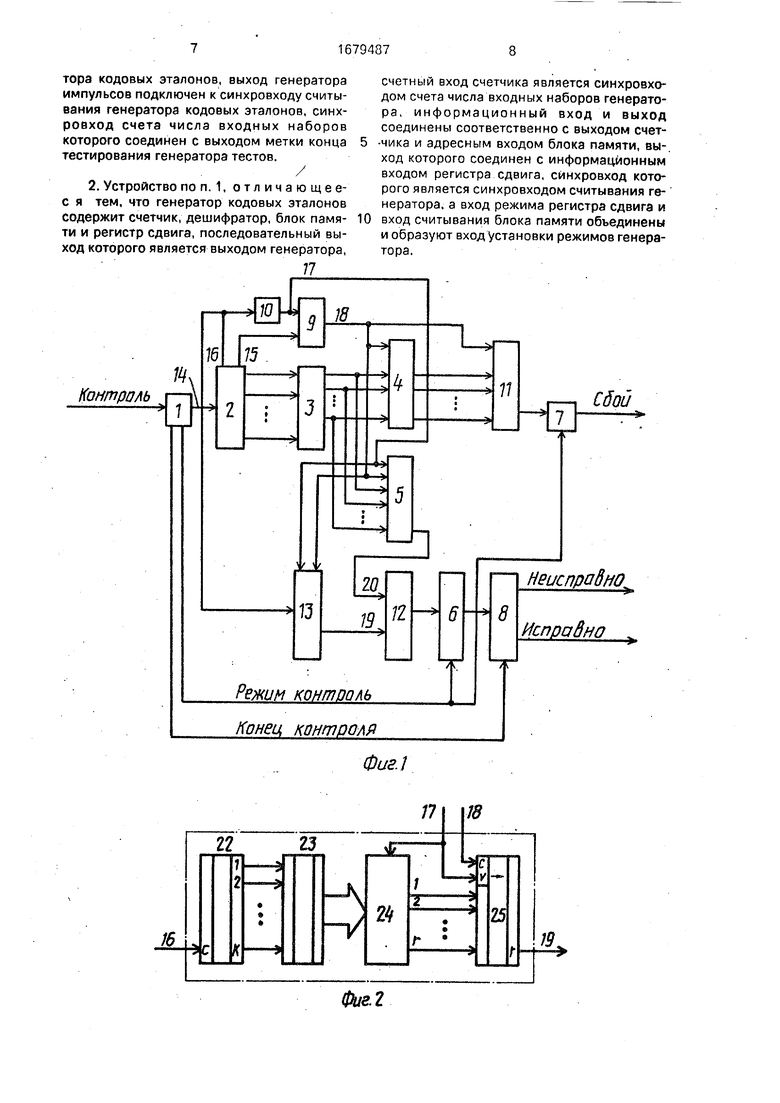

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - функциональная схема генератора кодовых эталонов; на фиг. 3 - функциональная схема узла сравнения, на фиг. 4 - блок управления; на фиг. 5 - временные диаграммы, поясняющие работу устройства.

Устройство содержит блок 1 управления, генератор 2 тестов, контролируемый цифровой блок 3, регистр 4 данных, первый регистр 5 сдвига, первый и второй счетчики 6 и 7, дешифратор 8, генератор 9 импульсов, элемент 10 задержки, второй регистр 11 сдвига, узел 12 сравнения, генератор 13 кодовых эталонов. Позиционные обозначения 14-21 использованы на фиг. 1 для различения входов и выходов отдельных узлов.

Генератор 13 кодовых эталонов (фиг. 2) содержит счетчик 22, дешифратор 23, блок 24 памяти и регистр 25

Узел 12 сравнения (фиг. 3) содержит сумматор 26 по модулю два и элемент НЕ 27.

Блок 1 управления (фиг. 4) содержит триггеры 28 и 29 и элементы 30 и 31 задержки

Вход 14 генератора 2 тестов является входом сигнала начала контроля (фиг. 5), первый выход 15 - выходом метки начала тестирования, совпадающей с началом контроля и определяющей момент выключения генератора 9 импульсов. Второй выход 16 генератора 2 - это выход метки конца тестирования, определяющей момент окончания формирования входных наборов генератором 2 тестов и совпадающей с моментом установки на адресных входах блока 24 кода адреса эталона (по синхровходу 16), соответствующего очередному номеру сформированного входного и выходного) набора. Выход 17 элемента 10 задержки - это выход метки включения генератора 9 импульсов и вход установки режимов Запись и Считысл

с

А

о Ч ю

-ч

вание регистров 5 и 25, а также установки режима считывания блока 24. Выход 18 генератора 9 импульсов - это выход импульсов, по которым осуществляется динамическое (по фронту и спаду) синхронное управление регистров 4, 5, 11 и 25 по синхровходам (в режимах Запись и Считывание). Причем в момент времени, совпадающий с меткой 17 включения генератора 9, разрешается запись в регистры 5 и 25. По фронтам импульсов с выхода 18 осуществляется обновление информации регистра 4, а также запись выходных наборов блока 3 в регистр 5 и запись эталонов из блока 24 в регистр 25. По спаду каждого очередного импульса 18 производится считывание зафиксированной информации из регистров 4, 5, и 25, одновременно в регистр 11 производится запись зафиксированных импульсов сбоев. Выход 19 генератора 13 является последовательным выходом регистра 13 и вторым входом узла 12 сравнения, на первый вход 20 которого поступают синхронно с эталоном реакции с последовательного выхода регистра 5. С выхода 21 узла 12 результаты сравнения в виде единичных импульсов поступают на вход счетчика 6.

Устройство работает следующим образом.

При включении контролируемого цифрового блока 3 и устройства все элементы в них устанавливаются в исходное состояние (цепи установки в исходное состояние не показаны). После этого на вход блока 1 управления поступает сигнал Контроль, после чегскна его третьем выходе на все время контроля появляется сигнал Режим контроль, который разрешает работу счетчиков 6 и 7 (фиг. 1). Одновременно на выходе 14 блока 1 появляется сигнал Начало контроля, который поступает на вход генератора 2 тестов (момент времени to, фиг. 5). По этому сигналу генератор 2 начинает последовательно вырабатывать тестовые наборы сигналов, число которых заранее определено для контролируемого блока. По началу каждого тестового набора на втором выходе генератора 2 появляется сигнал выключения генератора 9 (метка 15 начала тестирования, фиг. 5). По окончании передачи каждого тестового набора в момент времени ti на первом выходе генератора 2 появляется сигнал 16 (метка конца тестирования), который через элемент 10 задержки включает в момент времени t2 генератор 9. Кроме того, метка конца тестирования, т.е. окончания формирования очередного тестового набора, поступает на синхровход счетчика 22 генератора 13. Двоичный счетчик 22 подсчитывает число входных наборов S, которое для контролируемого цифрового блока 3 заранее определено. При этом, емкость счетчика 22 определяется

максимальным числом входных наборов, т.е. S, где k - номер старшего разряда счетчика 22. Код номера очередного входного набора поступает на информационный вход дешифратора 23, на выходе которого

0 появляется код адреса выходных наборов, однозначно соответствующих входным наборам и храняющимся в блоке 24 памяти (например, в статическом ПЗУ).

По каждому тестовому набору в интер5 вале тестирования (to. ti) на выходе контролируемого блока 3 появляются соответствующие выходные наборы, размерность каждого из которых определяется числом контролируемых разрядов г. Регист0 рация и анализ выходных наборов производится после окончания их формирования к моменту времени ti и с учетом времени установления переходных процессов (tyci) элементов 10 задержки, т.е. начиная с момента

5 времени t2. В моменты времени ta генератор 9 начинает вырабатывать серии импульсов, число которых определяется размерностью контролируемых двоичных векторов реакций, равной г.

0 Регистрация и анализ выходных наборов осуществляется следующим образом.

К моменту времени в интервале (to, lz) появляющиеся в выходных наборах сбои бу5 дут зафиксированы в соответствующих ячейках памяти регистра 4. В качестве регистра 4 может быть применен синхронный регистр на двухступенчатых D-триггерах или К-триггерах(МЗ-структура)сдинамиче0 ским управлением записи-считывания.

Таким образом, регистр 4 выполняет функции оперативной памяти, в которой изменение состояния по каждому разряду контролируемого блока 3 фиксируется в со5 ответствующей ячейке первой ступени регистра 4. Поэтому перезапись зафиксированной информации во вторую ступень регистра 4 происходит по фронту импульсов в моменты времени t2. В момен0 ты времени t3 происходит считывание информации второй ступени регистра 4 и запись ее в синхронный фиксатор, представляющий регистр 11 на RS-триггерах. Таким образом, в моменты т.2 по фронту

5 первого импульса с выхода 19 генератора 9 производится синхронная перезапись им-, пульсов сбоев и переходного процесса (если они имеются в выходных наборах) в соответствующие ячейки регистра 4, выходного набора - в регистр 5, а также кодового эталона - в регистр 25. Метка 17 включения генератора 9 в момент ta разрешает параллельный прием в регистры 5 и 25 по установочному входу режимов Запись-считывание, а также разрешает считывание эталона из блока 24. Регистры 5 и 25 по своей внутренней структуре идентичны и представляют сдвиговые регистры с синхронным параллельным приемом и последовательным сдвигом информации, причем управление регистрами динамическое. После записи в регистры по спаду первого (момент гз) и последующих (г-1) импульсов производится синхронный сдвиг зафиксированной в регистрах 5 и 25 информации. Импульсы сбоев подсчитываются счетчиком 7, последовательно поступая на его синхровход. Настройка счетчика 7 для подсчета одного импульса достаточна для регистрации сбоя, зафиксированного синхронным фиксатором (регистром 5).

Счет числа состояний контролируемого блока 3 производится следующим образом. По спаду каждого очередного импульса с выхода 18 генератора 9 (фиг. 5, момент времени ta для первого импульса) из регистра 5 с последовательного выхода 20 производится считывание выходного набора, а из регистра 25 - последовательное считывание кодового эталона (выход 19), соответствую- щего этому выходному набору. Оба набора данных, последовательно, бит за битом, поступают на первый и второй входы узла 12 сравнения. Узел 12 сравнения выполняет роль цифрового компаратора и представляет одноразрядную схему сравнения двух цифровых последовательностей с логикой работы ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией, т.е. для каждого входного бита информации на выходе 21 узла 12 появляется единичный бит равнозначности входных сигналов. Поэтому узел 12 представляет последовательное соединение сумматора 26 по модулю два и элемента НЕ 27. Импульсы сравнения с выхода 21 узла 12 поступают на синхровход счетчика 6, емкость К которого определяется числом входных наборов S и размерностью двоичных векторов реакций г, т.е. (S-r).

При подаче второго тестового набора генератор 9 включается, регистры 4, 5, 1 и 25 обнуляются и готовы к приему очередного выходного набора и кодового эталона, счетчики 6, 7 и 22 хранят записанное число импульсов и готовы к продолжению счета по второму набору.

После подачи всех тестовых наборов производится дешифрация кода числа состояний в виде сигнала Исправно - Неисправно дешифратором 8 по сигналу Конец контроля с выхода блока 1 управления. После окончания дешифрации кода числа состояний сигнап Режим контроль снимается.

Решение о результатах контроля принимается по совокупности сигналов Сбой, Исправно и Неисправно также, как и в известном устройстве.

Формула изобретения 1. Устройство для контроля цифровых блоков, содержащее блок управления, гене0 ратор тестов, первый счетчик, дешифратор, второй счетчик, два регистра сдвига, регистр данных, элемент задержки и генератор импульсов, выход которого соединен с синхровходами первого и второго регистров

5 сдвига и регистра данных, выход начала контроля блока управления подключен к входу запуска генератора тестов, информационный выход которого является выходом устройства для подключения к входу контро0 лируемого цифрового блока, выход режима контроля блока управления соединен с входом режима первого счетчика, информационный выход которого подключен к информационному входу дешифратора, уп5 равляющий вход которого соединен с выходом конца контроля блока управления, первый и второй выходы дешифратора являются соответственно выходом признака исправности и выходом признака

0 неисправности устройства, выход метки начала тестирования генератора тестов соеди- нен с входом запрета генератора импульсов, вход и выход элемента задержки подключены соответственно к выходу метки

5 конца тестирования генератора тестов и входу разрешения генератора импульсов, информационные входы первого регистра сдвига и регистра данных объединены и образуют вход устройства для подключения к

0 выходу контролируемого цифрового блока, выход регистра данных соединен с информационным входом второго регистра сдвига, последовательный выход которого подключен со счетным входом второго счет5 чика, вход режима которого соединен с выходом режима контроля блока управления, выход второго счетчика является выходом признака сбоя устройства, а вход режима контроля устройства является входом блока

0 управления, отличающееся тем. что, с целью повышения достоверности контроля, оно содержит узел сравнения и генера- ,тор кодовых эталонов, причем первый и второй входы и выход узла сравнения под5 ключены соответственно к последовательному выходу первого регистра сдвига, выходу генератора кодовых эталонов и счетному входу первого счетчика, выход элемента задержки соединен с входами установки режимов первого регистра сдвига и генератора кодовых эталонов, выход генератора импульсов подключен к синхровходу считывания генератора кодовых эталонов, синх- ровход счета числа входных наборов которого соединен с выходом метки конца тестирования генератора тестов.

/

2. Устройство по п. 1, отличающее- с я тем, что генератор кодовых эталонов содержит счетчик, дешифратор, блок памяти и регистр сдвига, последовательный выход которого является выходом генератора,

77

0

счетный вход счетчика является синхровхо- дом счета числа входных наборов генератора, информационный вход и выход соединены соответственно с выходом счет- чика и адресным входом блока памяти, выход которого соединен с информационным входом регистра сдвига, синхровход которого является синхровходом считывания генератора, а вход режима регистра сдвига и вход считывания блока памяти объединены и образуют вход установки режимов генератора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1989 |

|

SU1793441A2 |

| Устройство для контроля логических блоков | 1984 |

|

SU1196692A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1405059A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1290333A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1386999A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах контроля цифровых блоков в процессе эксплуатации. Целью изобретения является повышение достоверности контроля С этой целью в устройство, содержащее блок управления, генератор тестов, два счетчика, дешифратор два регистра сдвига регистр данных, элемент задержки и генератор импульсов, введены узел сравнения и генератор кодовых эталонов 1 з п. ф-лы, 5 ил

Контроль

Фиг. 2

НеиспраВнО Испрадно

Фиг.1

Физ.З

Фиг4

| Баран Е.Д | |||

| О достоверности контроля двоичных последовательностей методом счета состояний | |||

| -Автоматика и вычислительная техника, 1982, N 6 | |||

| Устройство для контроля цифровых блоков | 1984 |

|

SU1206785A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-09-23—Публикация

1989-01-12—Подача