и седьмого элементов И, выходы которых соединены соотв етственно с входами четвертого элемента ИЛИ, выход которого подключен к единичному входу третьего триггера, нулевой вход которого соединен с вторьм запросным входом устройства, а через второй формирователь импульса - с вторым входом шестого элемента И и с единичным входом четвертого триггера, нулевой вход которого соединен с нулевым выходом третьего триггера, с вторым входом пятого элемента И и первым входом восьмого элемента И, второй вход которого соединен с прямым выходом второго триггера, выходы пятого и восьмого элементов И соединены с входами пятого элемента ИЛИ, выход которого соединен с единичным

входом первого триггера, третий вх.од пятого элемента И соединен с инверсным выходом четвертого триггера, прямой выход которого соединен с вторым „входом седьмого элемента И, инверсный выход второго триггера соединен с третьим входом шестого элемента И, прямой выход третьего триггера соединен с вторыми входами элементов И

„ второй и четвертой групп, с вторым

выходом представления прерывания устройства и с первыми входами третьего и четвертого элементов И, вторые входы которых пoдкJдачeны соответственно к третьему и четвертому управляющим входам устройства, а выход - к входам шестого элемента ИЛИ, выход которого соединен с установочньм входом второго счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная система | 1988 |

|

SU1601614A1 |

| Устройство управления двухпортовой памятью | 1987 |

|

SU1490678A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения двух электронных вычислительных машин (эвм) | 1984 |

|

SU1187172A1 |

| Устройство для контроля хода программ | 1989 |

|

SU1645960A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1691892A1 |

| Устройство для имитации неисправностей | 1986 |

|

SU1337900A1 |

| Устройство для сопряжения двух ЭВМ | 1985 |

|

SU1302290A1 |

| Устройство для сопряжения двух электронно-вычислительных машин с внешними абонентами | 1985 |

|

SU1264192A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

ДВУХПОРТОВОЕ УСТРОЙСТВО СОПРЯЖЕНИЯ В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ, содержащее три триггера, шесть элементов И, первый элемент ИЛИ и первый формирователь импульса, о т л и ч аю Ц е. е с я тем, что, с целью повышения быстродействия, оно содержит шесть групп элементов И, две группы элементов ИЛИ, два счетчика, второй формирователь, импульса, четверть(й . триггер, седьмой и восьмой элементы И, второй, третий, четвертый, пятый и ягестой элементы ИЛИ и блок буферной памяти, причем первый и второй информационные входы устройства подключены соответственно к первьм входам элементов И первой и второй групп, вькоды которых соединены с входами элементов ИЛИ первой группы, выходы которых соединены с информационными входами блока буферной памяти, адрес ные входы которого соединены с выходами элементов ИЛИ второй группы, .первые и вторые входы которых соедииены соответственно с выходами элементов И третьей и четвертой групп, первые входы которых соединены соответственно с выходами первого и второго счетчиков, информационные входы которых соединены соответственно с выходами элементов И пятой и шестой групп, первые входы которых подключены соответственно К первым и вторым информационным входам уст- ройства, выход блока буферной памяти подключен к первому и второму информационным выходам устройства, входы чтения и записи блока буферной памяти подключены соответственно к выходам первого и второго элементов ИЛИ, первые и вторые входы которых подключены соответственно к выходам первого, второго и третьего и четвертого элементов И, прямой выход первого триггера подключен к вторьм входам элементов И первой и третьей групп, к первому выходу представления СО прерьгеания устройства и к первым входам первого и второго элементов И, к вторым входам которых подключены соответственно первый и второй управляюпще входы устройства, выходы первого и второго элементов И соединены соответственно с входами третьего ел элемента ИЛИ, выход которого соединен О) с установочным входом первого счето чика, вторые входы элементов И пятой 00 и шестой групп подключены соответст- венно к первому и третьему управляющим входам устройства, а инверсные входы - соответственно к первому и второму запросным входам устройства, ; первый запросный вход устройства соединен с нулевым входом первого триггера, а через первый формирователь импульса - с первым входом пятого э емента И, с инверсным входом шестого элемента И и с единнчньм входом второго триггера, нулевой вход которого соединен с инверсным выходом первого .триггера и с первьми входами шестого

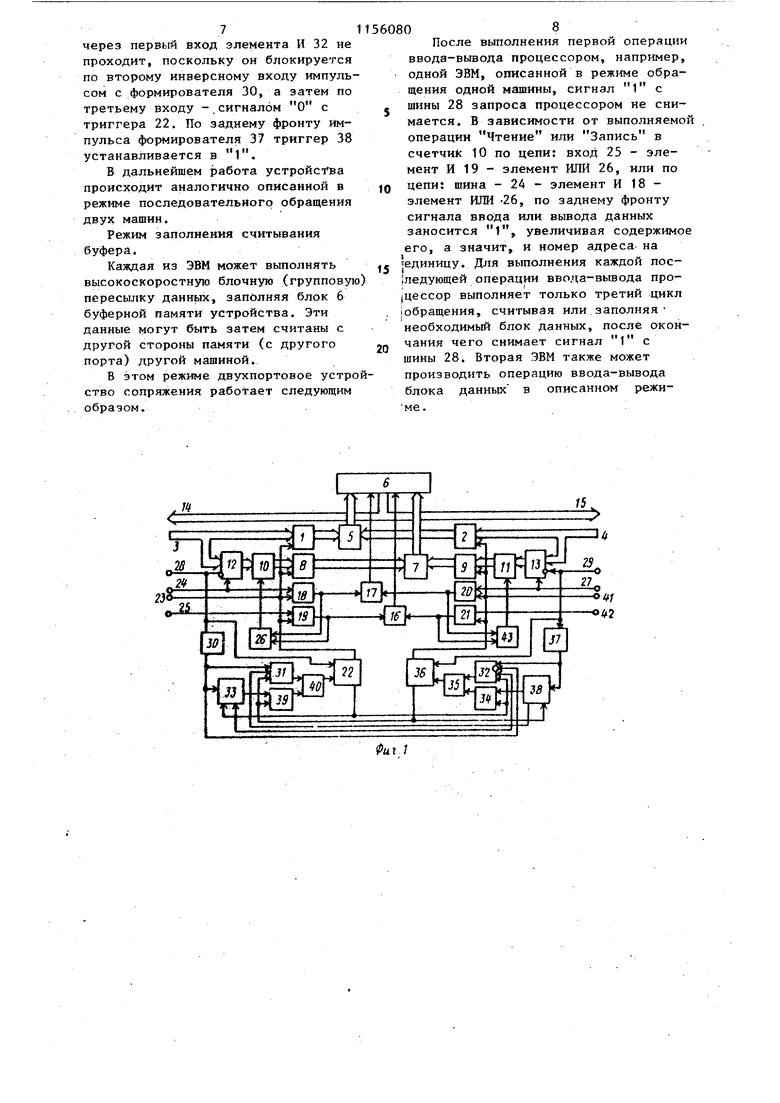

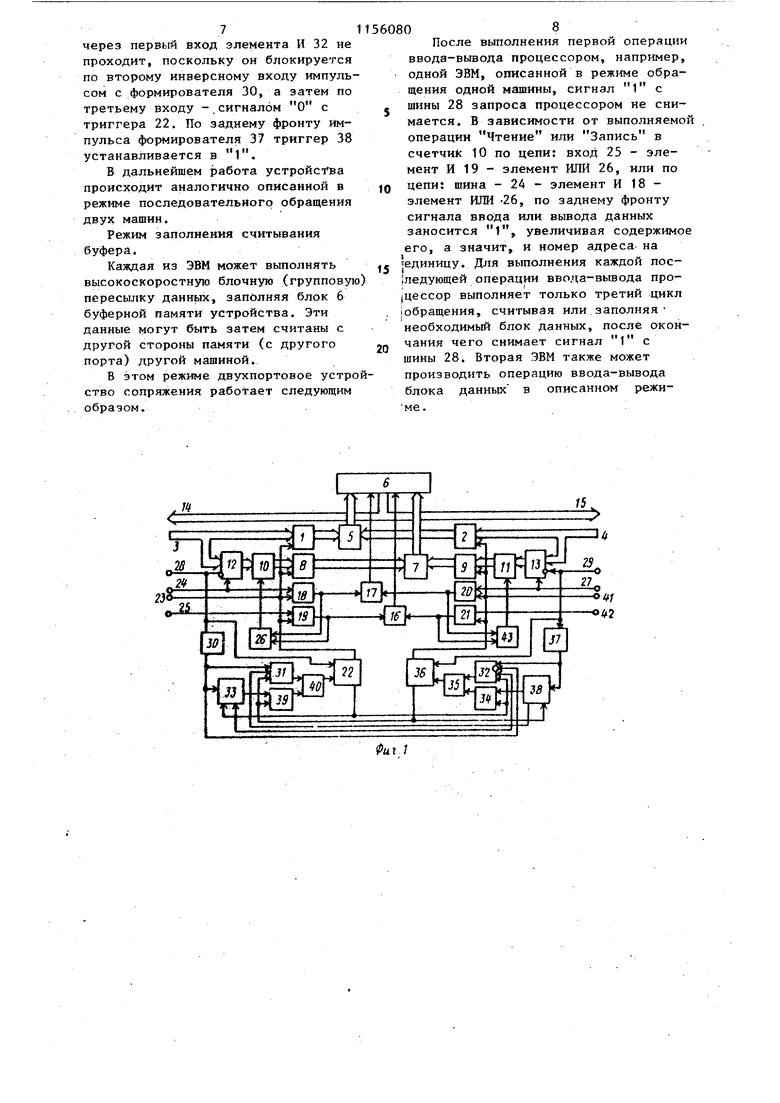

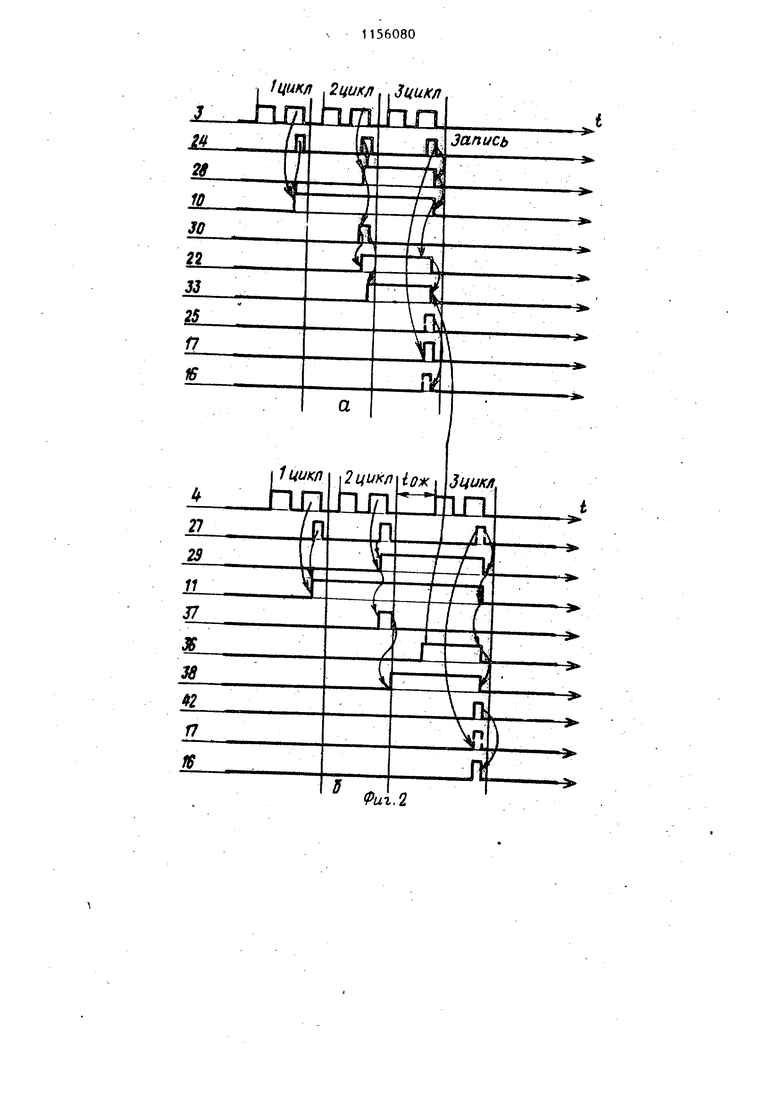

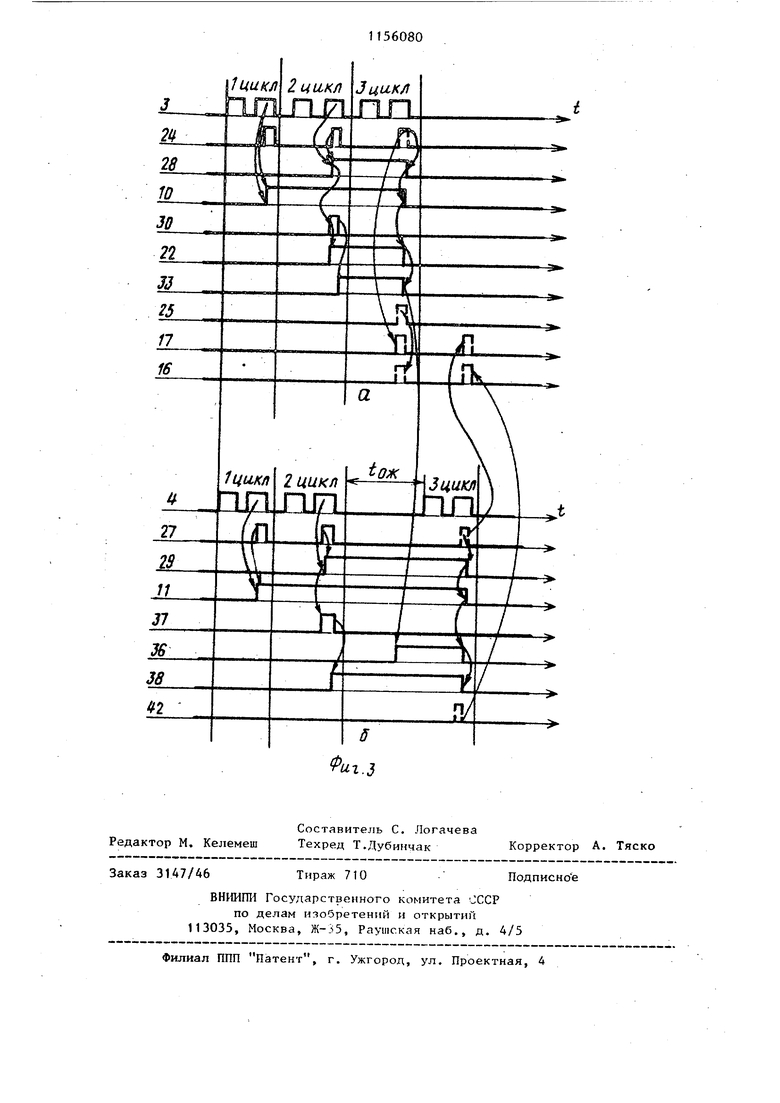

Изобретение относится к вь1числительной- технике, в частности к структурам дифровых вычислительных систем и может быть использовано при построении многопрограммных вычислительных систем, работающих в реальном масшта времени. Цель изобретения - повышение быстродействия вычислительной систем введением двухпортовых устройств сопряжения. На фиг. 1 показана схема предлагаемого двухпортового устройства сопряжения в вычислительной системе; на фиг. 2 - временные диаграммы работы двухпортового устройства сопряжения в вычислительной системе в режиме обращения одной машины и последовательного обращения двух вычислительньйс машин; на фиг. 3 то же, в режиме одновременного обращения двух вычислительных машин. Двухпортовое устройство сопряжени содержит элементы И 1 и 2 первой и второй групп, первые входы которых подключены соответственно к информационньм входам 3 и 4 устройства, а выходы - к входам элементов ИЛИ 5 первой группы, выходы которых соединены с инфориационными входами блока 6 буферной памяти, адресными входами соединенного с входами элементов ИЛИ 7 второй группы. Первые и вторые входы элементов ИЛИ 7 соединены соответственно с выходами элементов И 8 и 9 третьей и четвертой групп, первые входы которых соединены соответственно с выходами счетчиков 10 и 11, информационные входы которых . соединены соответственно с выходами элементов И 12 и 13 пятой и шестой групп, первые входы которых подключены соответственно к информационным входам устройства 3 и 4. Выход блока 6 подюпочен к информационным выходам устройства 14 и 15, а входы Чтение и Запись соответственно к выходам элементов ИЖ 16 и 17, первые и вторые входы которых подключены соответственно к выходам элементов И 18, 19 и 20, 21. Прямой выход триггера 22 подключен к вторым входам элементов И 1 и 8, к выходу 23 представления прерывания устройства и к первьм входам элементов И 18 и 19, к вторым входам которых подключены соответственно управляющие входы 24-и 25. Выходы элементов И 18 и 19 соединены соответственно с входами элемента ИЛИ 26, выход которого соединен с установочным входом счетчика 10, вторые входы элементов И 12 и 13 подключены соответственно к управля Ю1ЦИМ входам 24 и 27, а инверсные соответственно к запросным входам 28и 29. Вход 28 соединен с нулевым входо триггера 22, а через формирователь 30 - с первым входомэлемента И 31, с инверсным входом элемента И 32 и с единичным входом триггера 33, нулевой вход которого соединен с инверсным выходом триггера 22 и с первыми входами элементов И 32 и 34 вьЬсоды которых соединены соответственно с входами элемента И/Ш 35, подключенного выходом к единичному входу триггера 36, нулевой вход которого соединен с запросным входо 29устройства, а через формировател 37 импульса - с вторьм входом элеме та И 32 и единичным входом триггера 38, нулевой вход которого соединен с нулевьм выходом триггера 36, с вторым входом элемента И 31 и первьм входом элемента И 39, второй вход которого соединен с прямьм выходом триггера 33. Выходы элементов И 31 и 39 соеди нены с соответствующими входами эле мента ИЛИ 40, выход которого соединен с единичным выходом триггера 22 Третий вход элемента И 31 соединен инверсньм выходом триггера 38, прям выход которого соединен с вторьи входом элемента И -34. Инверсн1яй выход триггера 33 соед иен с третьим входом элемента И 32, .прямой выход триггера 36 соединен с вторыми входами элементов И 2 и 9, выходом 41 представления прерывания устройства и с первыми входами элементов И 20 и 21, вторые входы которых подключены соответственно к управляющим входам 27 и 42, а выходы к соответствующим входам элемента ИЛИ 43, выход которого соединен с установочным входом счетчика 11. Двухпортовое устройство сопряжени в вычислительной системе работает следующим образом. Любой цикл обращения, процессора ЭВМ начинается с адресной части выборки внешнего устройства, каким является двухпортовое устройство. После завершения адресной части цикл процессор выполняет прием или переда чу данных. Лля выполнения операций Чтение или Запись в блок 6 804 процессору необходимо выполнить три цикла обращения. В .зависимости от обращений вычислительных машин двухпортовое устройство сопряжения имеет несколько режгачов работы. Режим обращения одной машины (фиг. 2л). Этот режим характеризуется обращением к устройству одной ЭВМ на отрезке времени, равном времени выг полиения операции ввода-вывода процессором. Триггера 22, 33, 36 и 38 в исходном положении находятся в нулевом состоянии. Цепь их начальной установки на фиг. 1 не показана. В первом цикле процессор ЭВМ после адресации двухпортового устройства в адресной части помещает на вход 3 данные, представлякнцйе собой адрес ячейки блока 6, к которой необходимо обращаться, после чего устанавливается на входе 24 сигнал Вывод, означающий, что на линии 3 помещены данные. При этом на входе 28 запроса присутствует сигнал О. Данные через группу 12 элементов И записываются в счетчик. Этим завершается первый цикл обращения, при этом в счетчике 10 записан адрес ячейки блока 6, к необходимо обращаться. Во втором цикле обращения после адресной tacти на входе 28 появляется сигнал, блокир5 щий по инверсному входу элементы И 12 и занесение данных в счетчик 10. По переднему фронту сигнала запроса формирователь 30 вырабатывается импульс, по переднему фронту которого через первый вход элемента И 31 (так как на двух остальных входах присутствуют разрешающие сигналы) устанавли- ваотся в 1 триггер 22. С единичного выхода триггера 22 сигнал 1 поступает на выход 23, инфо «ируюв(ий процессор о том, что устройство готово Передавать или приню 1ать данные. По заднему фронту импульса формирователя 30 триггер 33 устанавливается в 1. В третьем цикле обращения процессор производит обращение к блоку 6 устройства по адресу, содержащемуся в счетчике 10. Операция, обращения происходит аналогично операции, описанной для первого цикла обращения. При этом, в случае операции 5М Запись, данные с линии 3, представляющие собой информацию, которую необходимо записать в блок 6, через группу 1 элементов И, на вторых входах которых присутствует разрешающий сигнал с триггера 22, и группу 5 элементов ИЛИ поступает сигнал на входные информационные шины блока 6 Группа 12 элементов И блокируется по второму инверсному входу сигналом с шины 28, адрес через группу 8 элементов И и группу 7 элементов ИЛИ поступает на адресные шииы блока 6, Сигнал с шины 24 через элементы И 18 и 17 поступает на управляющий вход Запись блока 6, в котором производится операция записи, выданной процессором информации по необходимому адресу. В случае операции Чтение данные на входе 3 не устанавливаются процессором, а на выходе 25 появляется сигнал, который через элементы И 19 и ИЛИ 16 поступает на управляющий вход Чтение блока 6, в котором происходит операция чтения информации по заданному адресу. Информация с выходных информационных шин блока поступает на линию 14, с которой при нимается процессором. После завершения процессором операции ввода-вывода с линии 25 снимается сигнал 1. По заднему фронту сигнала триггер 22 устанавливается в нулевое состояние. Режим последовательного обращени двух ЭВМ (фиг. 2а ,Б). Этот режим характеризуется после дoвaтeJlЬHЫм обращением к устройству двух ЭВМ на отрезке времени, равном времени выполнения операции вводавывода процессором. Например, одна ЭВМ производит операцию ввода-вывода с устройства. Во время этого вторая ЭВМ также обратилась к нему. В этом случае двухпортовое устройство работает следующим образом. Работа элементов устройства происходит аналогично описанной в режиме обращения одной машины, Первый адресный цикл обращения происходит аналогично описанному. При этом в счетчик 11 записывается адрес, по которому требуется обраще ние к блоку 6. Сигнал с шины 29 передним фронтом запустит формирователь 37. 0 Сигнал с формирователя 37 через элемент И 32 не пройдет, поскольку он блокирован по третьему входу сигналом О с нулевого выхода триггера 22 и по второму входу сигналом О с нулевого выхода триггера 33, который был установлен в единичное состояние задним фронтом импульса формирователя 30. Задним фронтом сигнала формирователя 37 триггер 38 установится в 1 и запретит по второму входу элемента И 31 установку триггера 22 в 1 при повторном запросе первой ЭВМ. Об окончании операции ввода-вывода первая ЭВМ сигнализирует снятие с линии 28 сигнала 1, по заднему фронту которого триггер 22 устанавливается в нулевое состояние и передним фронтом сигнала 1 с нулевого выхода устанавливает в О триггер 33 И через элемент И 34, на первом входе которого присутствует разрешающий сигнал с триггера 38, элемент ИЛИ 35 устанавливает в единичное состояние триггер 36, С единичного выхода триггера 36 сигнал поступает на шину 41, информирующий процессор второй ЭВМ о том, что устройство готово передавать или принимать данные. Процессор выполняет операцию вво/.а-вывода, по завершению которой с шины 29 снимается сигнал 1, задним фронтом которого триггер 36 устанавливается В нулевое состояние и устанавливает в состояние О триггер 38. Временная диаграмма работы двухпортового устройства и в режиме одновременного обращения к устройству двух ЭВМ показана на фиг. 3«, Б . Занесение адреса в счетчики-регисТры 10 и 11 происходит на первом цикле обращения машин аналогично описанному в режиме обращения одной машиньи Затем при появлении на шинах 28 и 29 сигналов 1 формирователи 30 и 37 формируют импульсы, передние фронта которых совпадают. По переднему фронту импульса формирователя 30 через элемент И 31, на двух остальных входах которого присутствуют разрешающие сигналы, и элемент ИЛИ 40 триггер 22 устанавливается в единичное состояние, а по заднему - в 1 устанавливается Триггер 33. Сигнал 1 с единичного выхода триггера 22 поступает на шину 23. Импульс формирователя 37

через первый вход злемента И 32 не проходит, поскольку он блокируется по второму инверсному входу импульсом с формирователя 30, а затем по третьему входу -.сигналом О с триггера 22. По заднему фронту импульса формирователя 37 триггер 38 устанавливается в 1.

В дальнейшем работа устройства происходит аналогично описанной в режиме последовательного обращения двух машин.

Режим заполнения считывания буфера.

Каждая из ЭВМ может выполнять высокоскоростную блочную (групповую пересылку данньпс, заполняя блок 6 буферной памяти устройства. Эти данные могут быть затем считаны с другой стороны памяти (с другого порта) другой машиной.

В этом режиме двухпортовое устроство сопряжения работает следующим образом.

После выполнения первой операции ввода-вывода процессором, например, одной ЭВМ, описанной в режиме обращения одной машины, сигнал 1 с шины 28 запроса процессором не снимается. В зависимости от выполняемой операции Чтение или Запись в счетчик 10 по цепи: вход 25 - элемент И 19 - элемент ИЛИ 26, или по цепи: шина - 24 - элемент И 18 элемент ИЛИ -26, по заднему фронту сигнала ввода или вывода данных заносится 1, увеличивая содержимое его, а значит, и номер адреса на единицу. Для выполнения каждой пос1

(ледующей операции ввода-вывода про|цессор выполняет только третий .цикл (Обращения, считывая или.заполняя необходимый блок данных, после окончания чего снимает сигнал 1 с шины 28. Вторая ЭВМ также может производить операцию ввода-вывода блока данных в описанном режиме.

15

| Многоканальное устройство для сопряжения источников сообщений с цифровой вычислительной машиной | 1980 |

|

SU941979A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения с общей маги-СТРАлью ВычиСлиТЕльНОй СиСТЕМы | 1979 |

|

SU809143A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-15—Публикация

1982-12-24—Подача