Изобретение относится к цифровой вычислительной технике и автоматике и может быть использовано при построении отказоустойчивых и гарантоспособных вычислительных систем, защищенных от ошибок, вызванных физическими дефектами и дефектами проектирования, на основе однотипных или разнообразных вычислителей, в которых возможно решение задач по нескольким альтернативным версиям.

Целью изобретения является повышение надежности устройства.

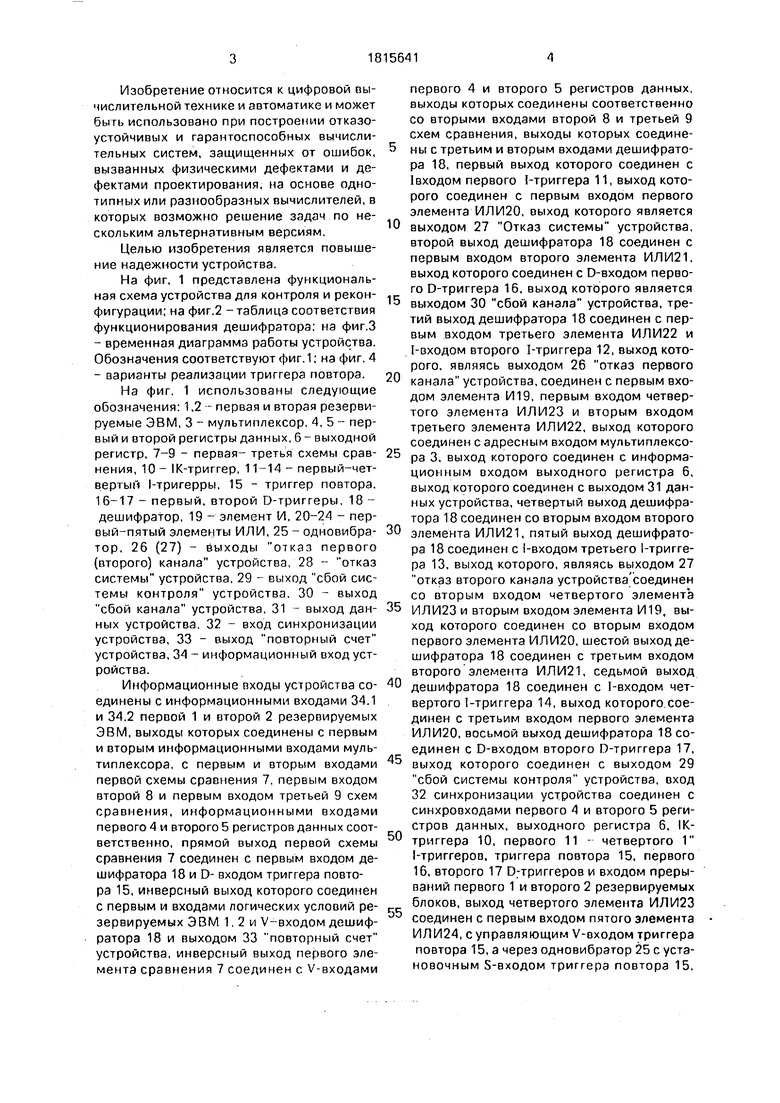

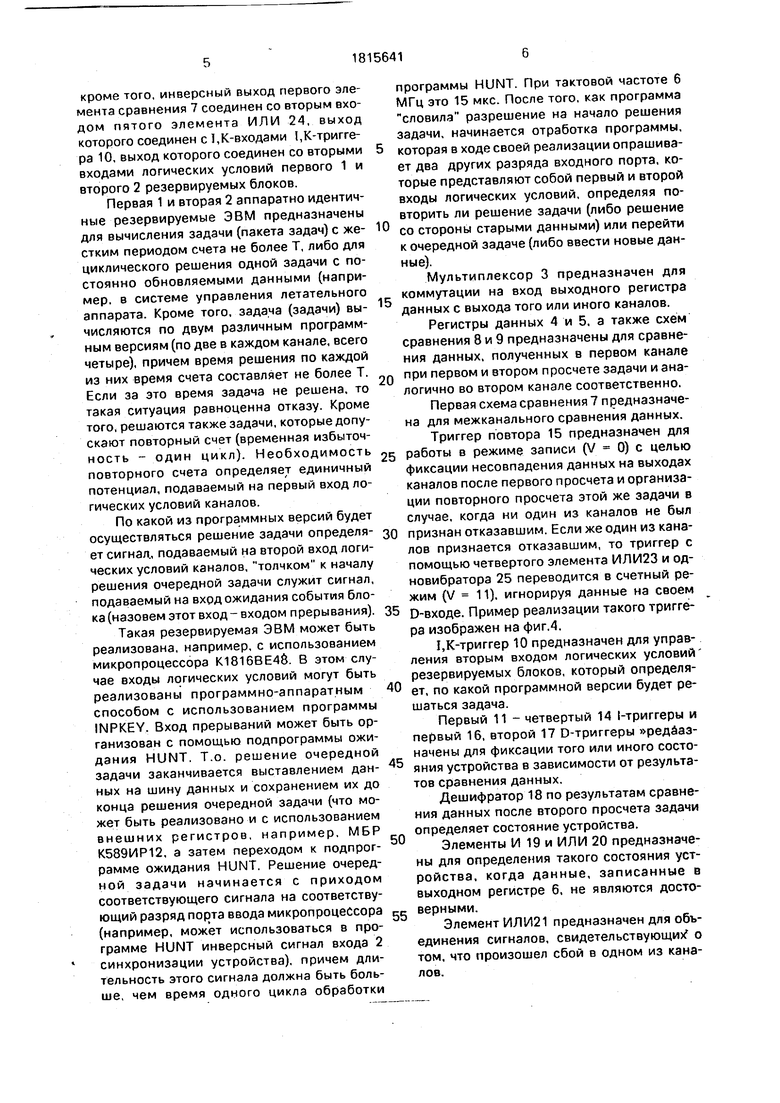

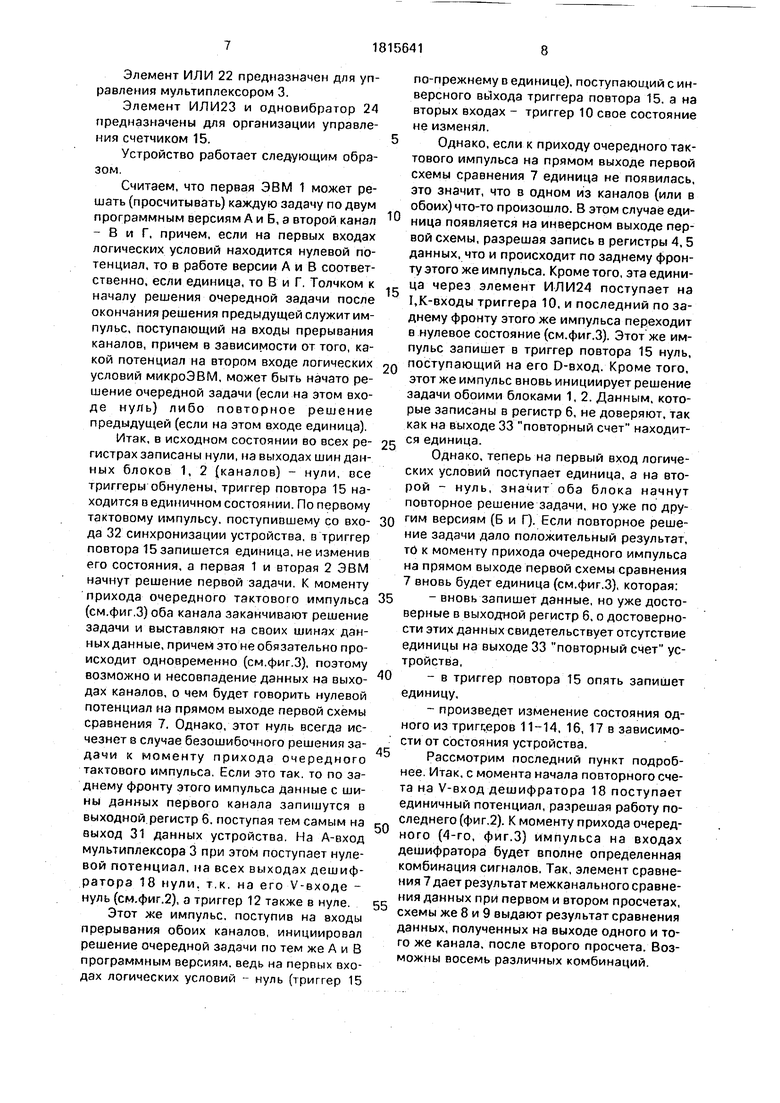

На фиг. 1 представлена функциональная схема устройства для контроля и реконфигурации; на фиг.2 - таблица соответствия функционирования дешифратора: на фиг.З

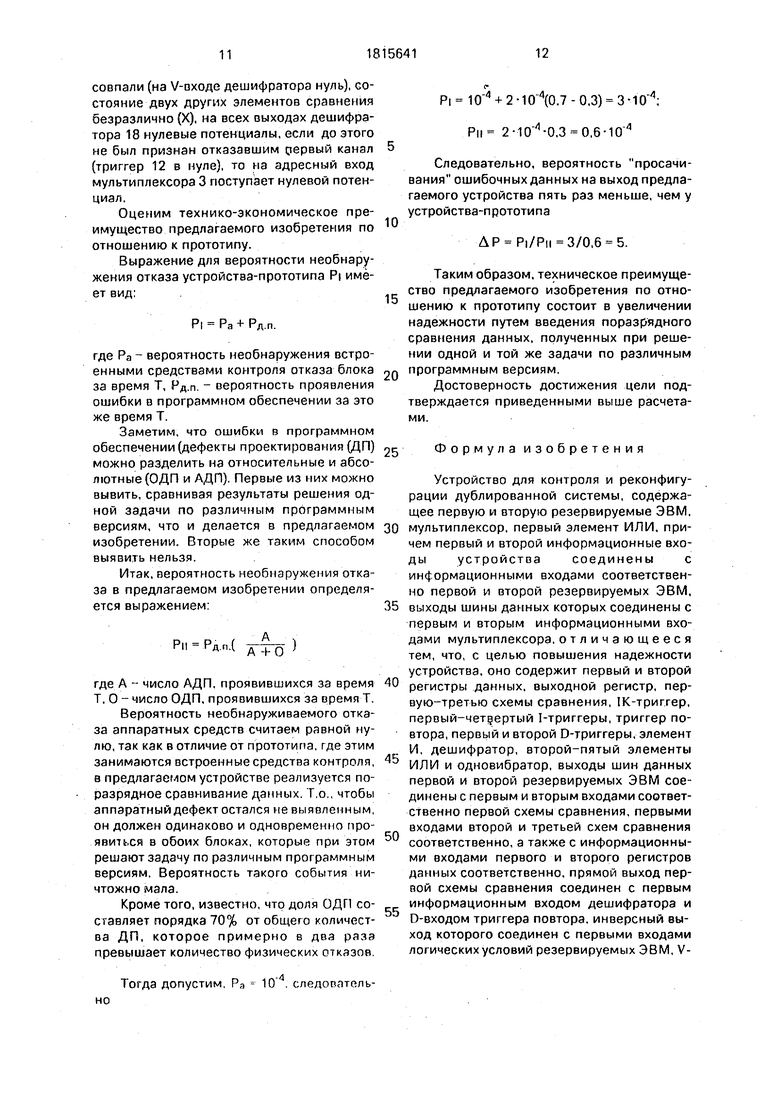

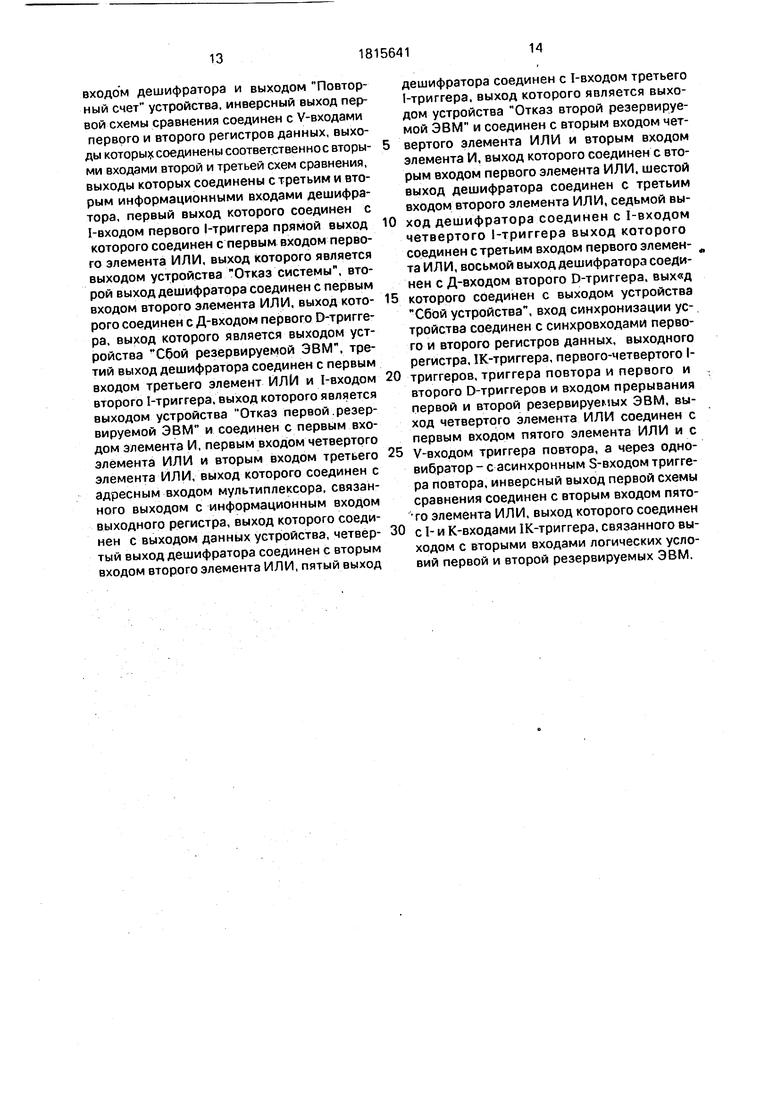

- временная диаграмма работы устройства. Обозначения соответствуют фиг. 1; на фиг. 4

- варианты реализации триггера повтора.

На фиг. 1 использованы следующие обозначения: 1,2 - первая и вторая резервируемые ЭВМ, 3 - мультиплексор, 4, 5 - первый и второй регистры данных, б - выходной регистр, 7-9 - первая- третья схемы сравнения, 10 - 1К-триггер, 11-14 - первый-чет- вертым 1-тригерры, 15 - триггер повтора, 16-17 - первый, второй D-триггеры, 18 - дешифратор, 19 - элемент И, 20-24 - пер- вый-пятый элементы ИЛИ, 25 - одновибра- тор, 26 (27) - выходы отказ первого (второго) канала устройства, 28 - отказ системы устройства, 29 - выход сбой системы контроля устройства, 30 - выход сбой канала устройства, 31 - выход данных устройства, 32 - вход синхронизации устройства, 33 - выход повторный счет устройства, 34 - информационный вход устройства.

Информационные входы устройства соединены с информационными входами 34.1 и 34.2 первой 1 и второй 2 резервируемых ЭВМ, выходы которых соединены с первым и вторым информационными входами мультиплексора, с первым и вторым входами первой схемы сравнения 7, первым входом второй 8 и первым входом третьей 9 схем сравнения, информационными входами первого 4 и второго 5 регистров данных соответственно, прямой выход первой схемы сравнения 7 соединен с первым входом дешифратора 18 и D- входом триггера повтора 15, инверсный выход которого соединен с первым и входами логических условий резервируемых ЭВМ 1, 2 и V-входом дешифратора 18 и выходом 33 повторный счет устройства, инверсный выход первого элемента сравнения 7 соединен с V-входами

первого 4 и второго 5 регистров данных, выходы которых соединены соответственно со вторыми входами второй 8 и третьей 9 схем сравнения, выходы которых соединены с третьим и вторым входами дешифратора 18, первый выход которого соединен с 1входом первого 1-триггера 11, выход которого соединен с первым входом первого элемента ИЛИ20, выход которого является

выходом 27 Отказ системы устройства, второй выход дешифратора 18 соединен с первым входом второго элемента ИЛИ21, выход которого соединен с D-входом первого D-триггера 16, выход которого является

выходом 30 сбой канала устройства, третий выход дешифратора 18 соединен с первым входом третьего элемента ИЛИ22 и I-входом второго 1-триггера 12, выход которого, являясь выходом 26 отказ первого

канала устройства, соединен с первым входом элемента И19, первым входом четвертого элемента ИЛИ23 и вторым входом третьего элемента ИЛИ22, выход которого соединен с адресным входом мультиплексора 3, выход которого соединен с информационным входом выходного регистра 6, выход которого соединен с выходом 31 данных устройства, четвертый выход дешифратора 18 соединен со вторым входом второго

элемента ИЛИ21. пятый выход дешифратора 18 соединен с I-входом третьего 1-триггера 13, выход которого, являясь выходом 27 отказ второго канала устройства соединен со вторым входом четвертого элемента

ИЛИ23 и вторым входом элемента И19, выход которого соединен со вторым входом первого элемента ИЛИ20, шестой выход дешифратора 18 соединен с третьим входом второго элемента ИЛИ21, седьмой выход

дешифратора 18 соединен с I-входом четвертого 1-триггера 14, выход которого.соединен с третьим входом первого элемента ИЛИ20, восьмой выход дешифратора соединен с D-входом второго D-триггера 17,

выход которого соединен с выходом 29 сбой системы контроля устройства, вход 32 синхронизации устройства соединен с синхровходами первого 4 и второго 5 регистров данных, выходного регистра 6, IK- триггера 10, первого 11 - четвертого 1 1-триггеров, триггера повтора 15, первого 16, второго 17 D.-триггеров и входом прерываний первого 1 и второго 2 резервируемых блоков, выход четвертого элемента ИЛИ23

соединен с первым входом пятого элемента ИЛИ24, с управляющим V-входом триггера повтора 15, а через одновибрэтор 25 с установочным S-входом триггера повтора 15,

кроме того, инверсный выход первого элемента сравнения 7 соединен со вторым входом пятого элемента ИЛИ 24, выход которого соединен с 1,К-входами 1,К-тригге- ра 10, выход которого соединен со вторыми входами логических условий первого 1 и второго 2 резервируемых блоков.

Первая 1 и вторая 2 аппаратно идентичные резервируемые ЭВМ предназначены для вычисления задачи (пакета задач) с жестким периодом счета не более Т, либо для циклического решения одной задачи с постоянно обновляемыми данными (например, в системе управления летательного аппарата. Кроме того, задача (задачи) вычисляются по двум различным программным версиям (по две в каждом канале, всего четыре), причем время решения по каждой из них время счета составляет не более Т. Если за это время задача не решена, то такая ситуация равноценна отказу. Кроме того, решаются также задачи, которые допускают повторный счет (временная избыточность - один цикл). Необходимость повторного счета определяет единичный потенциал, подаваемый на первый вход логических условий каналов.

По какой из программных версий будет осуществляться решение задачи определяет сигнал., подаваемый на второй вход логических условий каналов, толчком к началу решения очередной задачи служит сигнал, подаваемый на вход ожидания события блока (назовем этот вход-входом прерывания).

Такая резервируемая ЭВМ может быть реализована, например, с использованием микропроцессора К1816ВЕ48. В этом случае входы логических условий могут быть реализованы программно-аппаратным способом с использованием программы INPKEY, Вход прерываний может быть организован с помощью подпрограммы ожидания HUNT. Т.о. решение очередной задачи заканчивается выставлением данных на шину данных и сохранением их до конца решения очередной задачи (что может быть реализовано и с использованием внешних регистров, например, МБР К589ИР12, а затем переходом к подпрограмме ожидания HUNT. Решение очередной задачи начинается с приходом соответствующего сигнала на соответствующий разряд порта ввода микропроцессора (например, может использоваться в программе HUNT инверсный сигнал входа 2 синхронизации устройства), причем длительность этого сигнала должна быть больше, чем время одного цикла обработки

0

5

0

5

0

5

0

5

0

5

программы HUNT. При тактовой частоте б МГц это 15 мкс. После того, как программа словила разрешение на начало решения задачи, начинается отработка программы, которая в ходе своей реализации опрашивает два других разряда входного порта, которые представляют собой первый и второй входы логических условий, определяя повторить ли решение задачи (либо решение со стороны старыми данными) или перейти к очередной задаче (либо ввести новые данные).

Мультиплексор 3 предназначен для коммутации на вход выходного регистра данных с выхода того или иного каналов.

Регистры данных 4 и 5, а также схем сравнения 8 и 9 предназначены для сравнения данных, полученных в первом канале при первом и втором просчете задачи и аналогично во втором канале соответственно.

Первая схема сравнения 7 предназначена для межканального сравнения данных.

Триггер повтора 15 предназначен для работы в режиме записи (V 0) с целью фиксации несовпадения данных на выходах каналов после первого просчета и организации повторного просчета этой же задачи в случае, когда ни один из каналов не был признан отказавшим. Если же один из каналов признается отказавшим, то триггер с помощью четвертого элемента ИЛИ23 и од- новибратора 25 переводится в счетный режим (V 11). игнорируя данные на своем D-входе. Пример реализации такого триггера изображен на фиг.4.

1,К-триггер 10 предназначен для управления вторым входом логических условий резервируемых блоков, который определяет, по какой программной версии будет решаться задача.

Первый 11 - четвертый 14 1-триггеры и первый 16, второй 17 D-триггеры редааз- начены для фиксации того или иного состояния устройства в зависимости от результатов сравнения данных.

Дешифратор 18 по результатам сравнения данных после второго просчета задачи определяет состояние устройства.

Элементы И 19 и ИЛИ 20 предназначены для определения такого состояния устройства, когда данные, записанные в выходном регистре 6, не являются достоверными.

Элемент ИЛИ21 предназначен для объединения сигналов, свидетельствующих о том, что произошел сбой в одном из каналов.

Элемент ИЛИ 22 предназначен для управления мультиплексором 3.

Элемент ИЛИ23 и одновибратор 24 предназначены для организации управления счетчиком 15.

Устройство работает следующим образом,

Считаем, что первая ЭВМ 1 может решать (просчитывать) каждую задачу по двум программным версиям А и Б, а второй канал - 8 и Г, причем, если на первых входах логических условий находится нулевой потенциал, то в работе версии А и В соответственно, если единица, то В и Г. Толчком к началу решения очередной задачи после окончания решения предыдущей служит импульс, поступающий на входы прерывания каналов, причем в зависимости от того, какой потенциал на втором входе логических условий микроЭВМ, может быть начато решение очередной задачи (если на этом входе нуль) либо повторное решение предыдущей (если на этом входе единица).

Итак, в исходном состоянии во всех регистрах записаны нули, на выходах шин данных блоков 1, 2 (каналов) - нули, все триггеры обнулены, триггер повтора 15 находится в единичном состоянии. По первому тактовому импульсу, поступившему со входа 32 синхронизации устройства, в триггер повтора 15 запишется единица, не изменив его состояния, а первая 1 и вторая 2 ЭВМ начнут решение первой задачи. К моменту прихода очередного тактового импульса (см.фиг.3) оба канала заканчивают решение задачи и выставляют на своих шинах данных данные, причем это не обязательно происходит одновременно (см.фиг.3), поэтому возможно и несовпадение данных на выходах каналов, о чем будет говорить нулевой потенциал на прямом выходе первой схемы сравнения 7. Однако, этот нуль всегда исчезнет в случае безошибочного решения задачи к моменту прихода очередного тактового импульса. Если это так. то по заднему фронту этого импульса данные с шины данных первого канала запишутся в выходной.регистр 6. поступая тем самым на выход 31 данных устройства. На А-вход мультиплексора 3 при этом поступает нулевой потенциал, на всех выходах дешифратора 18 нули. т.к. на его V-входе - нуль (см.фиг.2), а триггер 12 также в нуле.

Этот же импульс, поступив на входы прерывания обоих каналов, инициировал решение очередной задачи по тем же А и В программным версиям, ведь на первых входах логических условий - нуль (триггер 15

0

5

0

5

0

5

0

5

0

5

по-прежнему в единице), поступающий с инверсного выхода триггера повтора 15, а на вторых входах - триггер 10 свое состояние не изменял.

Однако, если к приходу очередного тактового импульса на прямом выходе первой схемы сравнения 7 единица не появилась, это значит, что в одном из каналов (или в обоих) что-то произошло. В этом случае единица появляется на инверсном выходе первой схемы, разрешая запись в регистры 4, 5 данных, что и происходит по заднему фронту этого же импульса. Кроме того, эта единица через элемент ИЛИ24 поступает на 1,К-входы триггера 10, и последний по заднему фронту этого же импульса переходит в нулевое состояние (см.фиг.З). Этот же импульс запишет в триггер повтора 15 нуль, поступающий на его D-вход. Кроме того, этот же импульс вновь инициирует решение задачи обоими блоками 1, 2. Данным, которые записаны в регистр 6, не доверяют, так как на выходе 33 повторный счет находится единица.

Однако, теперь на первый вход логических условий поступает единица, а на второй - нуль, значит оба блока начнут повторное решение задачи, но уже по другим версиям (Б и 0- Если повторное решение задачи дало положительный результат, то к моменту прихода очередного импульса на прямом выходе первой схемы сравнения 7 вновь будет единица (см.фиг.З), которая:

- вновь запишет данные, но уже достоверные в выходной регистр 6, о достоверности этих данных свидетельствует отсутствие единицы на выходе 33 повторный счет устройства,

- в триггер повтора 15 опять запишет единицу,

- произведет изменение состояния одного из триггеров 11-14, 16, 17 в зависимости от состояния устройства.

Рассмотрим последний пункт подробнее. Итак, с момента начала повторного счета на V-вход дешифратора 18 поступает единичный потенциал, разрешая работу последнего (фиг,2). К моменту прихода очередного (4-го, фиг.З) импульса на входах дешифратора будет вполне определенная комбинация сигналов, Так, элемент сравнения 7 дает результат межканального сравнения данных при первом и втором просчетах, схемы же 8 и 9 выдают результат сравнения данных, полученных на выходе одного и того же канала, после второго просчета. Возможны восемь различных комбинаций.

Первая. Все три элемента сравнения дали отрицательный результат. Невозможно определить достоверна ли информация хотя бы в одном из каналов. Такая ситуация расценивается как отказ системы. Очередной тактовый импульс переводит триггер 11 в единичное состояние, на его вход поступает единица с выхода - 0 дешифратора. Единица с выхода триггера 11, пройдя через элемент ИЛИ20, информирует пользователя об отказе системы, поступая на выход 28.

Вторая. Данные ни в одном из каналов между собой не совпали, но второй счет дал положительный результат при межканальном сравнении. Значит при первом просчете в обоих каналах возникнет сбой. Единица, появившаяся на выходе 1, дешифратора 18, поступит через элемент ИЛИ21 на D-вход триггера 16, выход которого является выходом 30 сбой канала устройства, - информируется пользователь. Однако, этот сигнал может быть вновь снят, если при решении очередной задачи такой ситуации не возникнет, тогда на выходе 1 дешифратора вновь будет нуль к моменту прихода синхроимпульса.

Третья. Межканальное сравнение оба раза дало отрицательный результат, кроме того, первый канал выдал данные, которые не совпали между собой. Следовательно отказал первый канал 1, что и явилось причиной несовпадения данных при первом и втором просчетах. В этом случае к моменту прихода очередного импульса (импульс 6. фиг.З) единица с выхода 2 дешифратора 18, пройдя через элемент ИЛИ22, поступает на адресный вход мультиплексора 3. коммутируя тем самым на информационный вход выходного регистра 6 данные с выхода второго канала 2. По очередному импульсу эти данные запишутся в регистр 6. Этот же импульс переведет в единичное состояние триггер 12, на 1-вход которого поступает единица с выхода 2 дешифратора. Единица с выхода триггера 12 поступает на выход 26 отказ первого канала устройства, информируя пользователя. Кроме того, эта единица постоянно будет поступать на адресный вход мультиплексора 3 через элемент ИЛИ22, так как данные теперь могут поступать только со второго канала. Единица с выхода элемента ИЛИ23 поступает на вход одновибратора, который вырабатывает (через время т после очередного синхроимпульса, определяемого временами задержки триггера 12 и элемента ИЛИ23) одиночный импульс, который устанавливает триггер повтора 15 в единицу (ведь он остался после синхроимпульса в нуле - второй просчет также не дал совпадения данных на входе элемента сравнения 7) (см.фиг.З). Кроме того, эта же единица с выхода ИЛИ23

поступает на V-вход триггера повтора 15, переводя его из режима записи в режим счета, а пройдя через элемент ИЛИ 24, поступает на 1,К-входы триггера 10, который теперь будет изменять свое состояние на

противоположное по каждому синхроимпульсу (как и триггер повтора 15), ведь теперь для выдачи достоверных данных,, необходимо каждую задачу просчитывать два раза по двум различным программным

версиям, что теперь и будут обеспечивать триггер повтора 15 и триггер 10 до тех пор, пока не откажет и другой канал.

Четвертая, шестая. Эти две ситуации идентичны второй с той лишь разницей, что

сбой при первом просчете задачи произошел в одном из каналов (см. фиг.2).

Пятая. Аналогична третьей, отличие состоит лишь в том, что сигнал на адресном входе мультиплексора сохраняет свой потенциал.

Седьмая, Такая комбинация результатов сравнения также оценивается как отказ системы в целом, так как неясны причины межканального несовпадения данных после обоих просчетов одной задачи при том. что локальное сравнение дало положительный результат. Причин может быть несколько: константная неисправность (например, такой отказ шины данных блока, при котором на ней только нули) ЭВМ 1. 2, или отказ первого схемы сравнения 7, или отказы всех элементов сравнения. В любом из этих случаев дальнейшее функционирование устройства не обеспечивает выдачу достоверных данных. Такая ситуация фиксируется очередным тактовым импульсом в триггере 14, единица с выхода которого через элемент ИЛЙ20 поступает на выход 28

отказ системы устройства.

Восьмая. В этом случае, очевидно, произошел сбой в системе контроля, т.е. схема 7 при сравнении результатов версий А и В (или Б и Г) дал отрицательный результат,

хотя после второго счета задачи все три схемы сравнения 7, 8, 9 дали положительный результат, Эта ситуация также фиксируется D-триггером 17 по очередному тактовому импульсу. Если при решении следующей задачи эта ситуация не повторится, то этот триггер обнулится.

Девятая. Этот случай соответствует ситуации, когда при первом решении задачи данные на выходах резервируемых блоков

совпали (на V-входе дешифратора нуль), состояние двух других элементов сравнения безразлично (X), на всех выходах дешифратора 18 нулевые потенциалы, если до этого не был признан отказавшим первый канал (триггер 12 в нуле), то на адресный вход мультиплексора 3 поступает нулевой потенциал.

Оценим технико-экономическое преимущество предлагаемого изобретения по отношению к прототипу.

Выражение для вероятности необнаружения отказа устройства-прототипа PI имеет вид:

Pi Pa + Рд.п.

где Ра - вероятность необнаружения встроенными средствами контроля отказа блока за время Т, Рд.п. - вероятность проявления ошибки в программном обеспечении за это же время Т.

Заметим, что ошибки в программном обеспечении (дефекты проектирования (ДП) можно разделить на относительные и абсолютные (ОДП и АДП). Первые из них можно вывить, сравнивая результаты решения одной задачи по различным программным версиям, что и делается в предлагаемом изобретении. Вторые же таким способом выявить нельзя.

Итак, вероятность необнаружения отказа в предлагаемом изобретении определяется выражением:

Pll Рд.п.(

А

А +0

)

где А - число АДП, проявившихся за время Т. О - число ОДП, проявившихся за время Т.

Вероятность необнаруживаемого отказа аппаратных средств считаем равной нулю, так как в отличие от прототипа, где этим занимаются встроенные средства контроля, в предлагаемом устройстве реализуется поразрядное сравнивание данных. Т.о., чтобы аппаратный дефект остался не выявленным, он должен одинаково и одновременно проявиться в обоих блоках, которые при этом решают задачу по различным программным версиям. Вероятность такого события ничтожно мала.

Кроме того, известно, что доля ОДП составляет порядка 70% от общего количества ДП, которое примерно в два раза превышает количество физических отказов.

р

v4

v4,

5

Q

c о

5

0

5 0

5

Pi + 2 (0,7 - 0,3) 3 -.10Л Рц 2 -0,3 0,6-10

Следовательно, вероятность просачивания ошибочных данных на выход предлагаемого устройства пять раз меньше, чем у устройства-п рототи па

ДР Р|/Рц 3/0,6 5.

Таким образом, техническое преимущество предлагаемого изобретения по отношению к прототипу состоит в увеличении надежности путем введения поразрядного сравнения данных, полученных при решении одной и той же задачи по различным программным версиям.

Достоверность достижения цели подтверждается приведенными выше расчетами.

Формула изобретения

Устройство для контроля и реконфигурации дублированной системы, содержащее первую и вторую резервируемые ЭВМ, мультиплексор, первый элемент ИЛИ. причем первый и второй информационные входы устройства соединены с информационными входами соответственно первой и второй резервируемых ЭВМ, выходы шины данных которых соединены с первым и вторым информационными входами мультиплексора, отличающееся тем, что, с целью повышения надежности устройства, оно содержит первый и второй регистры данных, выходной регистр, пер- вую-третью схемы сравнения, 1К-триггер, первый-четдертый I-триггеры, триггер повтора, первый и второй D-триггеры, элемент И, дешифратор, второй-пятый элементы ИЛИ и одновибратор, выходы шин данных первой и второй резервируемых ЭВМ соединены с первым и вторым входами соответственно первой схемы сравнения, первыми входами второй и третьей схем сравнения соответственно, а также с информационными входами первого и второго регистров данных соответственно, прямой выход первой схемы сравнения соединен с первым информационным входом дешифратора и D-входом триггера повтора, инверсный выход которого соединен с первыми входами логических условий резервируемых ЭВМ, V

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и реконфигурации дублированной системы | 1991 |

|

SU1807489A1 |

| Резервированное устройство | 1991 |

|

SU1833877A1 |

| Устройство для коррекции ошибок вычислительного процесса | 1991 |

|

SU1807487A1 |

| Устройство для реконфигурации резервируемых блоков | 1990 |

|

SU1797121A1 |

| Устройство для оперативной реконфигурации резервированной системы | 1990 |

|

SU1727125A1 |

| Устройство для контроля и реконфигурации резервируемых блоков | 1990 |

|

SU1800456A1 |

| Четырехканальная резервированная система | 1990 |

|

SU1746383A1 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| Резервированная система | 1982 |

|

SU1089771A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

Использование: в цифровых отказоустойчивых структурах. Сущность: устройство содержит: 2 резервируемых ЭВМ (1. 2), 1 мультиплексор (3), 2 регистра данных (4, 5), 1 выходной регистр (6), 3 схемы сравнения (7, 8, 9). 4 1-триггера(11. 12,13, 14). 2 D-триг- гера (16, 17), 1 триггер повтора (15), 1 IK- триггер(Ю), 1 дешифратор (18), 1 элемент И

,-4

Тогда допустим, Ра 10 . следовательвходом дешифратора и выходом Повторный счет устройства, инверсный выход первой схемы сравнения соединен с V-входами первого и второго регистров данных, выходы которых соединены соответственно с вторы- ми входами второй и третьей схем сравнения, выходы которых соединены с третьим и вторым информационными входами дешифратора, первый выход которого соединен с 1-входом первого 1-триггера прямой выход которого соединен с первым входом первого элемента ИЛИ, выход которого является выходом устройства Отказ системы, второй выход дешифратора соединен с первым входом второго элемента ИЛИ, выход кото- рого соединен с Д-входом первого D-тригге- ра, выход которого является выходом устройства Сбой резервируемой ЭВМ, третий выход дешифратора соединен с первым входом третьего элемент ИЛИ и 1-входом второго 1-триггера. выход которого является выходом устройства Отказ первой.резервируемой ЭВМ и соединен с первым входом элемента И, первым входом четвертого элемента ИЛИ и вторым входом третьего элемента ИЛИ, выход которого соединен с адресным входом мультиплексора, связанного выходом с информационным входом выходного регистра, выход которого соединен с выходом данных устройства, четвер- тый выход дешифратора соединен с вторым входом второго элемента ИЛИ, пятый выход

дешифратора соединен с 1-входом третьего 1-триггера, выход которого является выходом устройства Отказ второй резервируемой ЭВМ и соединен с вторым входом четвертого элемента ИЛИ и вторым входом элемента И, выход которого соединен с вторым входом первого элемента ИЛИ. шестой выход дешифратора соединен с третьим входом второго элемента ИЛИ, седьмой выход дешифратора соединен с 1-входом четвертого 1-триггера выход которого соединен с третьим входом первого элемента ИЛИ, восьмой выход дешифратора соединен с Д-входом второго D-триггера. вых«д которого соединен с выходом устройства Сбой устройства, вход синхронизации устройства соединен с синхровходами первого и второго регистров данных, выходного регистра, 1К-триггера, первого-четвертого I- триггеров, триггера повтора и первого и второго D-триггеров и входом прерывания первой и второй резервируемых ЭВМ, выход четвертого элемента ИЛИ соединен с первым входом пятого элемента ИЛИ и с V-входом триггера повтора, а через одно- вибратор - с асинхронным S-входом триггера повтора, инверсный выход первой схемы сравнения соединен с вторым входом пято- то элемента ИЛИ, выход которого соединен с I- и К-входами IK-триггера, связанного выходом с вторыми входами логических условий первой и второй резервируемых ЭВМ.

Фиг. Z

| Каган Б.М. | |||

| Мкртумян И.Б | |||

| Основы эксплуатации ЭВМ | |||

| М.: Энергоиздат | |||

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

| Паровозный золотник (байпас) | 1921 |

|

SU153A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для контроля вычислительных машин | 1986 |

|

SU1390612A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

| Лихонинский В.Г | |||

| Организация сдвоенного дублирования при вычислении логических функций на микроЭВМ, - Приборы и системы управления | |||

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1993-05-15—Публикация

1990-12-04—Подача