Предлагаемое устройство относится к области автоматики и вычислительной техники и может быть использовано в высоконадежных вычислительных устройствах.

Цель изобретения - повышение достоверности выходной информации вычислительного модуля.

Поставленная цель достигается тем, что в устройство для коррекции ошибок вычислительного модуля, содержащее вычислительный модуль, первый регистр результата, дешифратор, первую схему сравнения, мультиплексор. - причем выход данных вычислительного модуля соединен с информационным входом первого регистра

результата, выход которого соединен с нулевым информационным входом мультиплексора.а также с первым входом первой схемы сравнения, кроме того, нулевой выход дешифратора соединен с управляющим входом первого регистра результата, дополнительно введены регистр данных, регистр адреса, второй и третий регистры результатов, выходной регистр, вторая и третья схемы сравнения, триггер отказа, триггер управления, счетчик, одновибратор, с первого по четвертый элементы ИЛИ. с первого по пятый элементы И, блок магистральных элементов, причем вход данных устройства соединен с информационным входом региО

а

00

етра данных, выход которого соединен с входом магистрального элемента, выход которого соединен с входом-выходом вычислительного модуля, вход адреса устройства соединен с информационным входом регистра адреса, выход которого соединен с младшими разрядами адресного входа вычислительного модуля, выход Чтение которого соединен с управляющим входом магистрального элемента; вход пуска устройства соединен с первым входом первого и второго элемента ИЛИ, выход первого элемента ИЛИ соединен с синхровходами регистров данных и адреса, а также с входом первого элемента И, выход второго элемента J/ШИ соединен с входом Сброс вычислительного модуля, синхровходом выходного регистра, а также с°синхровходом триггера отказа, инверсный выход триггера отказа соединен с первым входом второго элемента И, второй вход которого является входом синхронизации устройст- аа, а выход соединен с входом синхронизации вычислительного модуля, выход Запись которого соединен с синхровходами первого-третьего регистров результатов, триггера управления, счетным входом счетчика и входом одновибратора, выход которого соединен со вторыми входами первого и второго элементов ИЛИ, первый и второй выходы счетчика соединены со стар1 шими разрядами адресного входа вычислительного модуля, первым и вторым входами дешифратора, нулевой выход которого также соединен с нулевым входом триггера управления и со вторыми управляющими входами регистров данных и адреса, первый выход дешифратора соединен с управляющим входом второго регистра результата. второй выход дешифратора соединен с управляющими входом третьего регистра результата и единичным входом триггера управления, выход которого соединен с первыми входами третьего-пятого элементов И, вторые входы четвертого и пятого элементов И соединены с выходами второй и третьей схем сравнения, выход первой схемы сравнения соединен с первым входом третьего элемента ИЛИ, а также с нулевым управляющим входом мультиплексора, выход четвертого элемента И соединен со вторым и первым входами третьего и четвертого элементов ИЛИ соответственно, а выход пятого элемента И - с третьим и вторым входами третьего и четвертого элементов ИЛИ соответственно, выход четвертого элемента ИЛИ соединен с первым управляющим входом мультиплексора, выход которого соединен с информационным входом выходного регистра, выход третьего

элемента ИЛИ соединен с выходом Норма устройства, а также с управляющими входами данных регистра адреса, выходного регистра и вторыми входами первого и

третьего элементов И, выход третьего элемента И соединен с единичным входом триггера отказа, выход которого является выходом сигнала Не норма устройства, выход первого элемента И соединен с нулевым входом счетчика, выход данных вычислительного модуля соединен с информационными входами второго и третьего регистров результатов, выход второго регистра результатов соединен с первым информационным входом .мультиплексора и вторым входом первой схемы сравнения, выход третьего регистра результата соединен с первым входом второй схемы сравнения, второй вход которой

соединен с выходом первого регистра результата, а первый и второй входы третьей схемы сравнения соединены с выходами второго и третьего регистров результатов соответственно, выход третьего регистра

результатов соединен с вторым информационным входом мультиплексора.

Сущность изобретения состоит в увеличении надежности устройства, достоверности выдаваемой информации путем

коррекции ошибок вычислительного процесса, вызванных сбоями и ошибками, втом числе программного обеспечения, методом двух- или трехкратного решения одной задачи по двум (трем) различным альтернативным программным версиям, разнесенным последовательно во времени, с последующим сравнением между собой полученных результатов. Достоверным считается результат, сравнимый в двух программных

версиях.

Изобретение реализуется путем введения следующих новых элементов и связей.

Введение двух дополнительных (второй и третьей) схем сравнения и обусловленных ими связей позволяет реализовать сравнение между собой трех результатов вычислений в различных сочетаниях для определения достоверного результата. Введение регистра данных и регистра адреса и обусловленных ими связей позволяет запомнить исходные данные и начальный адрес микропрограммы для двух-, трехкратной ее реализации. Введение дополнительно .второго и третьего регистров результатов позволяет записывать и хранить результаты вычислений альтернативных программных версий для последующей организации их сравнения и выдачи сравнимого результата.

Введение выходного регистра и обусловленных им связей позволяет записывать и хранить достоверный результат вычислений для его последующего использования в других устройствах.

Введение счетчика и обусловленных им связей позволяет осуществлять подсчет номеров вычисляемых программных версий для модификации старших разрядов начального адреса очередной версии и управление дешифратором..

Введение одновибратора и обусловленных им связей позволяет осуществлять синхронизацию работы вычислительного модуля.

Введение триггера отказа и обусловленных им связей позволяет фиксировать сигнал отказа на выходеустройства, а также для организации остановки вычислительного процесса при этом.

Введение триггера управления и обусловленных им связей позволяет осуществлять управления выдачей сигналов .сравнения из второй и третьей схем сравнения с помощью четвертого, пятого элементов И для предотвращения преждевременного формирования сигнала норма при сравнении нулевой информации (старой) в регистрах результатов.

Введение первого, второго элементов ИЛИ и обусловленных ими связей позволяет осуществлять синхронизацию совместной работы регистров данных, адреса, счетчика и вычислительного модуля для решения новой задачи по новым внешним данным.

Введение третьего, четвертого элементов ИЛИ и обусловленных ими связей позволяют осуществлять управление выдачей сигналов сравнения со схем сравнения для формирования сигнала норма и управления мультиплексора соответственно.

Введение первого элемента И и обусловленных им связей позволяет осуществлять приведение счетчика в исходное (нулевое) состояние перед решением новой задачи.

Введение второго элемента И и обусловленных им связей позволяет останавливать вычислительный процесс при формировании сигнала отказ устройства.

Введение третьего элемента И и обусловленных им связей позволяет управлять триггером отказа.

Введение четвертого, пятого элементов И и обусловленных ими связей позволяет осуществлять управление выдачей сигналов сравнения.

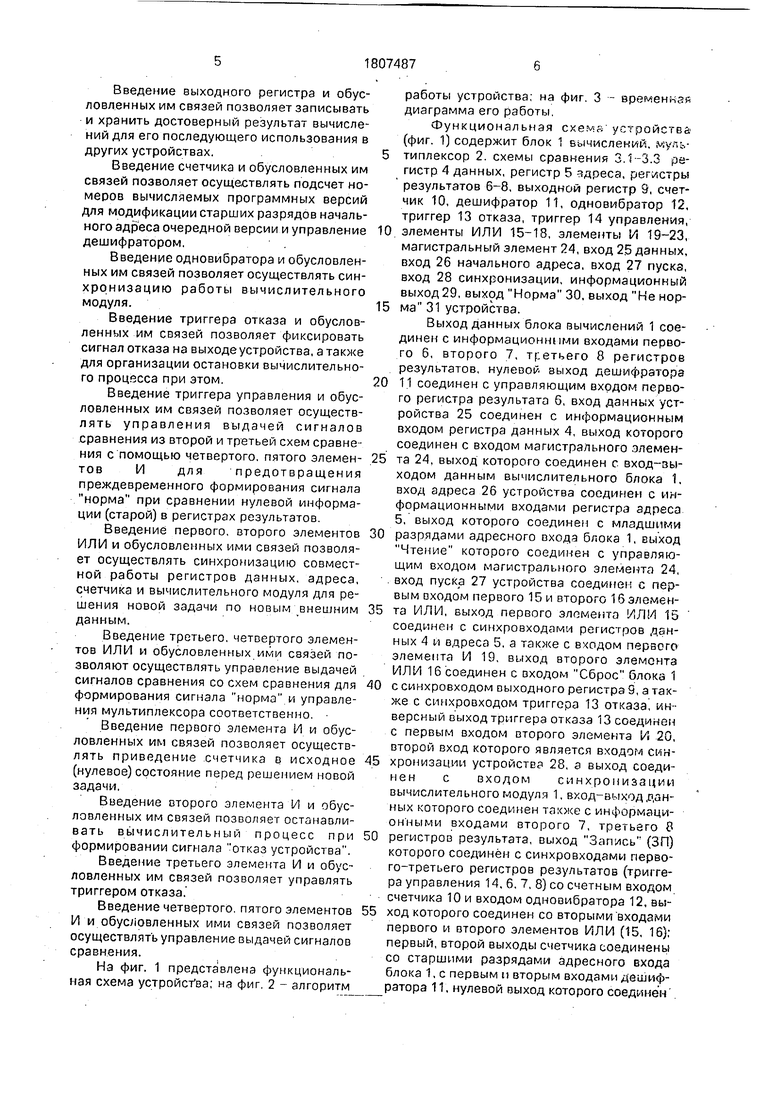

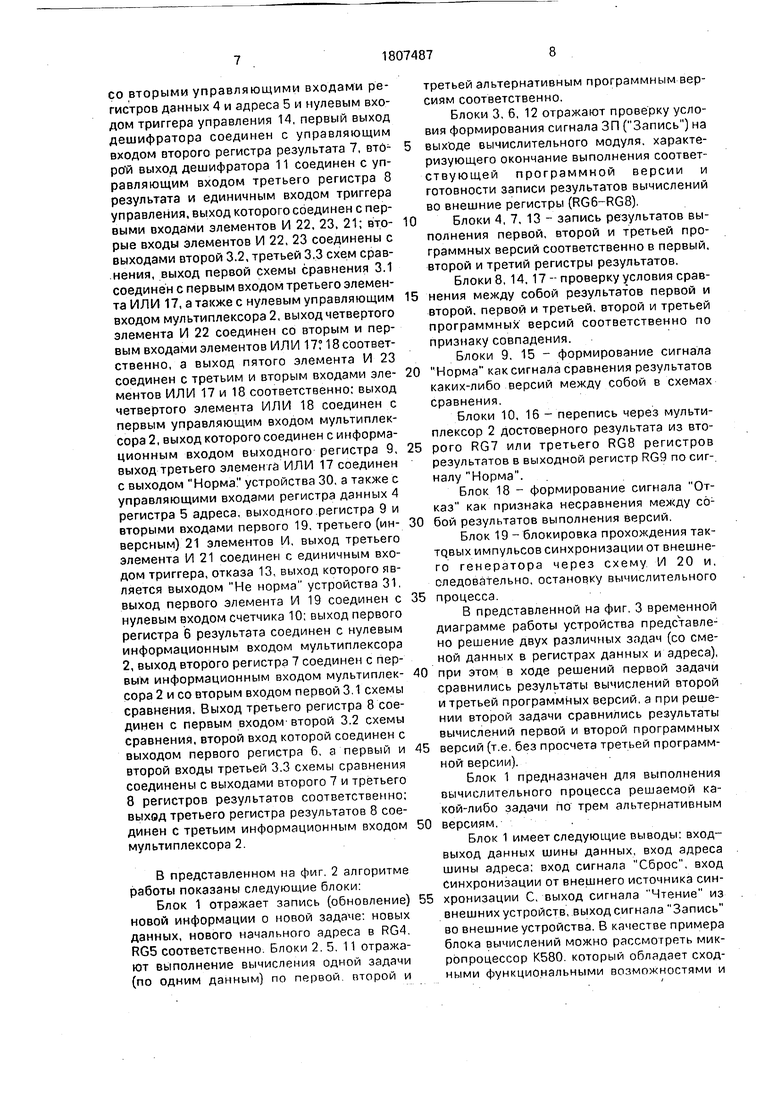

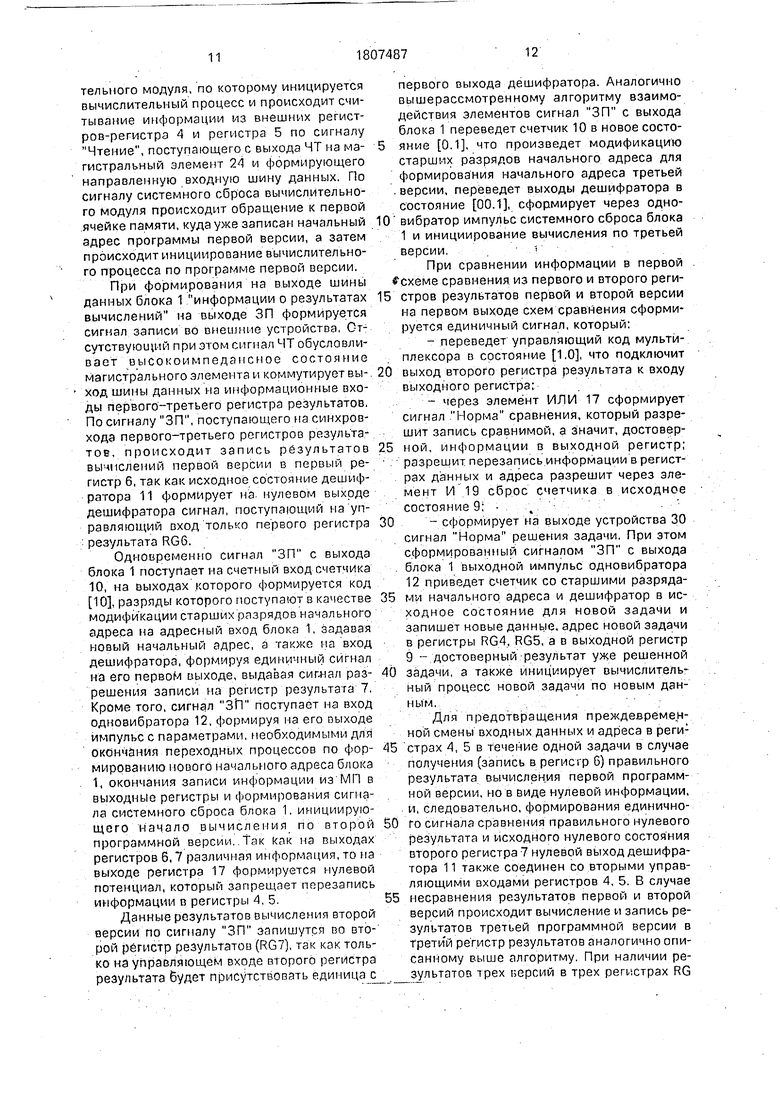

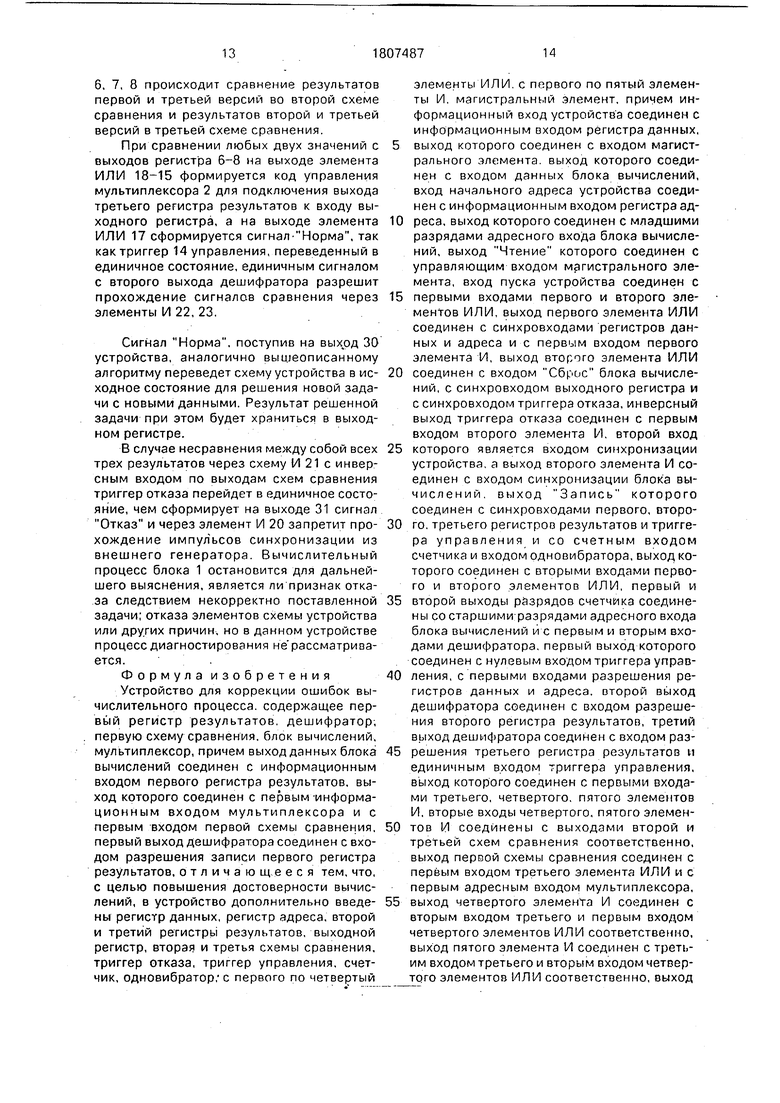

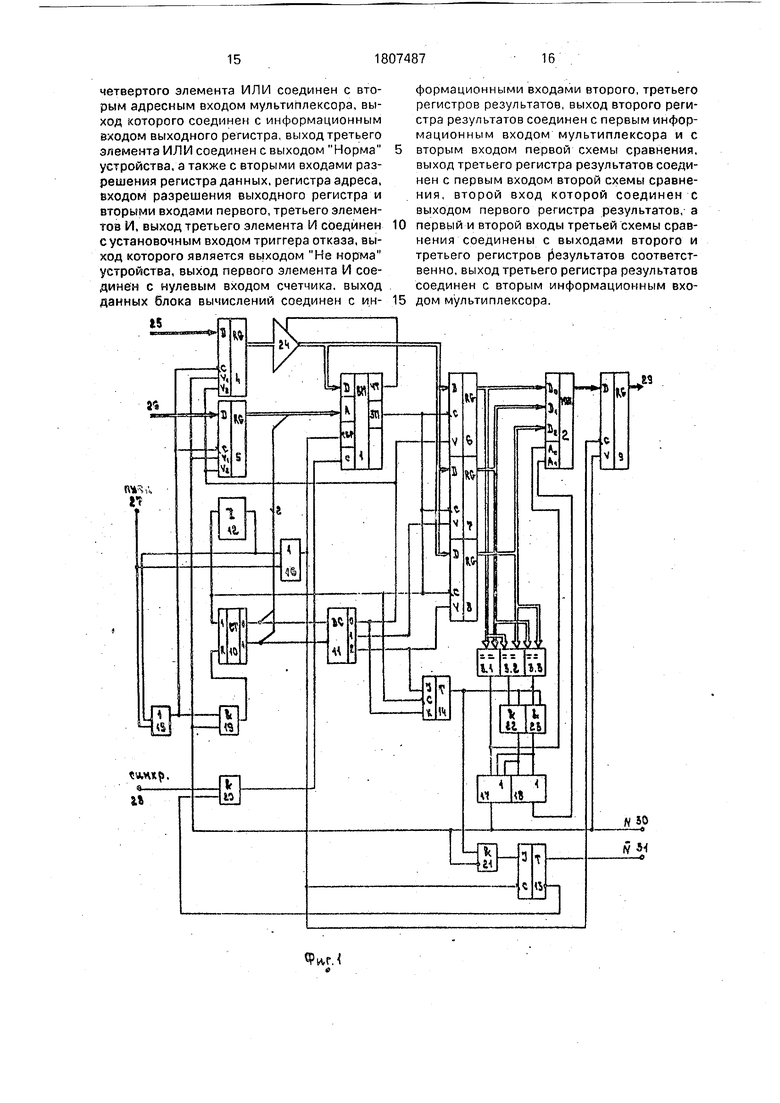

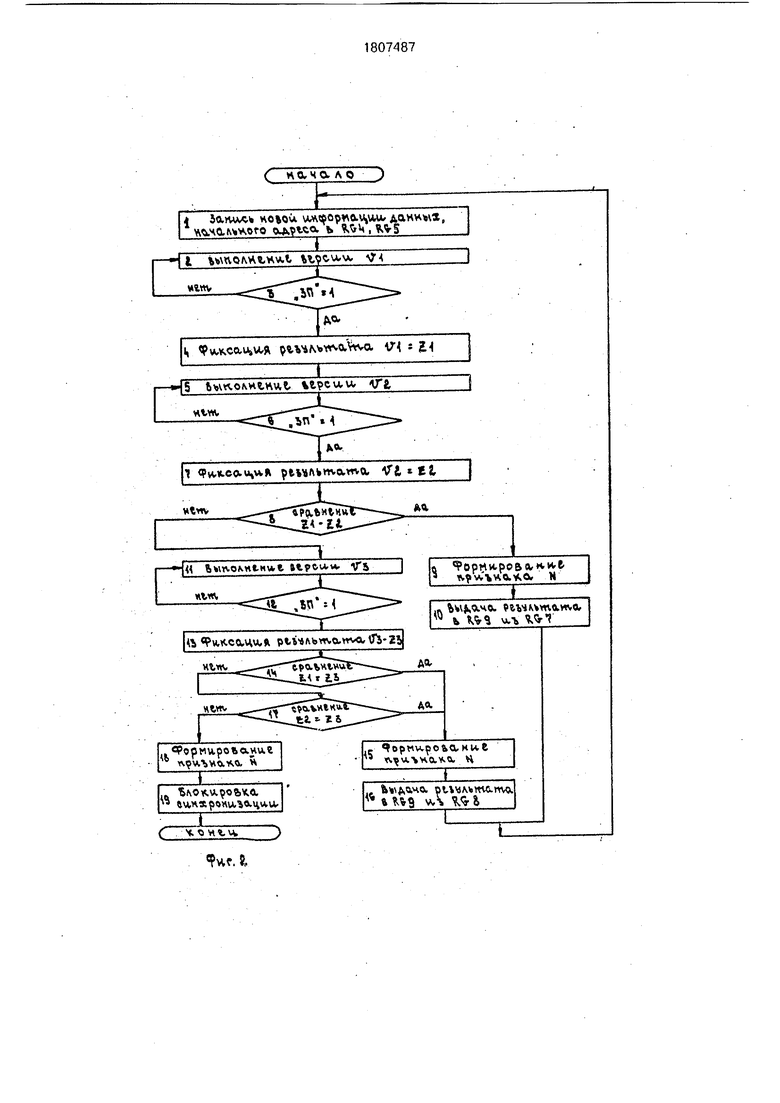

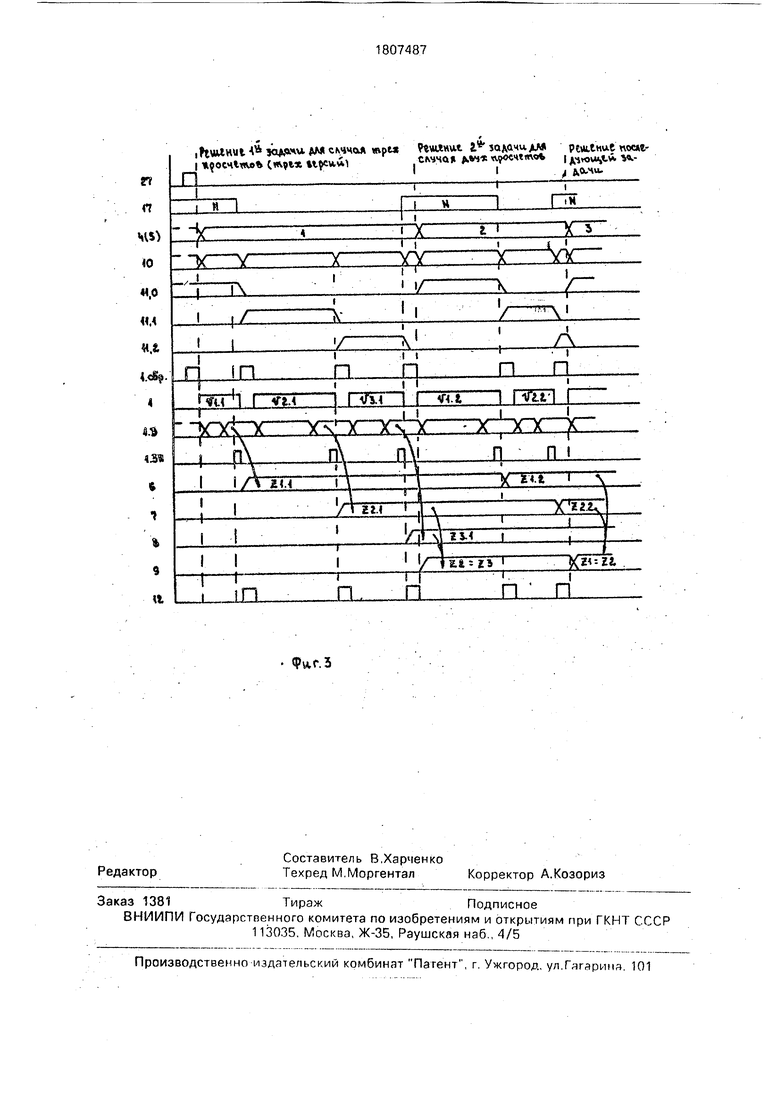

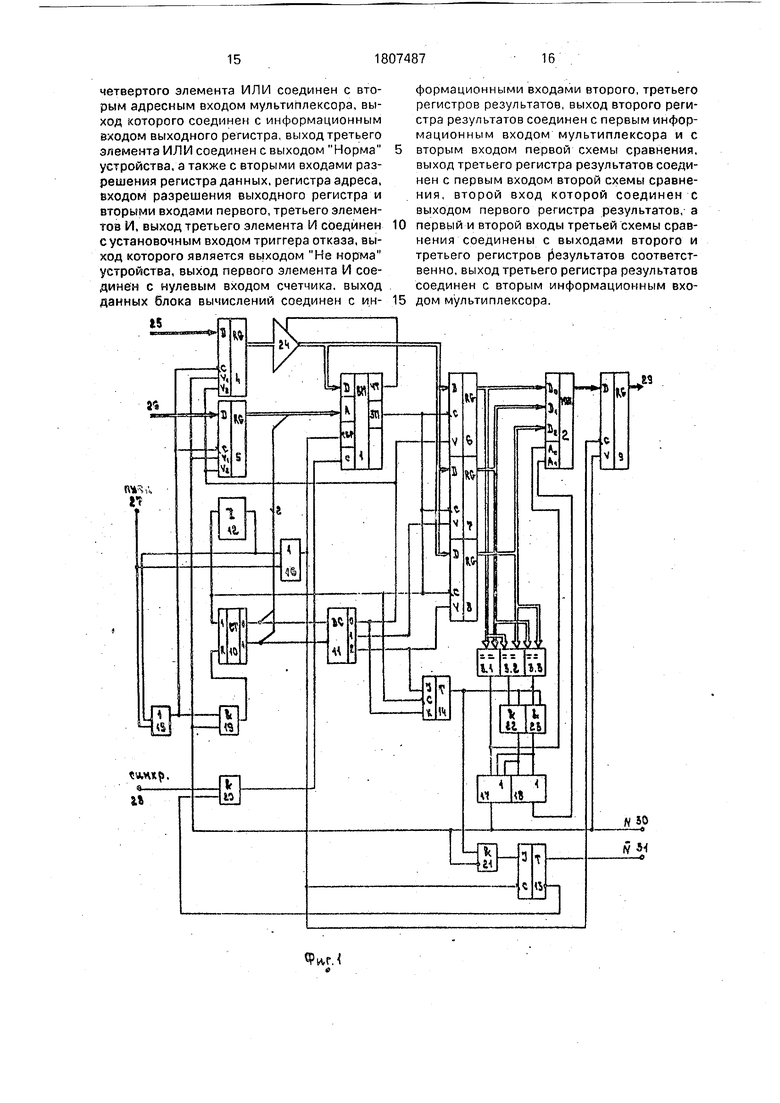

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - алгоритм

работы устройства; на фиг. 3 - временная диаграмма его работы.

Функциональная схема устройства (фиг. 1) содержит блок 1 вычислений, муль- 5 типлексор 2. схемы сравнения 3.1-3.3 регистр 4 данных, регистр 5 здреса, регистры результатов 6-8, выходной регистр 9, счетчик 10, дешифратор 11, одновибратор 12, триггер 13 отказа, триггер 14 управления,

0. элементы ИЛИ 15-18, элементы И 19-23, магистральный элемент 24, вход 25 данных, вход 26 начального адреса, вход 27 пуска, вход 28 синхронизации, информационный выход 29, выход Норма 30, выход Не нор5 ма 31 устройства.

Выход данных блока вычислений 1 соединен с информационнпми входами первого 6, второго 7, третьего 8 регистров результатов, нулевой выход дешифратора

0 1.1 соединен с управляющим входом первого регистра результата 6, вход данных устройства 25 соединен с информационным входом регистра данных 4, выход которого соединен с входом магистрального элемен5 та 24, выход которого соединен с вход-зы- ходом данным вычислительного блока 1. вход адреса 26 устройства соединен с информационными входами регистра адреса 5, выход которого соединен с младшими

0 разрядами адресного входа блока 1, выход Чтение которого соединен с управляющим входом магистрального элемента 24, . вход пуска 27 устройства соединен с первым входом первого 15 и второго 16элемен5 та ИЛИ, выход первого элемента ИЛИ 15 соединен с синхровходами регистров данных 4 и вдреса 5, а также с входом первого элемента И 19, выход второго элемента ИЛИ 16 соединен с входом Сброс блока 1

0 с синхровходом выходного регистра 9, а также с синхровходом триггера 13 отказа, инверсный выход триггера отказа 13 соединен с первым входом второго элемента И 20, второй вход которого является входом смн5 хронизации устройства 28, д выход соединен с входом синхронизации вычислительного модуля 1, вход-выход данных которого соединен также с информационными входами второго 7, третьего 8

0 регистров результата, выход Запись11 (ЗП) которого соединён с синхровходами первого-третьего регистров результатов (триггера управления 14, 6. 7, 8) со счетным входом счетчика 10 и входом одновибратора 12, вы5 ход которого соединен со вторыми входами первого и второго элементов ИЛИ (15, 16); первый, второй выходы счетчика соединены со старшими разрядами адресного входа блока 1, с первым и вторым входами дешифратора 11, нулевой выход которого соединен

со вторыми управляющими входами регистров данных 4 и адреса 5 и нулевым входом триггера управления 14, первый выход дешифратора соединен с управляющим входом второго регистра результата 7, вто- ро й выход дешифратора 11 соединен с управляющим входом третьего регистра 8 результата и единичным входом триггера управления, выход которого соединен с первыми входами элементов И 22, 23, 21; вто- рые входы элементов А 22, 23 соединены с выходами второй 3.2, третьей 3.3 схем сравнения, выход первой схемы сравнения 3.1 соединен с первым входом третьего элемента ИЛИ 17, а также с нулевым управляющим входом мультиплексора 2, выход четвертого элемента И 22 соединен со вторым и первым входами элементов ИЛИ 17 18 соответственно, а выход пятого элемента И 23 соединен с третьим и вторым входами эле- ментов ИЛИ 17 и 18 соответственно; выход четвертого элемента ИЛИ 18 соединен с первым управляющим входом мультиплексора 2, выход которого соединен с информационным входом выходного регистра 9, выход третьего элемента ИЛИ 17 соединен с выходом Норма устройства 30. а также с управляющими входами регистра данных 4 регистра 5 адреса, выходного .регистра 9 и вторыми входами первого 19, третьего (ин- версным) 21 элементов И, выход третьего элемента И 21 соединен с единичным входом триггера, отказа 13, выход которого является выходом Не норма устройства 31, выход первого элемента И 19 соединен с нулевым входом счетчика 10; выход первого регистра 6 результата соединен с нулевым информационным входом мультиплексора 2, выход второго регистра 7 соединен с первым информационным входом мультиплек- сора 2 и со вторым входом первой 3.1 схемы сравнения. Выход третьего регистра 8 соединен с первым входом-второй 3.2 схемы сравнения, второй вход которой соединен с выходом первого регистра б, а первый и второй входы третьей 3.3 схемы сравнения соединены с выходами второго 7 и третьего 8 регистров результатов соответственно; выход третьего регистра результатов 8 соединен с третьим информационным входом мультиплексора 2.

В представленном на фиг. 2 алгоритме работы показаны следующие блоки:

Блок 1 отражает запись (обновление) новой информации о новой задаче: новых данных, нового начального адреса в RG4. RG5 соответственно. Блоки 2. 5, 11 отражают выполнение вычисления одной задачи (по одним данным) по первой, второй и

третьей альтернативным программным версиям соответственно.

Блоки 3, 6, 12 отражают проверку условия формирования сигнала ЗП (Запись) на выходе вычислительного модуля, характеризующего окончание выполнения соответствующей программной версии и готовности записи результатов вычислений во внешние регистры (RG6-RG8).

Блоки 4, 7, 13 - запись результатов выполнения первой, второй и третьей программных версий соответственно в первый, второй и третий регистры результатов.

Блоки 8, 14,17 - проверку условия сравнения между собой результатов первой и второй, первой и третьей, второй и третьей программных версий соответственно по признаку совпадения.

Блоки 9, 15 - формирование сигнала Норма как сигнала сравнения результатов каких-либо версий между собой в схемах сравнения.

Блоки 10, 16 - перепись через мультиплексор 2 достоверного результата из второго RG7 или третьего RG8 регистров результатов в выходной регистр RG9 по сиг-, налу Норма.

Блок 18 - формирование сигнала Отказ как признака несравнения между собой результатов выполнения версий.

Блок 19 - блокировка прохождения так- тдвых импульсов синхронизации от внешнего генератора через схему И 20 и, следовательно, остановку вычислительного процесса.

В представленной на фиг. 3 временной диаграмме работы устройства представлено решение двух различных задач (со сменой данных в регистрах данных и адреса), при этом в ходе решений первой задачи сравнились результаты вычислений второй и третьей программных версий, а при решении второй задачи сравнились результаты вычислений первой и второй программных версий (т.е. без просчета третьей программной версии).

Блок 1 предназначен для выполнения вычислительного процесса решаемой какой-либо задачи по трем альтернативным версиям.

Блок 1 имеет следующие выводы: вход- выход данных шины данных, вход адреса шины адреса; вход сигнала Сброс, вход Синхронизации от внешнего источника синхронизации С, выход сигнала Чтение из внешних устройств, выход сигнала Запись во внешние устройства. В качестве примера блока вычислений можно рассмотреть микропроцессор К580. который обладает сходными функциональными возможностями и

имеет соответствие следующих входов-выходов: входу-выходу данных блока 1 соответствуют выводы восьмиразрядной двунаправленной шины данных К580, адресному входу - выводы адресной шины, входу Сброс блока 1 - вход сигнала системной установки в исходное .состояния Сброс, генерируемого внешней схемой управления, по которому происходит обращение к начальному адресу программы и инициирование ее вычисления.

Синхровходу блока 1 соответствует син- хровход МПК580, на который поступаюттак- тированные сигналы от внешнего генератора, выходу Чтение соответствует выход Чтение из внешних устройств МПК580, выходу Запись - одноименный инвертируемый: выход МПК580 сигнала записи во внешние устройства.

Мультиплексор 2 предназначен для коммутации выходов второго или третьего регистров (в зависимости от вариантов сравнения) на выходной регистр 9 для выдачи из устройства достоверной информации вычислений.;

Схемы сравнения 3.1-3,3 предназначены для попарного сравнения между собой информации, записываемой в первый-тре- тйй регистры результатов и выдачи сигнала сравнения (сравнение - 1, несравнение-0).

Регистр 4 данных предназначен для записи и хранения данных, используемых во время решения двух или трех программных версий задачи. . . Регистр 5 адреса - для записи и хранения младших разрядов начального адреса программной версии.

Регистры 6-8 результатов -для хранения результатов вычислений первой, второй и третьей программных версий соответственно.

Выходной регистр 9 -для записи и хра- не ния достоверного результата вычисления решаемой задачи,

:. Счетчик 10 - для подсчета номеров вычисляемой (текущей) программной версии, ирпользуемых для модификации :старших разрядов начального адреса очередной версии, а также для управления дешифратором.

Дешифратор 11 - для формирования сигналов управления записью результатов первой-третьей программных версий в пер- вый-третий регистры результатов соответственно и управления триггером 14.

Одновибратор 12 - для формирования импульса Сброс в необходимый момент времени после окончания формирования начального адреса.

Триггер отказа 13 - для формирования сигнала отказа устройства и сигнала запрещения синхронизации вычислительного модуля в случае отказа (начальное условие - триггер в нулевом состоянии).

Триггер управления 14 - для управле- 5 ния выдачей сигналов сравнения с выходов схем сравнения с целью предотвращения .формирования сигнала сравнения при нулевой или старой информации во втором и третьем регистрах результатов.

0 Элементы ИЛИ 15,16-для синхронизации совместной работы регистров данных и адреса с вычислительным модулем.

Элемент ИЛИ 17 - для формирования сигнала Норма в случаях сравнения ре5 зультатов версий между собой.

Элемент ИЛИ 18 - для формирования сигнала управления мультиплексором в зависимости от варианта сравнения версий, Элемент И 19 - для формирования сиг0 нала Сброс счетчика в случае получения сигнала Норма и приведения счетчика в исходное состояние для решения новой задачи.;

Элемент И 20 -для разрешения работы

5 вычислительного устройства в случае отсутствия признака сигнала.Отказ устройства. Элемент 2.1 - для формирования сигнала управления триггера отказа при несравнении ни одного из результатов

0 программных версий после трех просчетов,

Элементы И 22, 23 - для воспрещения

формирования сигналов сравнения второй

и третьей схемами сравнения при просчете

. первой версии, когда во втором и третьем

5 регистрах результатов может находиться сравнимая нулевая или старая информа. ция. . ..

Магистральный элемент 24 - для разделения магистрали данных на входную и вы0 ходную шины данных.

:Устройство работает следующим образом. В исходном состоянии все элементы памяти устройства обнулены, на вход данных 25 .устройства поданы исходные дан5 ные, необходимые в процессе решения. На вход адреса 26 устройства подон начальный адрес первой программной версии вычислений решаемой задачи. На вход синхронизации устройства 28 подана генерация

0 синхронизации..

При подаче на вход устройства 27 единичного импульса ПУСК он через элемент ИЛИ 15 поступает на.синхровходы регистров данных и адреса и проводит запись в

5 регистры информации с входов 25, 26, так как на управляющем входе регистров А, 5 находится единица сигнала сравнения нулевой информации регистров результатов б, 7. Также пусковой импуг,-ьс через элемент ИЛИ 16 поступает на вход Сброс вычисли--

тельного модуля, по которому иницируется вычислительный процесс и происходит считывание информации из внешних регист- ров-регистра 4 и регистра 5 по сигналу Чтение, поступающего с выхода ЧТ на магистральный элемент 24 и формирующего направленную входную шину данных. По сигналу системного сброса вычислительного модуля происходит обращение к первой .ячейке памяти, куда уже записан начальный адрес программы первой версии, а затем происходит инициирование вычислительного процесса по программе первой версии.

При формирования на выходе шины данных блока 1 информации о результатах вычислений на выходе ЗП формируется сигнал записи во внешние устройства, Отсутствующий при этом сигнал ЧТ обусловливает высокоимпедансное состояние магистрального элемента и коммутирует вы-. ход шины данных на информационные входы первого-третьего регистра результатов. По сигналу ЗП, поступающего на синхров- хода первого-третьего регистров результатов, происходит запись результатов вычислений первой версии в первый регистр 6, так как исходное состояние дешифратора 11 формирует на- нулевом выходе дешифратора сигнал, поступающий на управляющий вход только первого регистра : результата RG6.

Одновременно сигнал ЗП с выхода блока 1 поступает на счетный вход счетчика 10, на выходах которого формируется код 10, разряды которого поступают в качестве модификации старших разрядов начального адреса на адресный вход блока 1, задавая новый начальный адрес, а также на вход дешифратора, формируя единичный сигнал на его первом выходе, выдавая сигнал разрешения записи на регистр результата 7. Кроме того, сигнал ЗП поступает на вход одновибратора 12, формируя на его выходе импульс с параметрами, необходимыми для Окончания переходных процессов по формированию нового начального адреса блока 1, окончания записи информации из МП в выходные регистры и формирования сигнала системного сброса блока 1. инициирующего и а ч а л о вычисления по второй программной версии..Так как на выходах регистров 6,7 различная информация, то на выходе регистра 17 формируется нулевой потенциал, который запрещает перезапись информации в регистры 4, 5.

Данные результатов вычисления второй версии по сигналу ЗП запишутся во вто- рой регистр результатов (RG7), так как только на управляющем входе второго регистра результата будет присутствовать единица с

первого выхода дешифратора. Аналогично вышерассмотренному алгоритму взаимодействия элементов сигнал ЗП с выхода блока 1 переведет счетчик 10 в новое состояние 0.1, что произведет модификацию

старших разрядов начального адреса для

формирования начального адреса третьей

. версии, переведет выходы дешифратора в

состояние 00.1, сформирует через одно вибратор импульс системного сброса блока 1 и инициирование вычисления по третьей версии.. .г .

При сравнении информации в первой tсхеме сравнения из первого и второго регистров результатов первой и второй версии на первом выходе схем сравнения сформируется единичный сигнал, который:

- переведет управляющий код мультиплексора в состояние 1.0, что подключит выход второго регистра результата к входу выходного регистра;

- через элемент ИЛИ 17 сформирует сигнал Норма сравнения, который разрешит запись сравнимой, а значит, достоверной, информации в выходной регистр;

разрешит перезапись информации в регистрах данных и адреса разрешит через элемент И 19 сброс счетчика в исходное состояние 9; . ,

- сформирует на выходе устройства 30

сигнал Норма решения задачи. При этом

сформированный сигналом ЗП с выхода

блока 1 выходной импульс одновибратора

12 приведет счетчик со старшими разрядами начального адреса и дешифратор в исходное состояние для новой задачи и запишет новые данные, адрес новой задачи в регистры RG4, RG5, а в выходной регистр 9 - достоверный результат уже решенной

задачи, а также инициирует вычислительный процесс новой задачи по новым данным.. / Для предотвращения преждевременной смены входных данных и адреса в реги:

страх 4, 5 в течение одной задачи в случае получения (запись в регистр 6) правильного результата вычисления первой программной версии, но в виде нулевой информации, и, следовательно, формирования единичного сигнала сравнения правильного нулевого результата и исходного нулевого состояния второго регистра 7 нулевой выход дешифратора 11 также соединен со вторыми управляющими входами регистров 4, 5. В случае

несравнения результатов первой и второй версий происходит вычисление и запись результатов третьей программной версии в третий регистр результатов аналогично описанному выше алгоритму. При наличии результатов трех г ерсий в трех регистрах RG

6, 7, 8 происходит сравнение результатов первой и третьей версий во второй схеме сравнения и результатов второй и третьей версий в третьей схеме сравнения.

При сравнении любых двух значений с выходов регистра 6-8 на выходе элемента ИЛИ 18-15 формируется код управления мультиплексора 2 для подключения выхода третьего регистра результатов к входу выходного регистра, а на выходе элемента ИЛИ 17 сформируется сигнал- Норма, так как триггер 14 управления, переведенный в единичное состояние, единичным сигналом с второго выхода дешифратора разрешит прохождение сигналов сравнения через элементы И 22, 23.

Сигнал Норма, поступив на выхрд 30 устройства, аналогично вышеописанному алгоритму переведет схему устройства в исходное состояние для решения новой задачи с новыми данными. Результат решенной задачи при этом будет храниться в выходном регистре.

В случае несравнения между собой всех трех результатов через схему И 21 с инверсным входом по выходам схем сравнения триггер отказа перейдет в единичное состояние, чем сформирует на выходе 31 сигнал Отказ и через элемент И 20 запретит прохождение импул ьсов синхронизации из внешнего генератора. Вычислительный процесс блока 1 остановится для дальнейшего выяснения,является ли признак отказа следствием некорректно поставленной задачи; отказа элементов схемы устройства или других причин, но в данном устройстве процесс диагностирования не рассматривается..

Формула изобретения

Устройство для коррекции ошибок вычислительного процесса, содержащее первый регистр результатов, дешифратор, первую схему сравнения, блок вычислений, мультиплексор, причем выход данных блока вычислений соединен с информационным входом первого регистра результатов, выход которого соединен с первым -информа- ционным входом мультиплексора и с первым входом первой схемы сравнения, первый выход дешифратора соединен с входом разрешения записи первого регистра результатов, отличаю щ е е с я тем, что, с целью повышения достоверности вычислений, в устройство дополнительно введены регистр данных, регистр адреса, второй и третий регистры результатов, выходной регистр, вторая и третья схемы сравнения, триггер отказа, триггер управления, счетчик, одновибратор; с первого по четвертый

элементы ИЛИ. с первого по пятый элементы И. магистральный элемент, причем информационный вход устройства соединен с информационным входом регистра данных, 5 выход которого соединен с входом магистрального элемента, выход которого соединен с входом данных блока вычислений, вход начального адреса устройства соединен с информационным входом регистра ад0 реса, выход которого соединен с младшими разрядами адресного входа блока вычислений, выход Чтение которого соединен с управляющим входом магистрального элемента, вход пуска устройства соединен с

5 первыми входами первого и второго элементов ИЛИ, выход первого элемента ИЛИ соединен с синхровходами регистров данных и адреса и с первым входом первого элемента И, выход второго элемента ИЛИ

0 соединен с входом Сброс блока вычислений, с синхровходом выходного регистра и с синхровходом триггера отказа, инверсный выход триггера отказа соединен с первым входом второго элемента И. второй вход

5 которого является входом синхронизации устройства, а выход второго элемента И соединен с входом синхронизации блока вычислений, выход Запись которого соединен с синхровходами первого, второ0 го. третьего регистров результатов и триггера управления и со счетным входом счетчика и входом одновибратора, выход которого соединен с вторыми входами первого и второго элементов ИЛИ, первый и

5 второй выходы разрядов счетчика соединены со старшими-разрядами адресного входа блока вычислений и с первым и вторым входами дешифратора, первый выход которого соединен с нулевым входом триггера управ0 ления, с первыми входами разрешения регистров данных и адреса, второй выход дешифратора соединен с входом разрешения второго регистра результатов, третий выход дешифратора соединен с входом раз5 решения третьего регистра результатов и единичным входом триггера управления, выход которого соединен с первыми входами третьего, четвертого, пятого элементов И, вторые входы четвертого, пятого элемен0 тов И соединены с выходами второй и третьей схем сравнения соответственно, выход первой схемы сравнения соединен с первым входом третьего элемента ИЛИ и с первым адресным входом мультиплексора,

5 выход четвертого элеменУа И соединен с вторым входом третьего и первым входом четвертого элементов ИЛИ соответственно, выход пятого элемента И соединен с третьим входом третьего и вторым входом четвертого элементов ИЛИ соответственно, выход

четвертого элемента ИЛИ соединен с вторым адресным входом мультиплексора, выход которого соединен с информационным входом выходного регистра, выход третьего элемента ИЛИ соединен с выходом Норма устройства, а также с вторыми входами разрешения регистра данных, регистра адреса, входом разрешения выходного регистра и вторыми входами первого, третьего элементов И, выход третьего элемента И соединен с установочным входом триггера отказа, аы- ход которого является выходом Не норма устройства, выход первого элемента И соединен с нулевым входом счетчика, выход данных блока вычислений соединен с ин0

5

формационными входами второго, третьего регистров результатов, выход второго регистра результатов соединен с первым информационным входом мультиплексора и с вторым входом первой схемы сравнения, выход третьего регистра результатов сое/чинен с первым входом второй схемы сравнения, второй вход которой соединен с выходом первого регистра результатов, а первый и второй входы третьей схемы сравнения соединены с выходами второго и третьего регистров результатов соответственно, выход третьего регистра результатов соединен с вторым информационным входом мультиплексора.

(7 пана ло )

3:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и реконфигурации дублированной системы | 1990 |

|

SU1815641A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1737453A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Система для программного управления резервированными объектами и их диагностирования | 1989 |

|

SU1741295A1 |

| Модульное устройство программного управления и контроля | 1990 |

|

SU1803905A1 |

| Устройство для программного управления | 1989 |

|

SU1698875A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

t .алое HOIOU Ал$оркй.«,мьдаин л, o fcytfta ь Ц,У5

±

yT i ycu V.

I

-Ц5 ,nv,t %грсаи yrfc

i

ft «Ри.кса.цц, pt ftbmavtvc- T--2b

3

.,,

Т

Ч.« HtW

)

4f. I

.с 9opMwpobu.KU.ft

,. H

±

. puy nvbnvo. Au ft ПЗ уЛ ,

| Устройство для контроля вычислительных машин | 1986 |

|

SU1390612A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммные управляющие устройства и системы /Подред, Г.Н.Тимоньки- на | |||

| Ч | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| -Харьков, 1982 | |||

| С | |||

| Способ приготовления кирпичей для футеровки печей, служащих для получения сернистого натрия из серно-натриевой соли | 1921 |

|

SU154A1 |

Авторы

Даты

1993-04-07—Публикация

1991-06-24—Подача