Изобретение относится к автоматие и вычислительной технике и может ыть использовано при разработке икропрограммных устройств управлеия, контроля и диагностирования ЭВМ вычислительных систем, систем прозводственного контроля и управления технологическими процессами.

Целью изобретения является упрощение и повьшение оперативности диагостирования устройства.

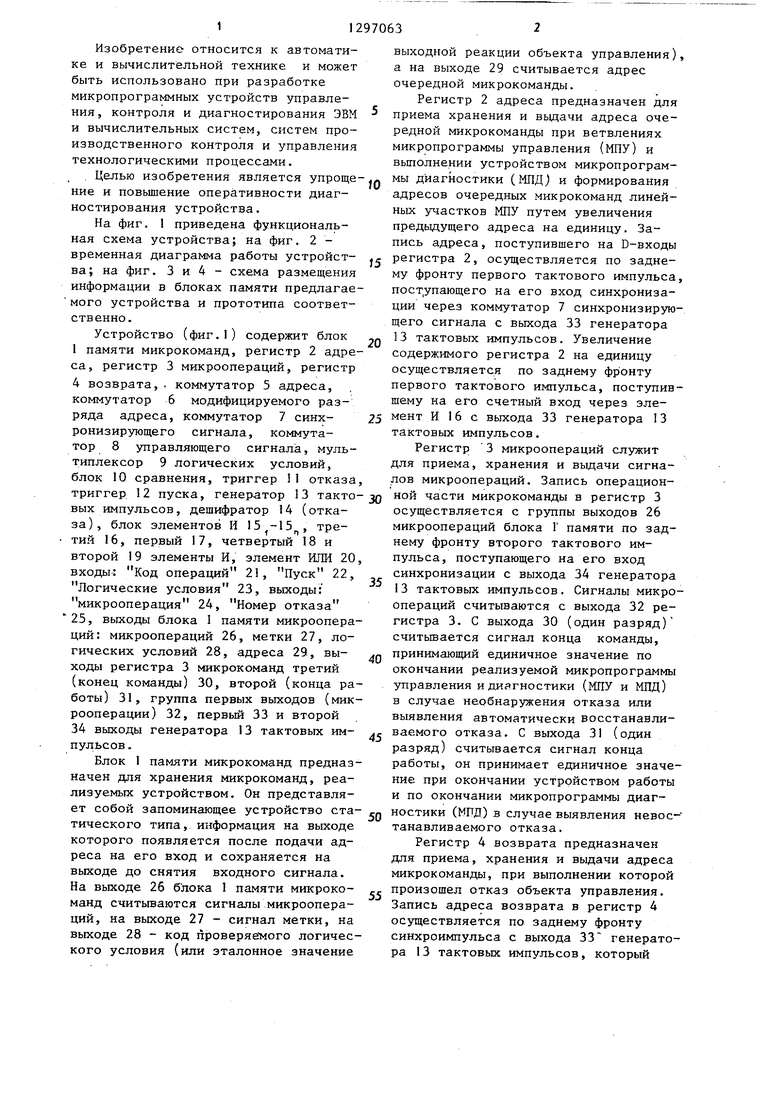

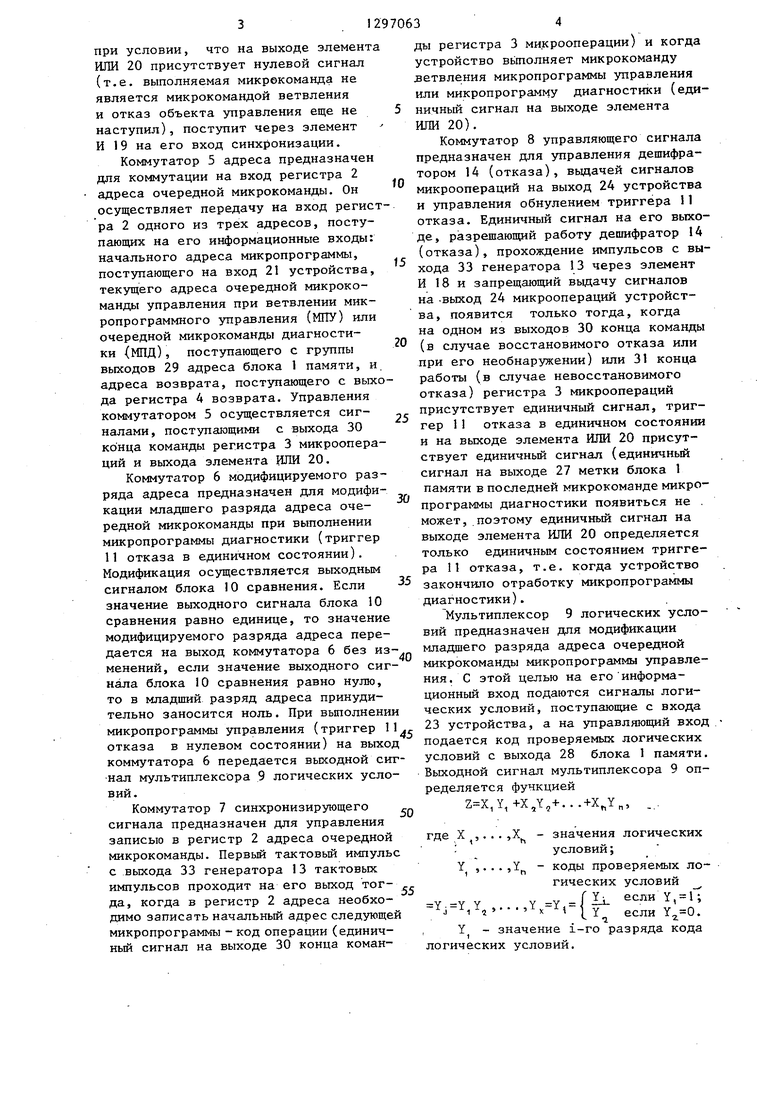

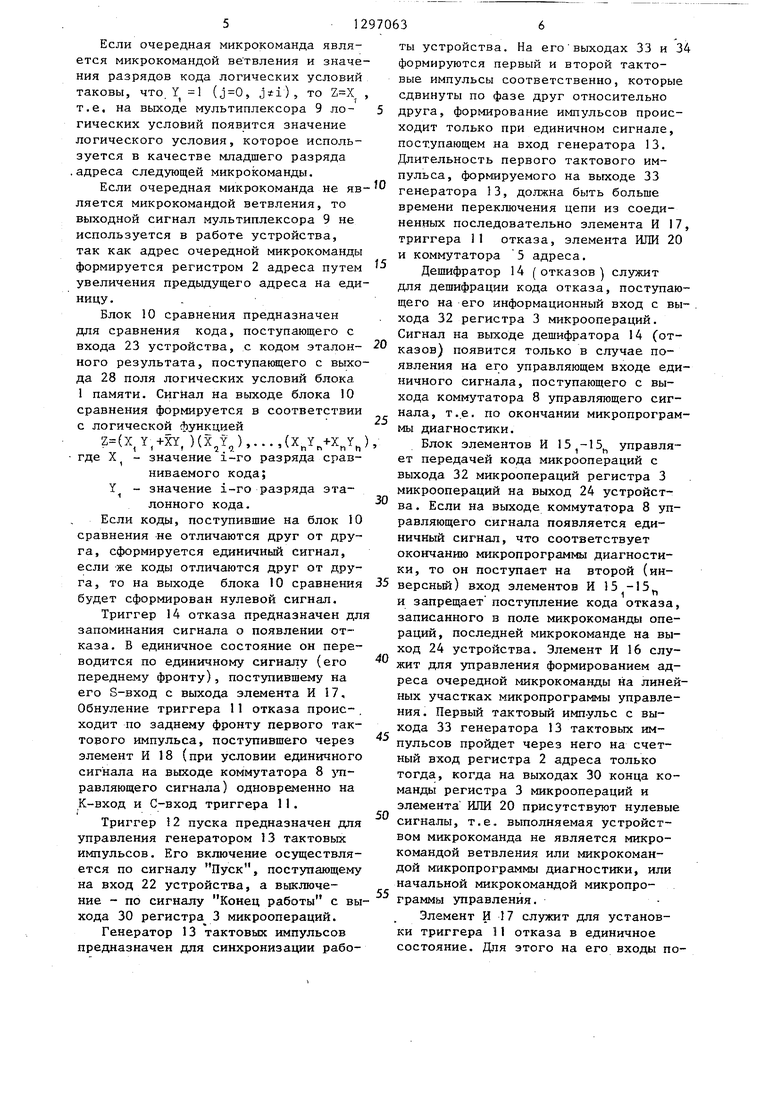

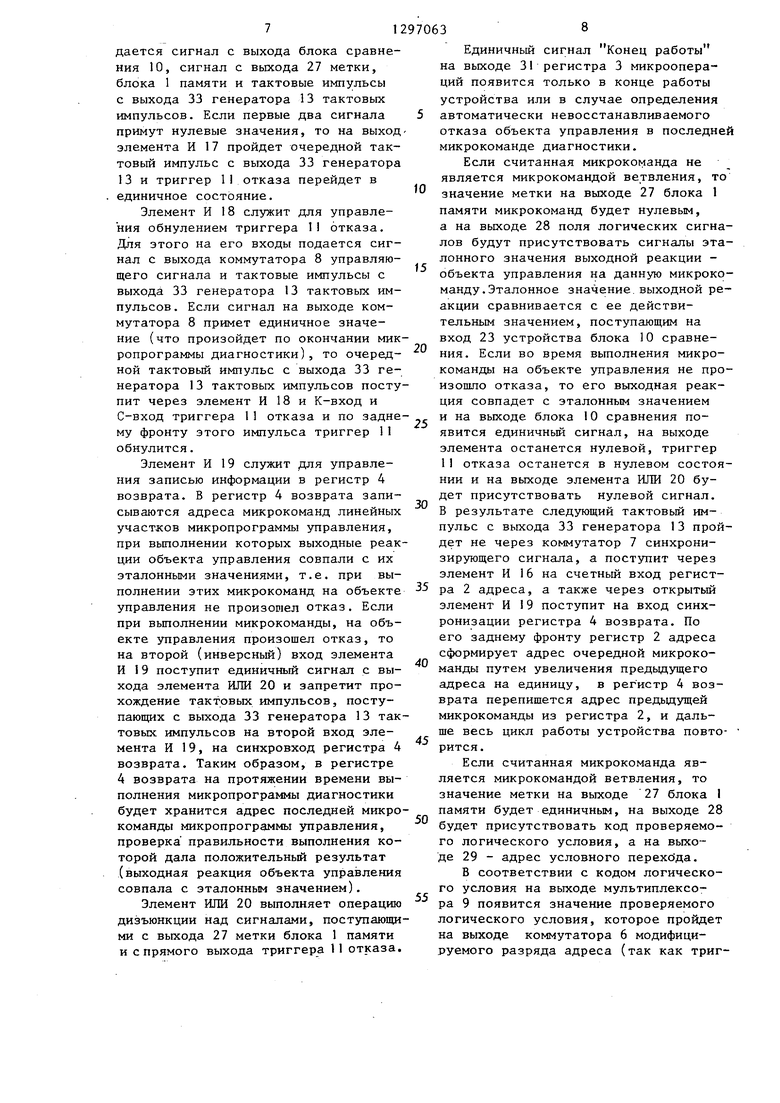

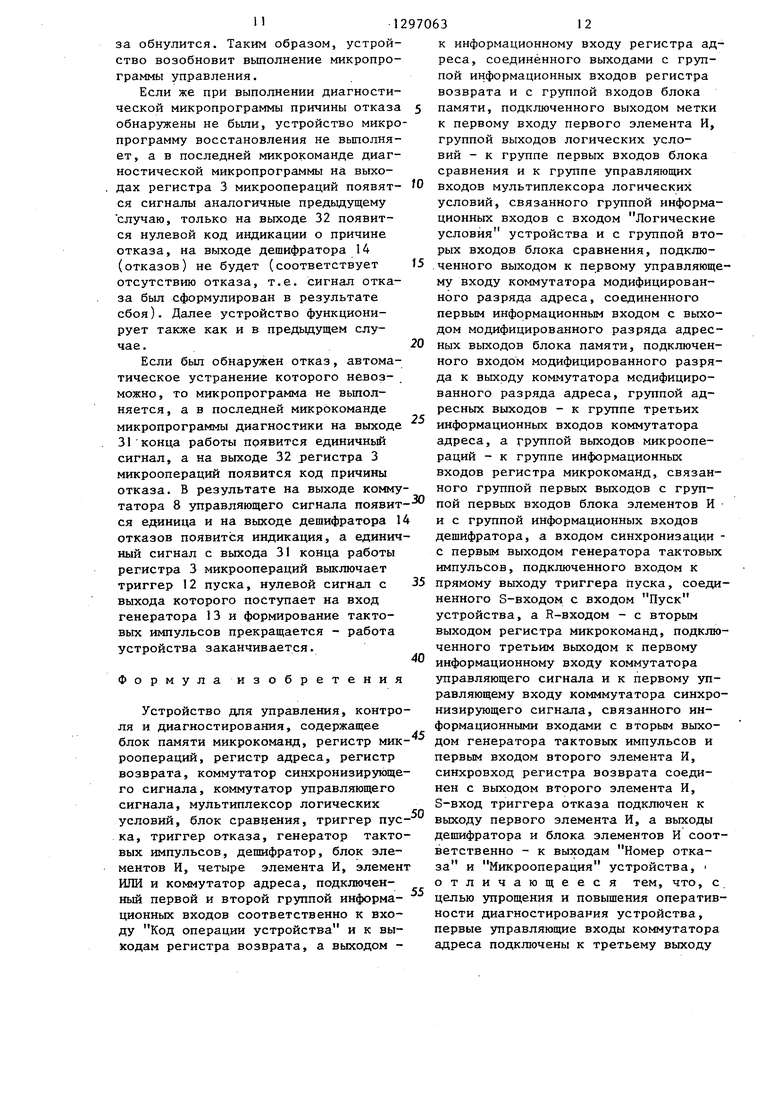

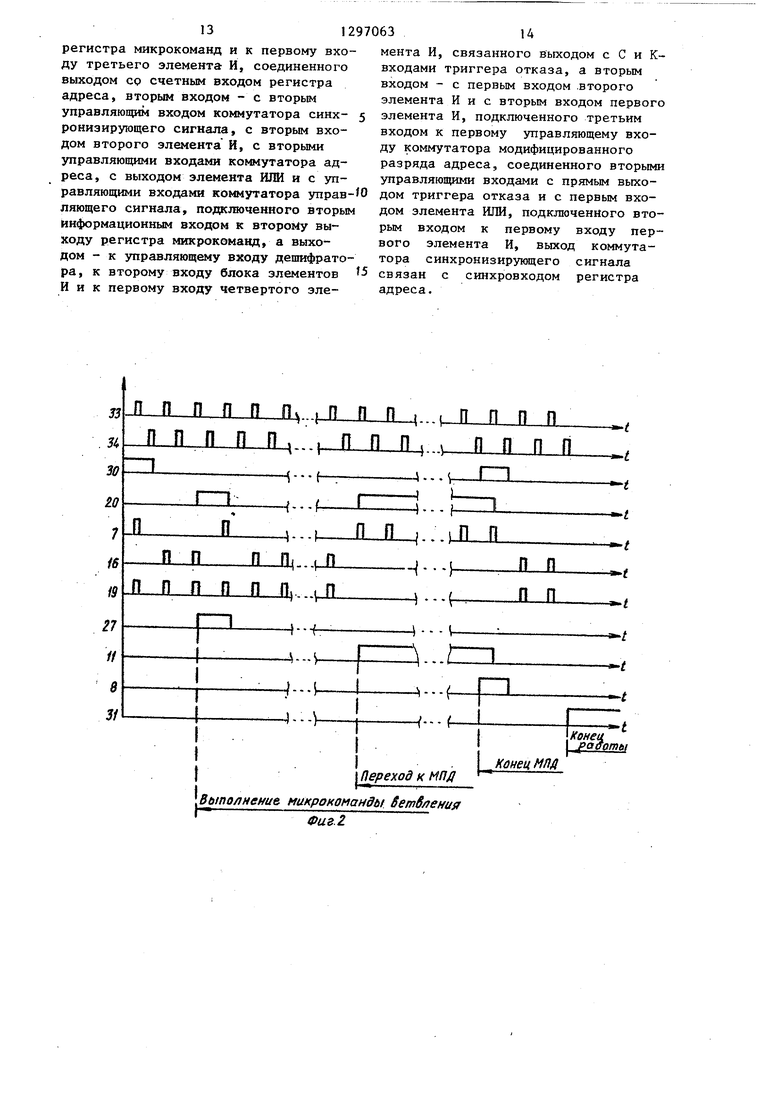

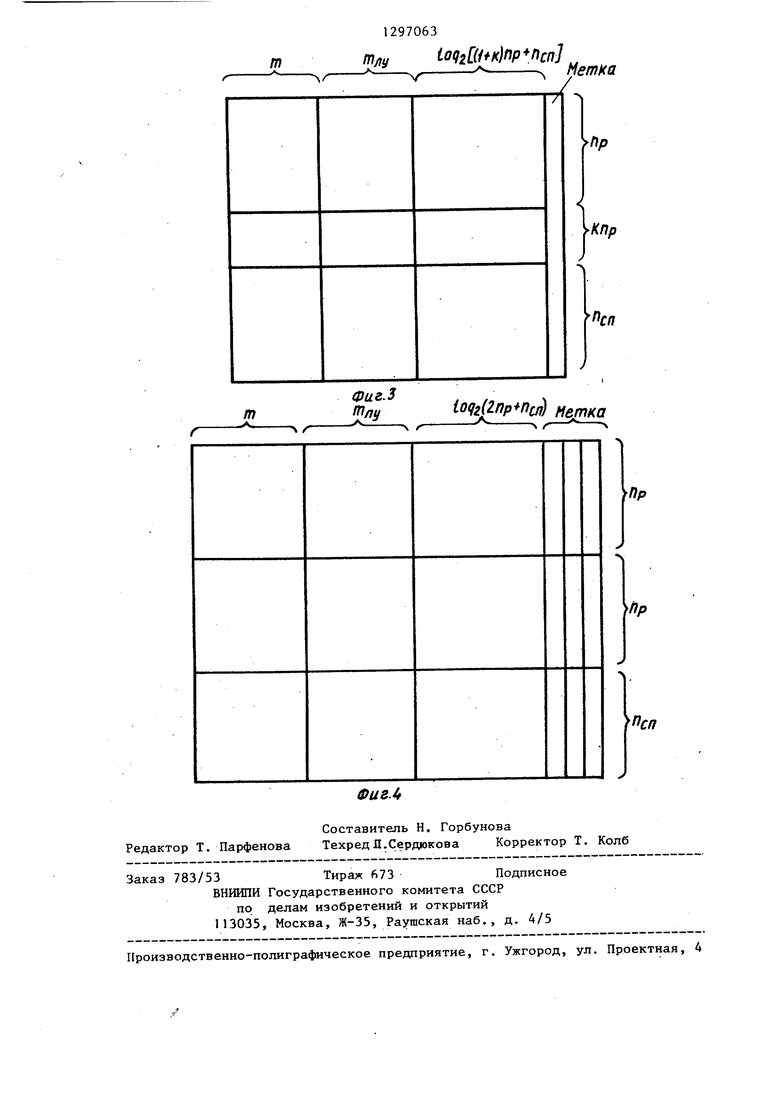

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - ременная диаграмма работы устройства; на фиг. 3 и 4 - схема размещения информации в блоках памяти предлагае- мого устройства и прототипа соответственно.

Устройство (фиг.1) содержит блок 1 памяти микрокоманд, регистр 2 адреса, регистр 3 микроопераций, регистр 4 возврата, г коммутатор 5 адреса, коммутатор 6 модифицируемого разряда адреса, коммутатор 7 синхронизирующего сигнала, коммутатор 8 управляющего сигнала, мультиплексор 9 логических условий, блок 10 сравнения, триггер 11 отказа, триггер 12 пуска, генератор 13 тактовых импульсов, дешифратор 14 (отказа), блок элементов И , третий 16, первый 17, четвертый 18 и второй 19 элементы И, элемент ИЛИ 20, входы: Код операций 21, Пуск 22, Логические условия 23, выходы: микрооперация 24, Номер отказа 25, выходы блока 1 памяти микроопераций: микроопераций 26, метки 27, логических условий 28, адреса 29, выходы регистра 3 микрокоманд третий (конец команды) 30, второй (конца работы) 31, группа первых выходов (микрооперации) 32, первый 33 и второй 34 выходы генератора 13 тактовых импульсов .

Блок 1 памяти микрокоманд предназначен для хранения микрокоманд, реализуемых устройством. Он представляет собой запоминающее устройство статического типа, информация на выходе которого появляется после подачи адреса на его вход и сохраняется на выходе до снятия входного сигнала. На выходе 26 блока 1 памяти микрокоманд считываются сигналы микроопераций, на выходе 27 - сигнал метки, на выходе 28 - код проверяе мого логического условия (или эталонное значение

5

0

5

0

5

0

5

0

55

выходной реакции объекта управления), а на выходе 29 считывается адрес очередной микрокоманды.

Регистр 2 адреса предназначен для приема хранения и выдачи адреса очередной микрокоманды при ветвлениях микропрограммы управления (МПУ) и выполнении устройством микропрограммы диагностики (МПД) и формирования адресов очередных микрокоманд линейных участков МПУ путем увеличения предьщущего адреса на единицу. Запись адреса, поступившего на D-входы регистра 2, осуществляется по заднему фронту первого тактового импульса, поступающего на его вход синхронизации через коммутатор 7 синхронизирующего сигнала с выхода 33 генератора 13 тактовых импульсов. Увеличение содержимого регистра 2 на единицу осуществляется по заднему фронту первого тактового импульса, поступившему на его счетный вход через элемент И 16 с выхода 33 генератора 13 тактовых импульсов.

Регистр 3 микроопераций служит для приема, хранения и выдачи сигналов микроопераций. Запись операционной части микрокоманды в регистр 3 осуществляется с группы выходов 26 микроопераций блока Г памяти по заднему фронту второго тактового импульса, поступающего на его вход синхронизации с выхода 34 генератора 13 тактовых импульсов. Сигналы микроопераций считываются с выхода 32 регистра 3. С выхода 30 (один разряд) считьгоается сигнал конца команды, принимающий единичное значение по окончании реализуемой микропрограммы управления и диагностики (МПУ и МПД) в случае необнаружения отказа или выявления автоматически восстанавливаемого отказа. С выхода 31 (один разряд) считывается сигнал конца работы, он принимает единичное значение при окончании устройством работы и по окончании микропрограммы диагностики (МПД) в случае выявления невос- танавливаемого отказа.

Регистр 4 возврата предназначен для приема, хранения и вьщачи адреса микрокоманды, при выполнении которой произошел отказ объекта управления. Запись адреса возврата в регистр 4 осуществляется по заднему фронту синхроимпульса с выхода 33 генератора 13 тактовых импульсов, который

при условии, что на выходе элемента ШШ 20 присутствует нулевой сигнал (т.е. выполняемая микрокоманда не является микрокомандой ветвления и отказ объекта управления еще не наступил), поступит через элемент И 19 на его вход синхронизации.

Коммутатор 5 адреса предназначен для коммутации на вход регистра 2 адреса очередной микрокоманды. Он осуществляет передачу на вход регистра 2 одного из трех адресов, поступающих на его информационные входы: начального адреса микропрограммы, поступающего на вход 21 устройства, текущего адреса очередной микрокоманды управления при ветвлении микропрограммного управления (МПУ) или очередной микрокоманды диагностики (МПД), поступающего с группы выходов 29 адреса блока 1 памяти, и адреса возврата, поступающего с выхода регистра 4 возврата. Управления коммутатором 5 осуществляется сигналами, поступающими с выхода 30 конца команды регистра 3 микроопераций и выхода элемента ИЛИ 20.

Коммутатор 6 модифицируемого разряда адреса предназначен для модификации младшего разряда адреса очередной микрокоманды при выполнении микропрограммы диагностики (триггер 11 отказа в единичном состоянии). Модификация осуществляется выходным сигналом блока 10 сравнения. Если значение выходного сигнала блока 10 сравнения равно единице, то значение модифицируемого разряда адреса передается на выход коммутатора 6 без изменений, если значение выходного сигнала блока 10 сравнения равно нулю, то в младший разряд адреса принудительно заносится ноль. При выполнени микропрограммы управления (триггер l отказа в нулевом состоянии) на выхо коммутатора 6 передается выходной синал мультиплексора 9 логических условий.

Коммутатор 7 синхронизирующего сигнала предназначен для управления записью в регистр 2 адреса очередной микрокоманды. Первьй тактовый импуль с выхода 33 генератора 13 тактовых импульсов проходит на его выход тогда, когда в регистр 2 адреса необходимо записать начальный адрес следующе микропрограммы - код операции (единичный сигнал на выходе 30 конца коман

to

15

20

25

ид г970634

ды регистра 3 микрооперации) и когда устройство вьтолняет микрокоманду ветвления микропрограммы управления или микропрограмму диагностики (единичный сигнал на выходе элемента ИЛИ 20).

Коммутатор 8 управляющего сигнала предназначен для управления дешифратором 14 (отказа), выдачей сигналов микроопераций на выход 24 устройства и управления обнулением триггера 11 отказа. Единичный сигнал на его выходе, разрешающий работу дешифратор 14 (отказа), прохождение импульсов с выхода 33 генератора 13 через элемент И 18 и запрещающий выдачу сигналов на -выход 24 микроопераций устройства, появится только тогда, когда на одном из выходов 30 конца команды (в случае восстановимого отказа или при его необнаружении) или 31 конца работы (в случае невосстановимого отказа) регистра 3 микроопераций присутствует единичный сигнал, триггер 11 отказа в единичном состоянии и на выходе элемента ИЛИ 20 присутствует единичный сигнал (единичный сигнал на выходе 27 метки блока 1 памяти в последней микрокоманде микропрограммы диагностики появиться не . может, поэтому единичный сигнал на выходе элемента ИЛИ 20 определяется только единичным состоянием триггера П отказа, т.е. когда устройство закончило отработку микропрограммы диагностики).

Мультиплексор 9 логических условий предназначен для модификации младшего разряда адреса очередной микрокоманды микропрограммы управления. С этой целью на его информационный вход подаются сигналы логических условий, поступающие с входа 23 устройства, а на управляющий вход подается код проверяемых логических условий с выхода 28 блока 1 памяти. Выходной сигнал мультиплексора 9 определяется функцией

30

35

40

50

,Y,+X,Y,+ ...,

5

где X

:Y. Y Y

J 1 7

,X - значения логических условий;

,Y - коды проверяемых логических условий

если Y,l;

Y Y X {

4

если 0.

Y - значение i-ro разряда кода логических условий.

Если очередная микрокоманда является микрокомандой ве твления и значения разрядов кода логических условий таковы, что Y 1 (j-0, jti), то , т.е. на выходе мультиплексора 9 ло- гических условий появится значение логического условия, которое используется в качестве младшего разряда .адреса следующей микрокоманды.

Если очередная микрокоманда не является микрокомандой ветвления, то выходной сигнал мультиплексора 9 не используется в работе устройства, так как адрес очередной микрокоманды формируется регистром 2 адреса путем увеличения предыдущего адреса на единицу,

Блок 10 сравнения предназначен

Дешифратор 14 (отказов служит для дешифрации кода отказа, поступающего на его информационный вход с выхода 32 регистра 3 микроопераций. Сигнал на выходе дешифратора 14 (отдля сравнения кода, поступающего с

входа 23 устройства, с кодом эталон- 20 казов) появится только в случае по- ного результата, поступающего с выхо- явления на его управляющем входе еди- да 28 поля логических условий блока ничного сигнала, поступающего с вы- 1 памяти. Сигнал на выходе блока 10 хода коммутатора 8 управляющего сиг- сравнения формируется в соответствии с логической функцией

Z(XY,+Xy,)(),..., {X,, где Х - значение i-ro разряда срав25

нала, т.е. по окончании микропрограммы диагностики.

Блок элементов И управляет передачей кода микроопераций с выхода 32 микроопераций регистра 3 микроопераций на выход 24 устройства . Если на выходе коммутатора 8 управляющего сигнала появляется единичный сигнал, что соответствует окончанию микропрограммы диагностики, то он поступает на второй (инниваемого кода;

Y - значение i-ro разряда эталонного кода.

Если коды, поступившие на блок 10 сравнения не отличаются друг от друга, сформируется единичный сигнал, если же коды отличаются друг от друга, то на выходе блока 10 сравнения 35 версньш) вход элементов И 15 -15 будет сформирован нулевой сигнал. и запрещает поступление кода отказа, Триггер 14 отказа предназначен для

записанного в поле микрокоманды операций, последней микрокоманде на выход 24 устройства. Элемент И 16 служит для управления формированием адреса очередной микрокоманды на линей ных участках микропрограммы управления . Первый тактовый импульс с выхода 33 генератора 13 тактовых импульсов пройдет через него на счетный вход регистра 2 адреса только тогда, когда на выходах 30 конца команды регистра 3 микроопераций и элемента ИЛИ 20 присутствзпот нулевые сигналы, т.е. выполняемая устройством микрокоманда не является микрокомандой ветвления или микрокомандой микропрограммы диагностики, или начальной микрокомандой микропрограммы управления.

запоминания сигнала о появлении отказа. В единичное состояние он переводится по единичному сигналу (его переднему фронту), поступившему на его S-вход с выхода элемента И 17, Обнуление триггера 11 отказа проис- . ходит по заднему фронту первого так- торого импульса, поступившего через элемент И 18 {при условии единичного сигнала на выходе коммутатора 8 щ- равляющего сигнала) одновременно на К-вход и С-вход триггера 11.

Триггер 12 пуска предназначен для управления генератором 13 тактовых импульсов. Его включение осуществляется по сигналу Пуск, поступающему на вход 22 устройства, а выключение - по сигналу Конец работы с выхода 30 регистра 3 микроопераций.

Генератор 13 тактовых импульсов предназначен для синхронизации работы устройства. На его выходах 33 и 34 формируются первый и второй тактовые импульсы соответственно, которые сдвинуты по фазе друг относительно друга, формирование импульсов происходит только при единичном сигнале, поступающем на вход генератора 13. Длительность первого тактового импульса, формируемого на выходе 33 генератора 13, должна быть больше времени переключения цепи из соединенных последовательно элемента И 17, триггера 1I отказа, элемента ИЛИ 20 и коммутатора 5 адреса.

Дешифратор 14 (отказов служит для дешифрации кода отказа, поступающего на его информационный вход с выхода 32 регистра 3 микроопераций. Сигнал на выходе дешифратора 14 (отказов) появится только в случае по- явления на его управляющем входе еди- ничного сигнала, поступающего с вы- хода коммутатора 8 управляющего сиг-

казов) появится только в случае по- явления на его управляющем входе еди- ничного сигнала, поступающего с вы- хода коммутатора 8 управляющего сиг-

нала, т.е. по окончании микропрограм

мы диагностики.

Блок элементов И управляет передачей кода микроопераций с выхода 32 микроопераций регистра 3 микроопераций на выход 24 устройства . Если на выходе коммутатора 8 управляющего сигнала появляется единичный сигнал, что соответствует окончанию микропрограммы диагностики, то он поступает на второй (инверсньш) вход элементов И 15 -15 и запрещает поступление кода отказа,

записанного в поле микрокоманды операций, последней микрокоманде на выод 24 устройства. Элемент И 16 слуит для управления формированием адреса очередной микрокоманды на линейных участках микропрограммы управления . Первый тактовый импульс с выхода 33 генератора 13 тактовых импульсов пройдет через него на счетный вход регистра 2 адреса только тогда, когда на выходах 30 конца команды регистра 3 микроопераций и элемента ИЛИ 20 присутствзпот нулевые сигналы, т.е. выполняемая устройством микрокоманда не является микрокомандой ветвления или микрокомандой микропрограммы диагностики, или начальной микрокомандой микропрограммы управления.

Элемент И 17 служит для установки триггера 11 отказа в единичное состояние. Для этого на его входы подается сигнал с выхода блока сравнения 10, сигнал с выхода 27 метки, блока 1 памяти и тактовые импульсы с выхода 33 генератора 13 тактовых импульсов. Если первые два сигнала примут нулевые значения, то на выход элемента И 17 пройдет очередной тактовый импульс с выхода 33 генератора 13 и триггер 11 отказа перейдет в единичное состояние.

Элемент И I8 служит для управления обнулением триггера 11 отказа. Для этого на его входы подается сигнал с выхода коммутатора 8 управляющего сигнала и тактовые импульсы с выхода 33 генератора 13 тактовых импульсов . Если сигнал на выходе коммутатора 8 примет единичное значение (что произойдет по окончании микЕдиничный сигнал Конец работы на выходе 31 регистра 3 микроопераций появится только в конце работы устройства или в случае определения автоматически невосстанавливаемого отказа обьекта управления в последней микрокоманде диагностики.

Если считанная микрокоманда не является микрокомандой ветвления, то значение метки на выходе 27 блока 1 памяти микрокоманд будет нулевым, а на выходе 28 поля логических сигналов будут присутствовать сигналы эталонного значения выходной реакции - обьекта управления на данную микрокоманду. Эталонное значение.выходной реакции сравнивается с ее действительным значением, поступающим на вход 23 устройства блока 10 сравне10

15

ропрограммы диагностики), то очеред- ния. Если во время выполнения микроной тактовьш импульс с выхода 33 генератора 13 тактовьпс импульсов поступит через элемент И 18 и К-вход и С-вход триггера I1 отказа и по заднему фронту этого импульса триггер 11 обнулится.

Элемент И 19 служит для управления записью информации в регистр 4 возврата. В регистр 4 возврата записываются адреса микрокоманд линейных участков микропрограммы управления, при выполнении которых выходные реакции объекта управления совпали с их эталонными значениями, т.е. при выполнении этих микрокоманд на объекте управления не произоиел отказ. Если при вьшолнении микрокоманды, на объекте управления произошел отказ, то на второй (инверсный) вход элемента И 19 поступит единичный сигнал с выхода элемента ИЛИ 20 и запретит прохождение тактовых импульсов, поступающих с выхода 33 генератора 13 тактовых импульсов на второй вход элемента И 19, на синхровход регистра 4 возврата. Таким образом, в регистре 4 возврата на протяжении времени выполнения микропрограммы диагностики будет хранится адрес последней микрокоманды микропрограммы управления, проверка правильности выполнения которой дала положительный результат (выходная реакция объекта управления совпала с эталонным значением).

Элемент ИЛИ 20 выполняет операцию дизъюнкции над сигналами, поступающими с выхода 27 метки блока 1 памяти и с прямого выхода триггера 1 1 отказа.

970638

Единичный сигнал Конец работы на выходе 31 регистра 3 микроопераций появится только в конце работы устройства или в случае определения автоматически невосстанавливаемого отказа обьекта управления в последней микрокоманде диагностики.

Если считанная микрокоманда не является микрокомандой ветвления, то значение метки на выходе 27 блока 1 памяти микрокоманд будет нулевым, а на выходе 28 поля логических сигналов будут присутствовать сигналы эталонного значения выходной реакции - обьекта управления на данную микрокоманду. Эталонное значение.выходной реакции сравнивается с ее действительным значением, поступающим на вход 23 устройства блока 10 сравне10

15

команды на объекте управления не произошло отказа, то его выходная реакция совпадет с эталонным значением и на выходе блока 10 сравнения появится единичньй сигнал, на выходе элемента останется нулевой, триггер 1I отказа останется в нулевом состоянии и на выходе элемента ИЛИ 20 будет присутствовать нулевой сигнал. В результате следующий тактовый импульс с выхода 33 генератора 13 пройдет не через коммутатор 7 синхронизирующего сигнала, а поступит через элемент И 16 на счетный вход регист- ра 2 адреса, а также через открытый элемент И I9 поступит на вход синхронизации регистра 4 возврата. По его заднему фронту регистр 2 адреса сформирует адрес очередной микрокоманды путем увеличения предыдущего адреса на единицу, в регистр 4 возврата перепишется адрес предыдущей микрокоманды из регистра 2, и дальше весь цикл работы устройства повторится.

Если считанная микрокоманда является микрокомандой ветвления, то значение метки на выходе 27 блока 1 памяти будет единичным, на выходе 28 будет присутствовать код проверяемого логического условия, а на выходе 29 - адрес условного перехода.

В соответствии с кодом логического условия на выходе мультиплексора 9 появится значение проверяемого логического условия, которое пройдет на выходе коммутатора 6 модифицируемого разряда адреса (так как триг

rep il отказа в нулевом состоянии) и будет являться младшим разрядом очередной микрокоманды. Таким образом будет осуществлена модификация адреса очередной микрокоманды значением проверяемого логического условия.

Так как значение метки на выходе 27 блока 1 памяти равно единице, то элемент И 17 закрыт и триггер 11 отказа не может быть переведен в единичное состояние, на выходе элемента ИЛИ 20 присутствует единичный сигнал, в соответствии с которым через коммутатор 5 адреса на информационный вход регистра 2 адреса поступит модифицированный адрес очередной микрокоманды, который запишется в него по заднему фронту следующего тактового импульса с выхода 33 генератора 13, поступившего на его вход синхронизации через коммутатор 7. Элементы И 16 и И 19 будут закрыты сигналом с выхода элемента ИЛИ 20, поэтому на счетный вход регистра 2 адреса и вхо синхронизации регистра 4 возврата тактовый импульс не поступит. Дальнейшая работа устройства будет определяться тем, что будет считанная микрокоманда являться микрокомандой ветвления или нет.

В случае появления отказа объекта управления при выполнении очередной микрокоманды линейного участка микропрограммы управления, т.е. микрокоманды не являющейся микрокомандой ветвления, выходная реакция объекта управления не совпадет с ее эталонным значением и на выходе блока 10 сравнения появится нулевой сигнал. На выходе 27 метки блока 1 памяти также нулевой сигнал и поэтому очередной тактовый импульс с выхода 33 генератора 13 пройдет через элемент И 17 на S-вход триггера 11 отказа и по его очередному фронту триггер 11 перейдет в единичное состояние. На выходе элемента ИЛИ 20 появится единичный сигнал. В результате через коммутатор 5 адреса на информационный вход регистра 2 адреса с выхода 29 блока 1 памяти поступит адрес микропрограммы диагностики, который запишется в регистр 2 по заднему фронту того же тактового импульса с выхода 33 генератора 13, поступившего через коммутатор выходов дешифратора 14; появится единичньй сигнал соответствующий коду, посту

0

5

пившему на его вход с выхода 32 регистра 3 микроопераций и однозначно указывающий на отказавший блок управляемого объекта. Одновременно единичный сигнал на выходе коммутатора 8 закроет блок элементов И 15 -15 и

о/ -

на выходе /4 устройства будет присутствовать нулевой код, и откроет элемент И 18 по Заднему фронту следующего тактового импульса.

Устройство работает следующим образом.

В исходном состоянии все элементы памяти устройства (фиг. 1) находятся в нулевом состоянии, за исключением разряда регистра 3 микроопераций, соответствующего выходу 30 конца комгшды регистра (цепи установки исходного состояния устройства не показаны), последний разрешает передачу через коммутатор 5 адреса кода операции с входа 21 устройства и его запись в регистр 2 адреса.

По сигналу Пуск с входа 22 устройства триггер 12 пуска устанавливается в единичное состояние и включает г ;нератор 13. По заднему фронту первого тактового импульса с выхода 33 генератора 13 тактовых импульсов, поступающего через коммутатор 7 синх- низирующего сигнала на синхровход регистр 2 адреса, регистр 2 с входа 21 устройства ,через коммутатор 5 адреса запишется код реализуемой микро- программы, который определяет адрес ее первой микрокоманды. Записанный в регистре 2 адрес поступает на вход блока 1 .памяти микрокоманд. В результате на его выходе 26 появятся сигналы микроопераций, на выходе 27 - значение метки на выходе 28 проверяемого логического условия, на выходе

29- адрес следующей микрокоманды.

По заднему фронту второго тактового импульса с выхода 34 генератора 13 микрооперационная часть микрокоманды записывается в регистр 3 микроопераций. В результате на его выходе

30конца работы пропадет единичньй сигнал, а на выходе 32 появятся сигналы микроопераций, которые через блок элементов И 15 -15 выдаются на выход 24 устройства, с выхода 33 генератора 13 в регистр 2 адреса через коммутатор 5 запишется адрес, хранящийся в регистре 4 возврата, т.е. адрес последней правильно выполненной микрокоманды, а триггер 11 отка0

0

5

0

за обнулится. Таким образом, устройство возобновит выполнение микропрограммы управления.

Если же при выполнении диагностической микропрограммы причины отказа обнаружены не были, устройство микропрограмму восстановления не выполняет, а в последней микрокоманде диагностической микропрограммы на выходах регистра 3 микроопераций появят- ся сигналы аналогичные предыдущему случаю, только на выходе 32 появится нулевой код индикации о причине отказа, на выходе дешифратора 14 (отказов) не будет (соответствует отсутствию отказа, т.е. сигнал отказа был сформулирован в результате сбоя). Далее устройство функционирует также как и в предыдущем случае.

Если был обнаружен отказ, автоматическое устранение которого невоз- . можно, то микропрограмма не выполняется , а в последней микрокоманде микропрограммы диагностики на выходе 31 конца работы появится единичный сигнал, а на выходе 32 регистра 3 микроопераций появится код причины отказа. В результате на выходе коммутатора 8 управляющего сигнала появит ся единица и на выходе дешифратора 1 отказов появится индикация, а единичный сигнал с выхода 31 конца работы регистра 3 микроопераций выключает триггер 12 пуска, нулевой сигнал с выхода которого поступает на вход генератора 13 и формирование тактовых импульсов прекращается - работа устройства заканчивается.

Формула изобретения

Устройство дпя управления, контроля и диагностирования, содержащее блок памяти микрокоманд, регистр мик роопераций, регистр адреса, регистр возврата, коммутатор синхронизирующего сигнала, коммутатор управляющего сигнала, мультиплексор логических условий, блок сравнения, триггер пус ка, триггер отказа, генератор тактовых импульсов, дешифратор, блок элементов И, четыре элемента И, элемент ИЛИ и коммутатор адреса, подключенный первой и второй группой информационных входов соответственно к входу Код операции устройства и к выводам регистра возврата, а выходом

5 О15 20

35

25

40

45

50

55

к информационному входу регистра адреса, соединённого выходами с группой информационных входов регистра возврата и с группой входов блока памяти, подключенного выходом метки к первому входу первого элемента И, группой выходов логических условий - к группе первых входов блока сравнения и к группе управляющих входов мультиплексора логических условий, связанного группой информационных входов с входом Логические условия устройства и с группой вторых входов блока сравнения, подклю- .ченного выходом к первому зтравляюще- му входу коммутатора модифицированного разряда адреса, соединенного первым информационным входом с выходом модифицированного разряда адресных выходов блока памяти, подключенного входом модифицированного разряда к выходу коммутатора модифицированного разряда адреса, группой адресных выходов - к группе третьих информационных входов коммутатора адреса, а группой выходов микроопераций - к группе информационных входов регистра микрокоманд, связанного группой первых выходов с группой первых входов блока элементов И и с группой информационных входов дешифратора, а входом синхронизации - с первым выходом генератора тактовых импульсов, подключенного входом к прямому выходу триггера пуска, соединенного S-входом с входом Пуск устройства, а R-входом - с вторым выходом регистра микрокоманд, подключенного третьим выходом к первому информационному входу коммутатора управляющего сигнала и к первому управляющему входу комммутатора синхронизирующего сигнала, связанного информационными входами с вторым выходом генератора тактовых импульсов и первым входом второго элемента И, синхровход регистра возврата соединен с выходом второго элемента И, S-вход триггера отказа подключен к выходу первого элемента И, а выходы дешифратора и блока элементов И соответственно - к выходам Номер отказа и Микрооперация устройства, отличающееся тем, что, с. целью зттрощения и повышения оперативности диагностирования устройства, первые управляющие входы коммутатора адреса подключены к третьему выходу

регистра микрокоманд и к первому входу третьего элемента: И, соединенного выходом со счетным входом регистра адреса, вторым входом - с вторым управляющим входом коммутатора сикх- ровизирующего сигнала, с вторым входом второго элемента И, с вторыми управляющими входами коммутатора адреса, с выходом элемента ШШ и с управляющими входами коммутатора управляющего сигнала, подключенного вторым информационным входом к второму выходу регистра микрокоманд, а выходом - к управляющему входу дешифратора, к второму входу блока элементов И и к первому входу четвертого эле

Выполнение микрокоманды Ветвления

мента И, связанного выходом с С и К- входами триггера отказа, а вторым входом - с первым входом .второго элемента И и с вторым входом первого элемента И, подключенного третьим входом к первому управляющему входу коммутатора модифицированного разряда адреса, соединенного вторыми управляющими входами с прямым выходом триггера отказа и с первым входом элемента ШШ, подключенного вторым входом к первому входу первого элемента И, выход коммутатора синхронизирующего сигнала связан с синхровходом регистра адреса.

Коней J aaom6i

Переход

КНПД

Конец МПД

т

т

ФигЛ

Составитель Н. Горбунова Редактор Т. Парфенова Техред Л.Сердюкова Корректор Т. Колб

.«.«-.- ««---- ----- --.-

Заказ 783/53Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

т/,{/ /

Метка

Фиг.З т„у

ioqzUnp ncn Метка

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления и диагностирования | 1984 |

|

SU1174930A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1180888A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1322282A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке микропрограммных устройств управления , контроля и диагностирования ЭВМ и вычислительных систем, систем производственного контроля и управления технологическими процессами. Цель изобретения - упрощение и повышение диагностирования устройства путем организации частичного совмещения реализации алгоритмов управления и диагностирования . Устройство содержит блок 1 памяти микрокоманд, регистр 2 адреса, регистр 3 микроопераций, регистр 4 возврата, коммутатор 5 адреса, коммутатор 6 модифицируемого разряда адреса, коммутатор 7 синхронизирующего сигнала, коммутатор 8 управляющего сигнала, мультиплексор 9 логических условий, блок 10 сравнения, триггер 11 отказа, триггер 12 пуска, генератор 13 тактовых импульсов , дешифратор 14, блок элементов И , третий, первый, четвертый и второй 16-19 элементы И, элемент ИЛИ 20. 4 ил. (Л to со -vl О) со

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления и диагностирования | 1984 |

|

SU1174930A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-22—Подача