Изобретение относится к автоматике и вычислительной технике и может быть использовано при получении минимизированного количества контрольных точек, необходимого для определения технического состояния дискретной аппаратуры0

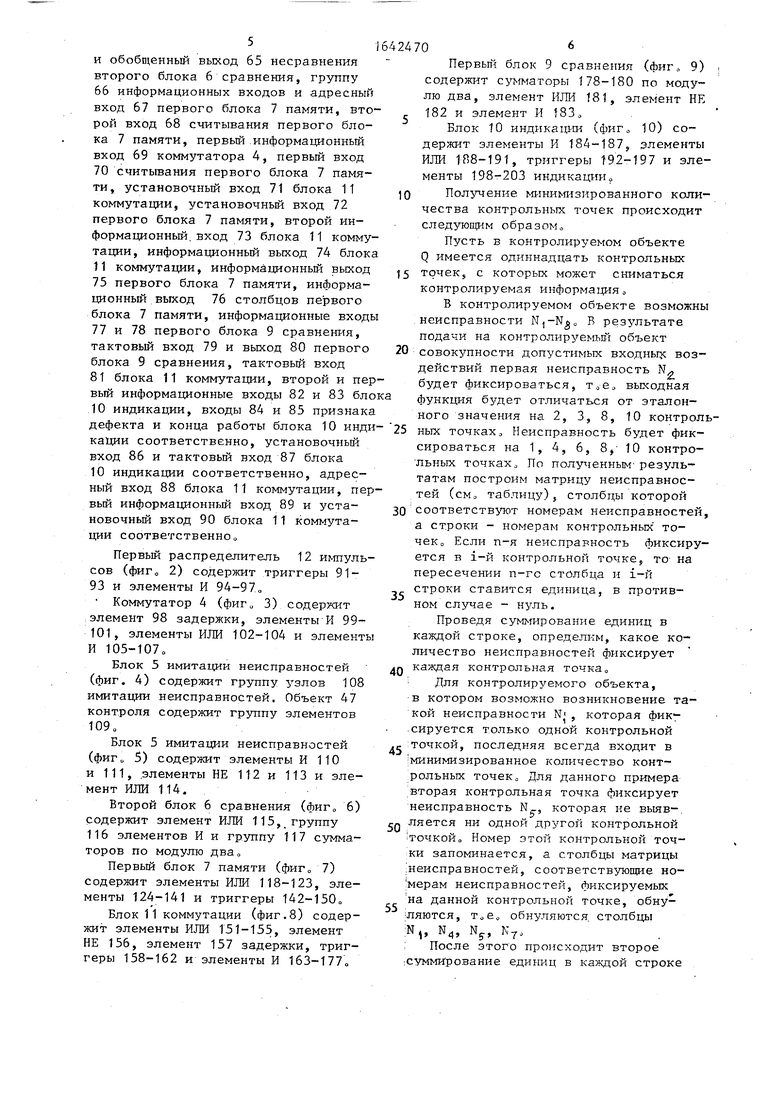

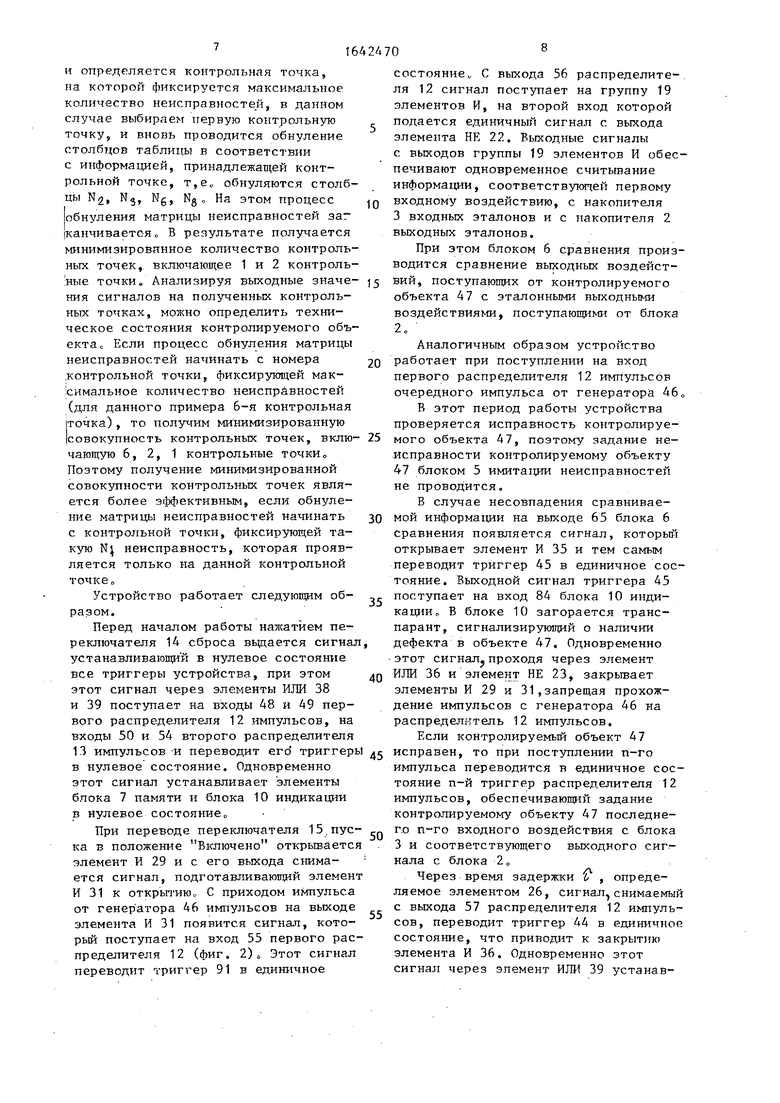

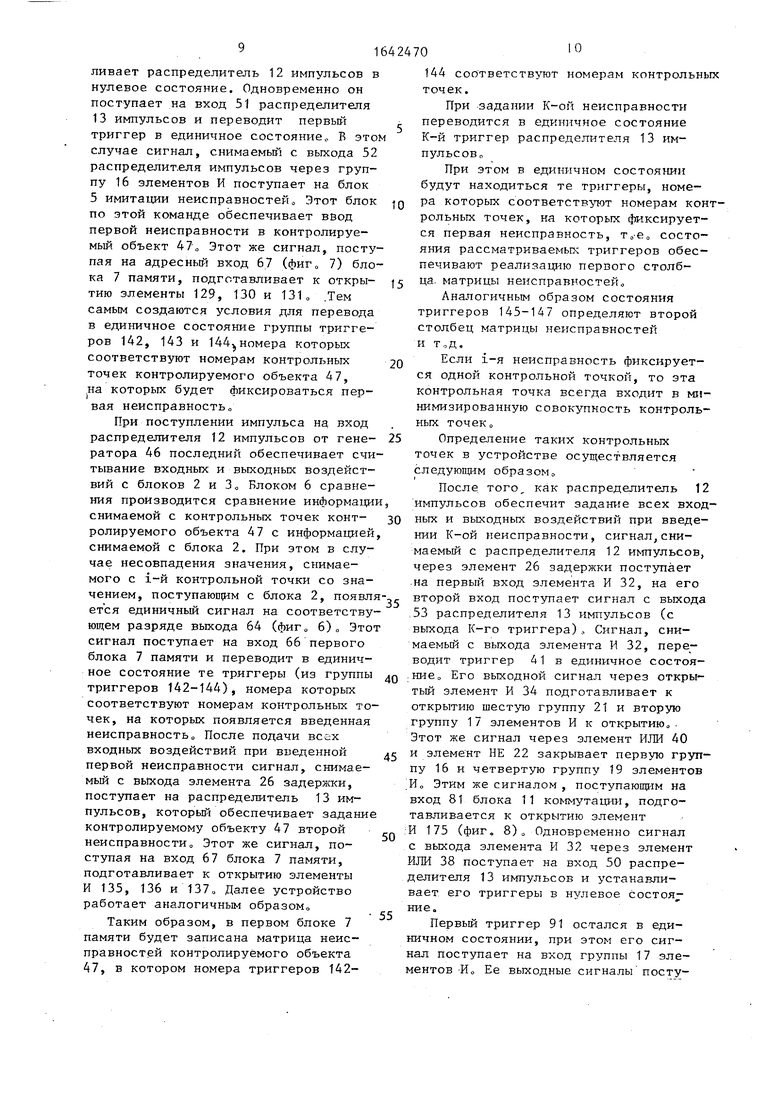

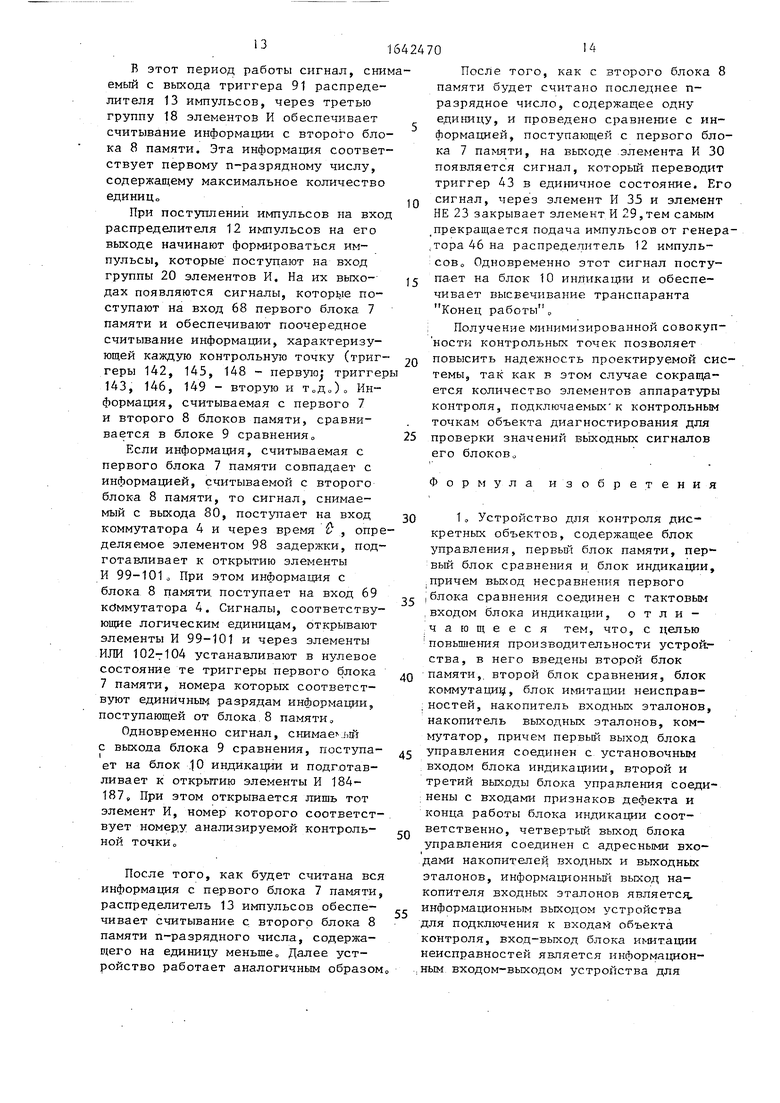

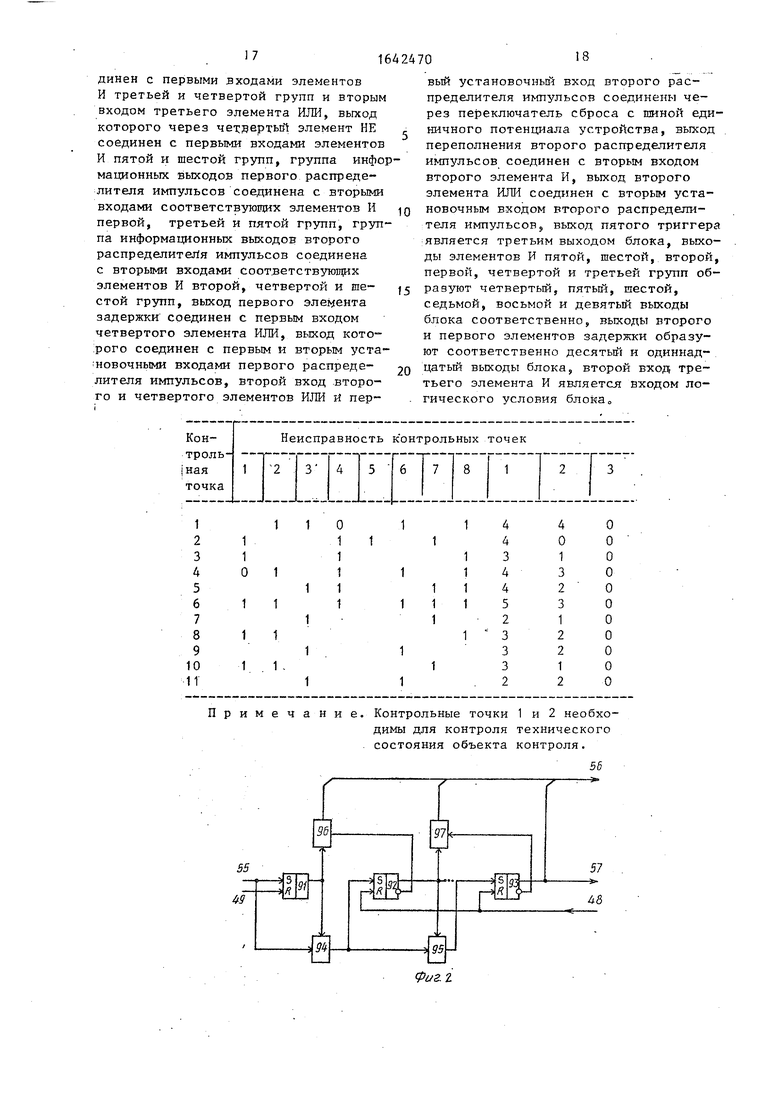

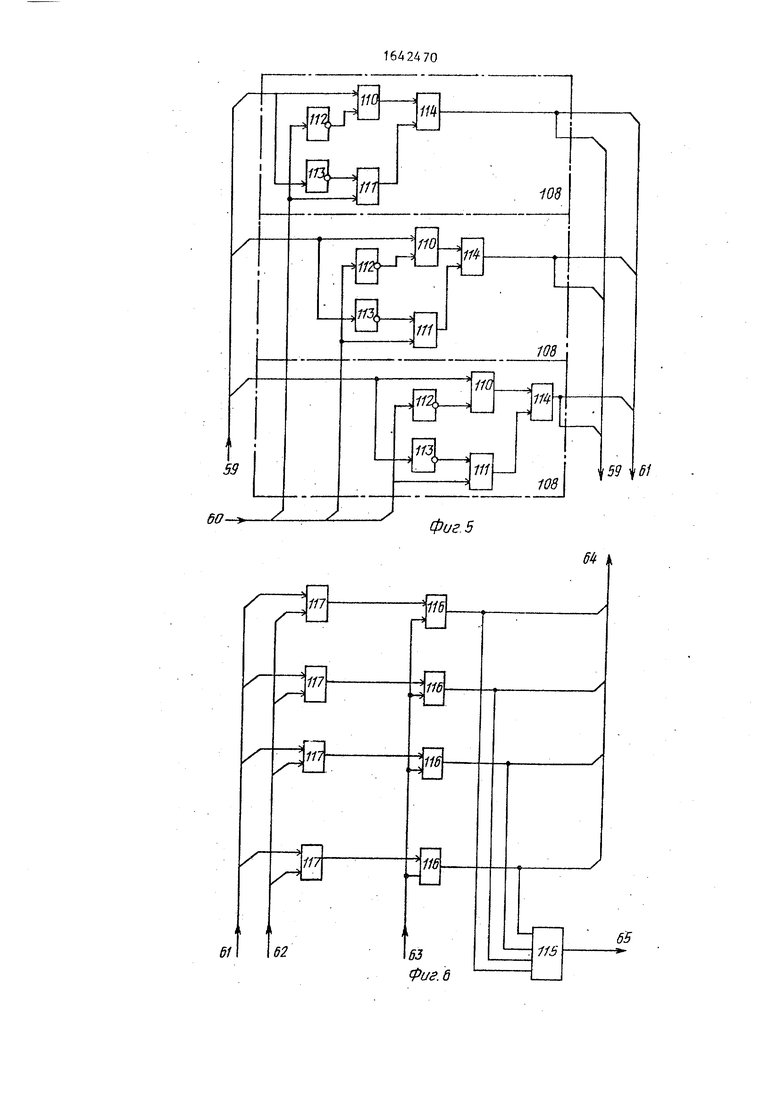

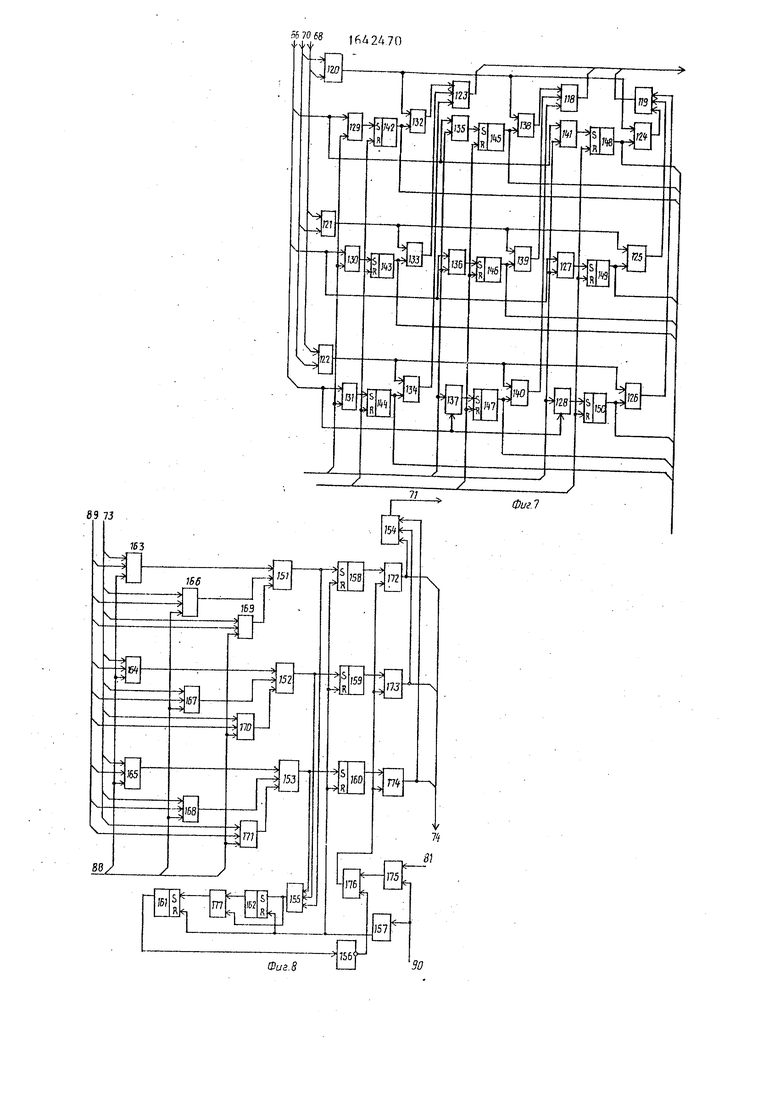

Целью изобретения является повышение производительности устройства„ На фиг о 1 приведена функциональная схема предлагаемого устройства; на фиг„ 2 - функциональная схема распределителя импульсов блока управления; на фиг. 3 - функциональная схема коммутатора; на фиг„ 4 - схема подключения блока имитации неисправностей к объекту контроля; на фиг о 5 - функциональная схема блока имитации неисправностей; на фиг„ 6 - функциональная схема первого блока сравнения; на фиг0 7 - функциональная схема первого блока памяти; на фиг 8 - функциональная схема блока коммутации; на фиг0 9 - функциональная схема второго блока сравнения; на фиг„ 10 - функциональная схема блока индикации„

Устройство (фиг о 1) содержит блок 1 управления, накопитель 2 выходных эталонов, накопитель 3 входных эталонов, коммутатор 4, блок 5 имитации неисправностей, второй блок 6 сравнения, первый и второй блоки 7 и 8 памяти соответственно, первый блок 9 сравнения, блок 10

0

5

0

5 индикации, блок 11 коммутации, распределители 12 и 13 импульсов блока 1 управления, переключатели 14 и 15 сброса и пуска соответственно блока 1 управления, группы 16-21 элементов И блока 1 управления, элементы НЕ 22-25 блока 1 управления, элементы 26-28 задержки блока 1 управления, элементы И 29-36 блока 1 управления, элементы ИЛИ 37-40 блока 1 управления, триггеры 41-45 блока 1 управления, генератор 46 тактовых импульсов блока 1 управления, объект 4 контроля (не входит в состав устройства), установочные входы 48 и 49 первого распределителя 12 импульсов, второй установочный вход 50, тактовый вход 51, группу 52 информационных выходов, выход 53 переполнения и первый установочный вход 54 второго распределителя 13 импульсов, тактовый вход 55, группу 56 информационных выходов и выход 57 переполнения перйого распределителя 12 импульсов, информационный выход 58 устройства для подключения к входу объекта 47 контроля, информационный вход-выход 59 устройства для подключения к входу-выходу объекта 47 контроля, адресный вход 60 блока 5 имитации неисправностей, информа5 ционные входы 61 и 62 второго блока 6 сравнения, тактовый вход 63 второго блока 6 сравне ния, группу 64 выходов несравнения

5

0

и обобщенный выход 65 несравнения второго блока 6 сравнения, группу 66 информационных входов и адресный вход 67 первого блока 7 памяти, второй вход 68 считывания первого блока 7 памяти, первый информационный вход 69 коммутатора 4, первый вход 70 считывания первого блока 7 памяти, установочный вход 71 блока 11 коммутации, установочньй вход 72 первого блока 7 памяти, второй информационный вход 73 блока 11 коммутации, информационный выход 74 блок t1 коммутации, информационный выход 75 первого блока 7 памяти, информационный выход 76 столбцов первого блока 7 памяти, информационные входы 77 и 78 первого блока 9 сравнения, тактовый вход 79 и выход 80 первого блока 9 сравнения, тактовый вход 81 блока 11 коммутации, второй и первый информационные входы 82 и 83 бло 10 индикации, входы 84 и 85 признака дефекта и конца работы блока 10 инди кации соответственно, установочньй вход 86 и тактовый вход 87 блока 10 индикации соответственно, адресный вход 88 блока 11 коммутации, первый информационный вход 89 и установочньй вход 90 блока 11 коммутации соответственно о

Первьй распределитель 12 импульсов (фиго 2) содержит триггеры 91- 93 и элементы И 94-97„ Коммутатор 4 (фиг„ 3) содержит элемент 98 задержки, элементы И 99- 101, элементы ИЛИ 102-104 и элементы И 105-1070

Блок 5 имитации неисправностей (фиг. 4) содержит группу узлов 108 имитации неисправностей. Объект 47 контроля содержит группу элементов 109.

Блок 5 имитации неисправностей (фиг„ 5) содержит элементы И 110 и 111, элементы НЕ 112 и 113 и элемент ИЛИ 114.

Второй блок 6 сравнения (фиг,, 6) содержит элемент ИЛИ 115,.группу 116 элементов И и группу 117 сумматоров по модулю два о

Первьй блок 7 памяти (фиг„ 7) содержит элементы ИЛИ 118-123, элементы 124-141 и триггеры 142-150„

Блок 11 коммутации (фиг.8) содержит элементы ИЛИ 151-155, элемент НЕ 156, элемент 157 задержки, триггеры 158-162 и элементы И 163-177„

10

15

20

25

424706

Первьй блок 9 сравнения (фиг„ 9) содержит сумматоры 178-180 по модулю два, элемент ИЛИ 181, элемент НЕ 182 и элемент И 183 о

Блок 10 индикации (фиг0 Ю) содержит элементы И 184-187, элементы ИЛИ 188-191, триггеры 192-197 и элементы 198-203 индикации„

Получение минимизированного количества контрольных точек происходит следующим образом

Пусть в контролируемом объекте Q имеется одиннадцать контрольных точек, с которых может сниматься контролируемая информация„

В контролируемом объекте возможны неисправности N, В реззтльтате подачи на контролируемый объект совокупности допустимых входные воздействий первая неисправность N- будет фиксироваться, выходная функция будет отличаться от эталонного значения на 2, 3, 8, 10 контрольных точкахj Неисправность будет фиксироваться на 1, 4, 6, 8, 10 контрольных точках0 По полученным результатам построим матрицу неисправностей (смо таблицу), столбцы которой соответствуют номерам неисправностей, а строки - номерам контрольных точек Если n-я неисправность фиксируется в 1-й контрольной точке, то на пересечении n-гс столбца и 1-й строки ставится единица, в противном случае - нуль.

Проведя суммирование единиц в каждой строке, определим, какое количество неисправностей фиксирует каждая контрольная точка

Для контролируемого объекта, в котором возможно возникновение та30

35

40

5

0

5

кой неисправности N1, которая фиксируется только одной контрольной точкой, последняя всегда входит в минимизированное количество контрольных точеко Для данного примера вторая контрольная точка фиксирует неисправность N,., которая не выявляется ни одной другой контрольной точкой Номер этой контрольной точки запоминается, а столбцы матрицы неисправностей, соответствующие но- мерам неисправностей, фиксируемых на данной контрольной точке, обнуляются, обнуляются столбцы N,, N4, N, N7,

После этого происходит второе суммирование единиц в каждой строке

и определяется контрольная точка, на которой фиксируется максимальное количество неисправностей, в данном случае выбираем первую контрольную точку, и вновь проводится обнуление столбцов таблицы в соответствии с информацией, принадлежащей контрольной точке, т,е„ обнуляются столбцы Ng, N3, Ng, Ngо На этом процесс обнуления матрицы неисправностей заг |канчивается „ В результате получается минимизированное количество контрольных точек, включающее 1 и 2 контроль

состояние„ С выхода 56 распределителя 12 сигнал поступает на группу 19 элементов И, на второй вход которой подается единичный сигнал с выхода элемента НЕ 22. Выходные сигналы с выходов группы 19 элементов И обеспечивают одновременное считывание информации, соответствующей первому входному воздействию, с накопителя 3 входных эталонов и с накопителя 2 выходных эталонов.

При этом блоком 6 сравнения производится сравнение выходных воздейст

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для построения диагностического теста и диагностирования комбинационных схем | 1983 |

|

SU1160420A2 |

| Устройство для имитации отказов дискретной аппаратуры | 1990 |

|

SU1815642A1 |

| Устройство для приема телесигналов | 1983 |

|

SU1137497A1 |

| Устройство для контроля и диагностики радиоэлектронной аппаратуры | 1986 |

|

SU1432463A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для формирования тестов диагностики дискретных блоков | 1983 |

|

SU1149265A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1401468A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при получении минимизированного количества контрольных точек, необходимого для определения технического состояния дискретной аппаратуры. Цель изобретения

ные точки. Анализируя выходные значе- 15 вий, поступающих от контролируемого

ния сигналов на полученных контрольных точках, можно определить техническое состояния контролируемого объекта с Если процесс обнуления матрицы неисправностей начинать с номера контрольной точки, фиксирующей максимальное количество неисправностей (для данного примера 6-я контрольная точка), то получим минимизированную

совокупность контрольных точек, вклю- 25 мого объекта 47, поэтому задание нечающую 6,2, 1 контрольные точки Поэтому получение минимизированной совокупности контрольных точек является более эффективным, если обнуление матрицы неисправностей начинать с контрольной точки, фиксирующей такую Nj неисправность, которая проявляется только на данной контрольной точке„

Устройство работает следующим образом.

Перед началом работы нажатием переключателя 14 сброса выдается сигнал, устанавливающий в нулевое состояние все триггеры устройства, при этом этот сигнал через элементы ИЛИ 38 и 39 поступает на входы 48 и 49 первого распределителя 12 импульсов, на входы 50 и 54 второго распределителя

исправности контролируемому объекту 47 блоком 5 имитации неисправностей не проводится

В случае несовпадения сравнивае- 30 мой информации на выходе 65 блока 6 сравнения появляется сигнал, который открывает элемент И 35 и тем самым переводит триггер 45 в единичное состояние. Выходной сигнал триггера 45 поступает на вход 84 блока 10 индикации о В блоке 10 загорается транспарант, сигнализирующий о наличии дефекта в объекте 47. Одновременно этот сигнал.проходя через элемент ИЛИ 36 и элемент НЕ 23, закрывает элементы И 29 и 31,запрещая прохождение импульсов с генератора 46 на распределитель 12 импульсов.

Если контролируемый объект 47

35

40

13 импульсов и переводит его триггеры исправен, то при поступлении п-го в нулевое состояние. Одновременно импульса переводится в единичное сос- этот сигнал устанавливает элементы тояние n-й триггер распределителя 12

импульсов, обеспечивающий задание контролируемому объекту 47 последнеблока 7 памяти и блока 10 индикации в нулевое состояние„

При переводе переключателя 15 пус- „ го n-го входного воздействия с блока

ка в положение Включено открывается элемент И 29 и с его выхода снимается сигнал, подготавливающий элемент И 31 к открытиюо С приходом импульса от генератора 46 импульсов на выходе элемента И 31 появится сигнап, который поступает на вход 55 первого распределителя 12 (фиг. 2)о Этот сигнал переводит триггер 91 в единичное

55

выходного сигнала с блока 2 о

Через время задержки , определяемое элементом 26, сигнал снимаемы с выхода 57 распределителя 12 импуль сов, переводит триггер 44 в единично состояние, что приводит к закрытию элемента И 36. Одновременно этот сигнал через элемент ИЛИ 39 устанавобъекта 47 с эталонными выходными воздействиями, поступающими от блока 2.

Аналогичным образом устройство работает при поступлении на вход первого распределителя 12 импульсов очередного импульса от генератора 46с

В этот период работы устройства проверяется исправность контролируеисправности контролируемому объекту 47 блоком 5 имитации неисправностей не проводится

В случае несовпадения сравнивае- 0 мой информации на выходе 65 блока 6 сравнения появляется сигнал, который открывает элемент И 35 и тем самым переводит триггер 45 в единичное состояние. Выходной сигнал триггера 45 поступает на вход 84 блока 10 индикации о В блоке 10 загорается транспарант, сигнализирующий о наличии дефекта в объекте 47. Одновременно этот сигнал.проходя через элемент ИЛИ 36 и элемент НЕ 23, закрывает элементы И 29 и 31,запрещая прохождение импульсов с генератора 46 на распределитель 12 импульсов.

Если контролируемый объект 47

5

0

5

выходного сигнала с блока 2 о

Через время задержки , определяемое элементом 26, сигнал снимаемый с выхода 57 распределителя 12 импульсов, переводит триггер 44 в единичное состояние, что приводит к закрытию элемента И 36. Одновременно этот сигнал через элемент ИЛИ 39 устанавливает распределитель 12 импульсов в нулевое состояние. Одновременно он поступает на вход 51 распределителя 13 импульсов и переводит первый триггер в единичное состояние В этом случае сигнал, снимаемый с выхода 52 распределителя импульсов через группу 16 элементов И поступает на блок 5 имитации неисправностей Этот блок по этой команде обеспечивает ввод первой неисправности в контролируемый объект 47о Этот же сигнал, поступая на адресный вход 67 (фиг„ 7) блока 7 памяти, подготавливает к откры

тию элементы 129, 130 и 131 .Тем самым создаются условия для перевода в единичное состояние группы триггеров 142, 143 и 144 номера которых соответствуют номерам контрольных точек контролируемого объекта 47, на которых будет фиксироваться первая неисправность

При поступлении импульса на вход распределителя 12 импульсов от гене- ратора 46 последний обеспечивает считывание входных и выходных воздействий с блоков 2 и 3 Блоком 6 сравнения производится сравнение информаци снимаемой с контрольных точек конт- ролируемого объекта 47 с информацией снимаемой с блока 2. При этом в случае несовпадения значения, снимаемого с i-й контрольной точки со значением, поступающим с блока 2, появля-.,. второй вход поступает сигнал с выхода

uf ОA

45

ется единичный сигнал на соответствующем разряде выхода 64 (фиг 6)„ Этот сигнал поступает на вход 66 первого блока 7 памяти и переводит в единичное состояние те триггеры (из группы д0 триггеров 142-144), номера которых соответствуют номерам контрольных точек, на которых появляется введенная неисправность После подачи всох входных воздействий при введенной первой неисправности сигнал, снимаемый с выхода элемента 26 задержки, поступает на распределитель 13 импульсов, который обеспечивает задание контролируемому объекту 47 второй неисправности Этот же сигнал, поступая на вход 67 блока 7 памяти, подготавливает к открытию элементы И 135, 136 и 137 Далее устройство работает аналогичным образом

Таким образом, в первом блоке 7 памяти будет записана матрица неисправностей контролируемого объекта 47, в котором номера триггеров 14250

55

53 распределителя 13 импульсов (с выхода К-го триггера), Сигнал, снимаемый с выхода элемента И 32, переводит триггер 41 в единичное состояние Его выходной сигнал через открытый элемент И 34 подготавливает к открытию шестую группу 21 и вторую группу 17 элементов И к открытию. Этот же сигнал через элемент ИЛИ 40 и элемент НЕ 22 закрывает первую группу 16 и четвертую группу 19 элементов И„ Этим же сигналом , поступающим на вход 81 блока 11 коммутации, подготавливается к открытию элемент И 175 (фиг, 8) Одновременно сигнал с выхода элемента И 32 через элемент ИЛИ 38 поступает на вход 50 распределителя 13 импульсов и устанавливает его триггеры в нулевое состоя ние

Первый триггер 91 остался в единичном состоянии, при этом его CHI- нал поступает на вход группы 17 элементов И Ее выходные сигналы посту10

15

20

25 , 30 ,

64247010

144 соответствуют номерам контрольных точек.

При задании К-ой неисправности переводится в единичное состояние К-й триггер распределителя 13 импульсов

При этом в единичном состоянии будут находиться те триггеры, номера которых соответствуют номерам контрольных точек, на которых фиксируется первая неисправность, состояния рассматриваемых триггеров обеспечивают реализацию первого столбца, матрицы неисправностей.

Аналогичным образом состояния триггеров 145-147 определяют второй столбец матрицы неисправностей и т,д.

Если i-я неисправность фиксируется одной контрольной точкой, то эта контрольная точка всегда входит в минимизированную совокупность контрольных точек

Определение таких контрольных точек в устройстве осуществляется следующим образом

После того, как распределитель 12 импульсов обеспечит задание всех входных и выходных воздействий при введении К-ой неисправности, сигнал,снимаемый с распределителя 12 импульсов, через элемент 26 задержки поступает на первый вход элемента И 32, на его

f ОA

5

0

0

5

53 распределителя 13 импульсов (с выхода К-го триггера), Сигнал, снимаемый с выхода элемента И 32, переводит триггер 41 в единичное состояние Его выходной сигнал через открытый элемент И 34 подготавливает к открытию шестую группу 21 и вторую группу 17 элементов И к открытию. Этот же сигнал через элемент ИЛИ 40 и элемент НЕ 22 закрывает первую группу 16 и четвертую группу 19 элементов И„ Этим же сигналом , поступающим на вход 81 блока 11 коммутации, подготавливается к открытию элемент И 175 (фиг, 8) Одновременно сигнал с выхода элемента И 32 через элемент ИЛИ 38 поступает на вход 50 распределителя 13 импульсов и устанавливает его триггеры в нулевое состоя ние

Первый триггер 91 остался в единичном состоянии, при этом его CHI- нал поступает на вход группы 17 элементов И Ее выходные сигналы посту111

пают на вход 88 блока 11 коммутации, подготавливая элементы И 163, 164, 165 к открытию. Как только от генератора 46 поступит импульс на вход распределителя 12 импульсов, то переводится в единичное состояние триггер 91. Его выходной сигнал через шестую группу 21 элементов И поступает на вход 89 блока 11 коммутации, подготавливая его элементы к открытию (фиг о 8) или открывает их„ Если на второй вход с входа 89 элемента И 163 поступает единичный сигнал (триггер 142 находится в единичном состоянии, причем его номер соответствует номеру первой контрольной

точки, которая в данном случае фиксирует первую неисправность, то он через элемент ИЛИ 151 переводит триггер 158 в единичное состояние0 Этот же сигнал через элемент ИЛИ 155 переводит триггер 162 в единичное состояние

С приходом очередного импульса на вход первого распределителя 12 импульсов, подготавливается к от1- крытию элемент И 164, к второму входу которого подключен выход триггера 143 (соответствующему номеру

ВТОРОЙ КОНТРОЛЬНОЙ ТОЧКИ) И Т„До

Если окажется, что первая неисправность фиксируется только на одной контрольной точке, например на 1-й, то в блоке 11 коммутации окажется в единичном состоянии только триггер 158, При этом с переводом триггера 93 (фиг 2) в единичное состояние на входе 90 блока 11 коммутации появится единичный сигнал. Элемент И 175 открывается и его выходной сигнал через открытый элемент И 176 подготавливает к от крытию элементы И 172, 173, 174 Однако в данном случае открбется то- лько элемент И 172, номер которого соответствует номеру первой контрольной точки. Сигнал с выхода элемента И 172 поступает на блок .109 где фиксируется первая контрольная точка, и на вход 70 первого блока 7 памяти (на вход элемента ИЛИ 120)„ Это обеспечивает считывание информации с триггеров 142, 145, 148, характеризующей первую контрольную точку

Единичные сигналы с выходов триггеров 142, 145, 148 через соответствующие элементы ИЛИ 123, 124, 125 поступают на вход 69 коммутатора 4

12

0

5

0

5

0

5

0

5

0

5

и открывают соответствующие элементы И 99, 100, 101„ Их«выходные сигналы поступают на входы элементов ИЛИ 102т104, выходы которых устанавливают соответствующие триггеры блока 7 памяти в нулевое состояние, т„е. происходит обнуление информации в соответствии с информацией, соответствующей первой контрольной точке

Если окажется, что первая неисправность фиксируется более, чем на одной контрольной точке, то в этом случае переводится в единичное состояние триггер 161 блока 11 коммутации,, Его выходной сигнал закрывает элемент И 176, что обеспечивает запрещение считывания информации с блока 11 коммутации. В этом случае, с приходом сигнала на вход 90 через время задержки t , определяемое элементом задержки 157, триггеры блока 11 коммутации устанавливаются в нулевое состояние0 После проведения анализа состояний контрольных точек при введенной первой неисправности переводится в единичное состояние триггер 92 распределителя 13 импульсов Его выходной сигнал через вторую группу 17 элементов И подготавливает к открытию элементы И 166, 167, 168 блока 11 коммутации (фиг 8)„ Далее устройство работает аналогичным образом После того, как будет закончено определение контрольных точек, обязательно входящих в минимизированную совокупность контрольных точек, начинается работа устройства по определению контрольных точек, несущих максимальное количество информации

В этом случае с переводом триггеров 93 распределителей 12 и 13 в единичное состояние открывается элемент И 32 и его выходной сигнал переводит в единичное состояние триггер 42 Его выходной сигнал открывает элемент И 37 (элемент И 34 закрыт) Выходной сигнал элемента И 37 подготавливает к открытию третью группу 18 и пятую группу 20 элементов И

Элемент И 30 остается в закрытом состоянии, так как сигнал, поступающий с выхода элемента И 32 на его ервый вход, не совпадает по времени с сигналом, снимаемым с выхода триггера 42 (к моменту его поступления закрывается элемент И 32)„

В этот период работы сигнал, снимемый с выхода триггера 91 распределителя 13 импульсов, через третью группу 18 элементов И обеспечивает считывание информации с второго блока 8 памяти. Эта информация соответствует первому n-разрядному числу, содержащему максимальное количество единицо

При поступлении импульсов на вход распределителя 12 импульсов на его выходе начинают формироваться импульсы, которые поступают на вход группы 20 элементов И. На их выхо- дах появляются сигналы, которые поступают на вход 68 первого блока 7 памяти и обеспечивают поочередное считывание информации, характеризующей каждую контрольную точку (триг- геры 142, 145, 148 - первую триггер 143, 146, 149 - вторую и т„дд)0 Информация, считываемая с первого 7 и второго 8 блоков памяти, сравнивается в блоке 9 сравнения о

Если информация, считываемая с первого блока 7 памяти совпадает с информацией, считываемой с второго блока 8 памяти, то сигнал, снимаемый с выхода 80, поступает на вход коммутатора 4 и через время Ј , определяемое элементом 98 задержки, подготавливает к открытию элементы И 99-1010 При этом информация с блока 8 памяти поступает на вход 69 кбммутатора 4. Сигналы, соответствующие логическим единицам, открывают элементы И 99-101 и через элементы ИЛИ 102-104 устанавливают в нулевое состояние те триггеры первого блока 7 памяти, номера которых соответствуют единичным разрядам информации, поступающей от блока 8 памяти,

Одновременно сигнал, снимае ый с выхода блока 9 сравнения, поступа- ет на блок 0 индикации и подготавливает к открытию элементы И 184- 187, При этом открывается лишь тот элемент И, номер которого соответствует номеру анализируемой контроль- ной точки„

После того, как будет считана вся информация с первого блока 7 памяти, распределитель 13 импульсов обеспечивает считывание с второго блока 8 памяти n-разрядного числа, содержащего на единицу меньше„ Далее устройство работает аналогичным образом

10

Q 5

о Q

- 0

5

5

После того, как с второго блока 8 памяти будет считано последнее п- разрядное число, содержащее одну единицу, и проведено сравнение с информацией, поступающей с первого блока 7 памяти, на выходе элемента И 30 появляется сигнал, который переводит триггер 43 в единичное состояние. Его сигнал, через элемент И 35 и элемент НЕ 23 закрывает элемент И 29,тем самым прекращается подача импульсов от генератора 46 на распределитель 12 импульсов о Одновременно этот сигнал поступает на блок 10 иштикации и обеспечивает высвечивание транспаранта Конец работы 0

Получение минимизированной совокуп- ности контрольных точек позволяет повысить надежность проектируемой системы, так как в этом случае сокращается количество элементов аппаратуры контроля, подключаемых к контрольным точкам объекта диагностирования для проверки значений выходных сигналов его блоков„

Формула изобретения

1 о Устройство для контроля дискретных объектов, содержащее блок управления, первый блок памяти, первый блок сравнения и блок индикации, причем выход несравнения первого , блока сравнения соединен с тактовым входом блока индикации, о т л и - чающееся тем, что, с целью повышения производительности устройства, в него введены второй блок памяти, второй блок сравнения, блок коммутации, блок имитации неисправностей, накопитель входных эталонов, накопитель выходных эталонов, коммутатор, причем первый выход блока управления соединен с установочным входом блока индикациии, второй и третий выходы блока управления соединены с входами признаков дефекта и конца работы блока индикации соответственно, четвертый выход блока управления соединен с адресными входами накопителей входных и выходных эталонов, информационный выход накопителя входных эталонов является, информационным выходом устройства для подключения к входам объекта контроля, вход-выход блока имитации неисправностей является информационным входом-выходом устройства для

подключения к входу-выходу объекта контроля, пятый выход блока управления соединен с адресными входами первого блока памяти и блока имитации неисправностей, информационные выход блока имитации неисправностей и накопителя выходных эталонов соединены соответственно с первым и вторым информационными входами второго блока сравнения, выход несравнения которог соединен с входом логического услови блока управления, группа выходов несравнения второго блока сравнения соединена с группой информационных входов первого блока памяти, установочный вход которого соединен с выходом коммутатора, шестой и седьмой выходы блока управления и информационный выход первого блока памяти соединены соответственно с адресным и первым и вторым информационными входами блока коммутации, информационный выход которого соединен с первым информационным входом блока индикации и первым входом считывания первого блока памяти, восьмой выход блока управления соединен с адресным входом второго блок а памяти информационный выходкоторого соеди- нен с вторым входом считывания первого блока памяти и первым информационным входом первого блока сравнения , девятый выход блока управления соединен с вторым информацион- ным входом первого блока сравнения и первым информационным входом коммутатора, информационный выход столбцов первого блока памяти соединен с вторыми информационными входами пер- вого блока сравнения и коммутатора, десятый и одиннадцатый выходы блока управления соединены с установочным входом блока коммутации и тактовыми входами блоков сравнения соответст- венно, первый выход блока управления и выход несравнения первого блока сравнения соединены с первым и вторым управляющими входами -коммутатора соответственно, информационный выход блока коммутации соединен с третьим информационным входом коммутатора „

5 0 5 0 5 о 5

0

5

элементов И, четыре элемента ИЛИ, два распределителя импульсов и шесть групп элементов И, причем установочные входы всех триггеров блока и первый выход блока через переключатель сброса подключены к шине единичного потенциала устройства, выход генератора тактовых импульсов соединен с входом первого элемента задержки и первым входом первого элемента И, выход которого соединен с тактовым входом первого распределителя импульсов, выход переполнения которого через второй элемент задержки соединен с тактовым входом второго распределителя импульсов, единичным выходом первого триггера и первым входом второго элемента И, прямой выход первого триггера через первый элемент НЕ соединен с первым входом третьего элемента И, выход которого соединен с единичным входом второго триггера, прямой выход которого соединен с первым входом первого элемента ИЛИ и подключен к второму выходу блока, выход первого элемента ИЛИ через второй элемент НЕ соединен с первым входом четвертого элемента И, выход которого соединен с вторым входом первого элемента И, второй вход четвертого элемента И через переключатель пуска соединен с шиной единичного потенциала устройства, выход второго элемента И соединен с единичным входом третьего триггера, первым входом второго элемента ИЛИ и первыми входами пятого и шестого элементов И, выходы которых соединены с единичными входами четвертого и пятого триггеров соответственно, прямой выход третьего триггера соединен с вторым входом пятого элемента И и первыми входами седьмого и восьмого элементов И, прямой выход четвертого триггера соединен с входом третьего элемента задержки, вторым входом восьмого элемента И и входом третьего элемента НЕ, выход которого соединен с вторым входом седьмого элемента И, выход третьего элемента задержки соединен с вторым входом шестого элемента И, прямой выход пятого триггера соединен с вторым входом первого элемента ИЛИ, выход седьмого элемента И соединен с первыми входами элементов И первой и второй групп и первым входом третьего элемента ИЛИ, выход восьмого элемента И соединен с первыми входами элементов И третьей и четвертой групп и вторым входом третьего элемента ИЛИ, выход которого через четвертый элемент НЕ соединен с первыми входами элементов И пятой и шестой групп, группа информационных выходов первого распределителя импульсов соединена с вторыми входами соответствующих элементов И первой, третьей и пятой групп, группа информационных выходов второго распределителя импульсов соединена с вторыми входами соответствующих элементов И второй, четвертой и me- стой групп, выход первого элемента задержки соединен с первым входом четвертого элемента ИЛИ, выход которого соединен с первым и вторым установочными входами первого распреде- лителя импульсов, второй вход второго и четвертого элементов ИЛИ и перПримечание.

вый установочный вход второго распределителя импульсов соединены через переключатель сброса с шиной единичного потенциала устройства, выход переполнения второго распределителя импульсов соединен с вторым входом второго элемента И, выход второго элемента ИЛИ соединен с вторым установочным входом второго распределителя импульсовj выход пятого триггера является третьим выходом блока, выходы элементов И пятой, шестой, второй, первой, четвертой и третьей групп образуют четвертый, пятый, шестой, седьмой, восьмой и девятый выходы блока соответственно, выходы второго и первого элементов задержки образуют соответственно десятый и одиннадцатый выходы блока, второй вход третьего элемента И является входом логического условия блока

Контрольные точки 1 и 2 необходимы для контроля технического состояния объекта контроля.

56

71 76

I

(

86

69

во

60

59

109

§

I

-

s 1(

Г4

EIH rCd -Л

фиг.З

i

61

59

109

фигЛ

59

Stt9 глф Ј9

ш

9 глф

IS

65

Ш

-Ш

ои

VI

ш

OiKWl

га

IQ

Z//:

-OQ

йУ

Н

/

r-Ш

vT

I68 1M2470

jzff|,/L

tit -i

Ш

г-i

П°

S7

s

/53

1-Я

ГП И

k| ц-jg

Фиг 8

tit -i

R

Ш

W

r-5

го

й

т

я

«Я

ll

Ш

я

s tH«

R

7/

Фиг

/72

75бр

55

78 77

| 0 |

|

SU402869A1 |

Авторы

Даты

1991-04-15—Публикация

1988-03-09—Подача