Изобретение относится к вычислительной технике, а более конкретно, к запо- минающим устройствам и может быть использовано при разработке асинхронного двухпортового ОЗУ.. ;

Цель изобретения - обеспечение возможности, записи или считывания по разным адресам и одновременного считывания по одному адресу.

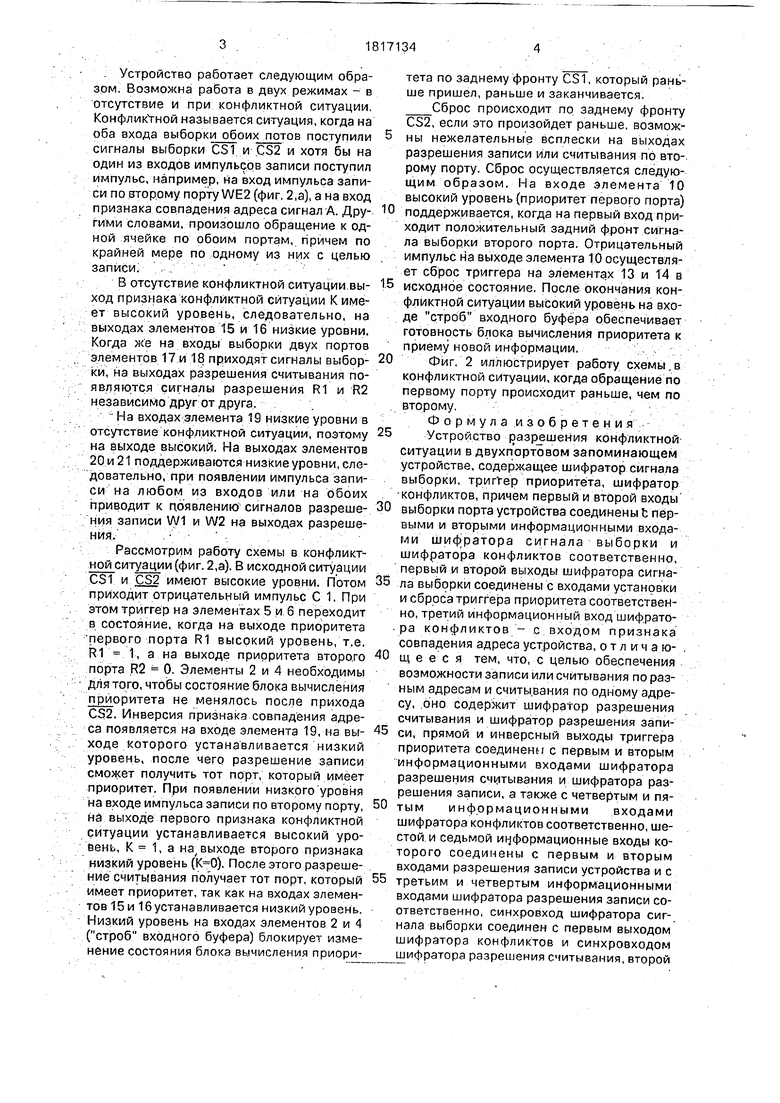

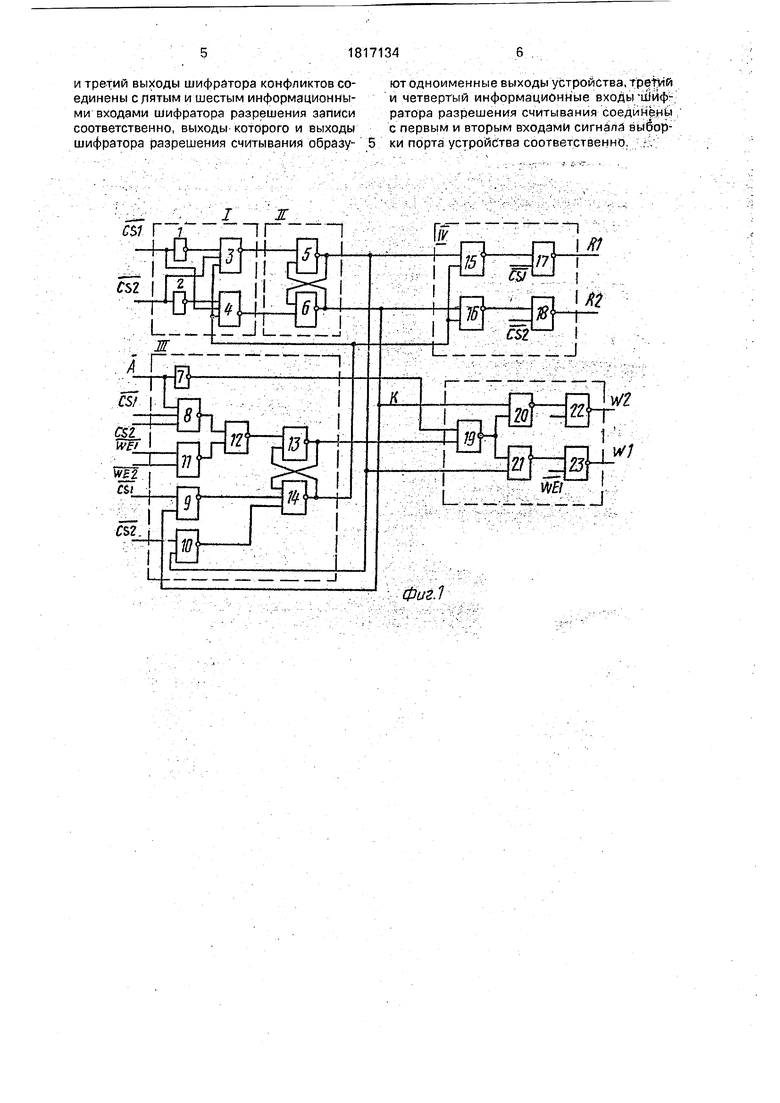

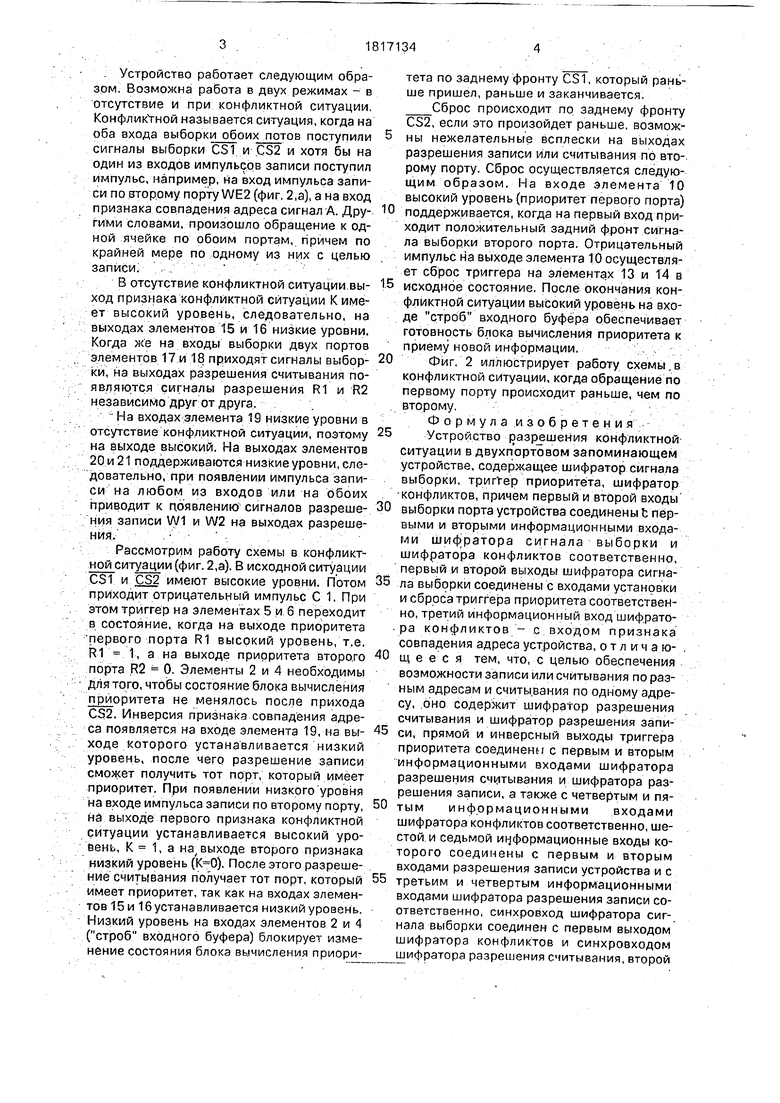

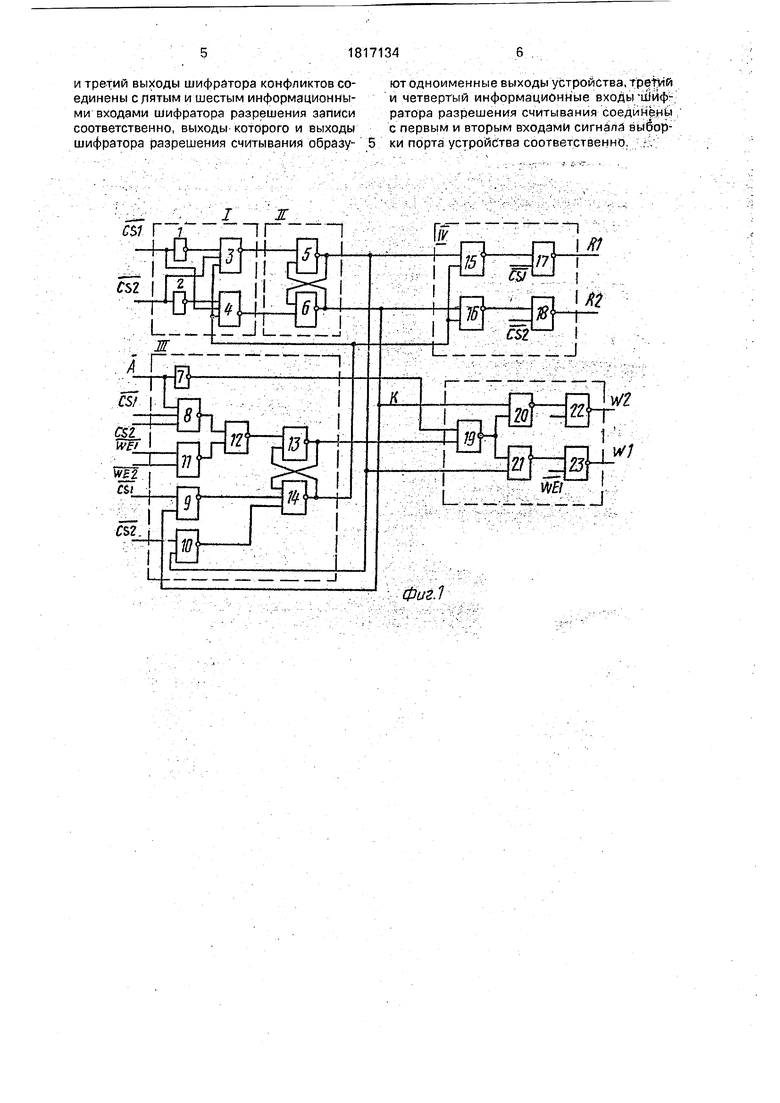

На фиг. 1 изображено устройство разрешения конфликтной ситуации; на фиг. 2 - временные диаграммы, поясняющие работу устройства при конфликтной ситуации, ког- ;да первый порт обращается к ЗУ раньше, второго На фиг. 2а первый порт обращается, чтобы считать, а второй - записать, на фиг. 26, оба порта обращаются для записи, а на фиг, 2в первый порт обращается для записи, а второй для считывания.

Условные обозначения:

CS1 и CS2 - сигналы выборки портов;

WE1 и WE2 - импульсы записи; А - признак совпадений адреса; К - второй признак конфликтной ситуаел

с

ции; .;- - .- -..-; ....-../.

R1 и R2 - разрешение считывания;

W1 и W2 - разрешение записи; К-первый признак конфликтной ситуации

Устройство разрешения конфликтной ситуации (фиг. 1) состоит из шифратора сигналов выборки, включающего в себя элементы НЕ 1, 2 и элементы И-НЕ 3, 4, триггера приоритета включающего в себя элементы И-НЕ 5, б, шифратора конфликтов, включающего в себя элемент НЕ 7, элемент И Л И-НЕ 8 и элементы И-НЁ 9-14, шифратора разрешения считывания, включающего, в себя элементы ИЛИ-НЕ 15-18, шифратора разрешения записи, включаю-, щего в себя элементы ИЛИ-НЕ 19-23.

СлЭ Јь

. Устройство работает следующим образом. Возможна работа в двух режимах - в отсутствие и при конфликтной ситуации. Конфликтной называется ситуация, когда на оба входа выборки обоих потов поступили сигналы выборки CS1 и CS2 и хотя бы на один из входов импульсов записи поступил импульс, например, на вход импульса записи по второму порту WE2 (фиг. 2,а), а на вход признака совпадения адреса сигнал А. Другими словами, произошло обращение к одной ячейке по обоим портам, причем по крайней мере по одному из них с целью записи; . ,-.. V .. ;

В отсутствие конфликтной ситуации.выход признака конфликтной ситуации К имеет высокий уровень, следовательно, на выходах элементов 15 и 16 низкие уровни. Когда же на входы выборки двух портов элементов 17 и 18 приходят сигналы выбор- ки, на выходах разрешения считывания появляются сигналы разрешения R1 и R2 независимо друг от друга.

На входах элемента 19 низкие уровни в отсутствие конфликтной ситуации, поэтому на выходе высокий. На выходах элементов 20 и 21 поддерживаются низкие уровни, следовательно, при появлении импульса записи на любом из входов или на обоих приводит к появлению сигналов разрешения записи W1 и W2 на выходах разрешения, .

Рассмотрим работу схемы в конфликтной ситуации (фиг. 2,а). В исходной ситуации CS1 и CS2 имеют высокие уровни. Потом приходит отрицательный импульс С 1. При этом триггер на элементах 5 и 6 переходит в состояние, когда на выходе приоритета первого порта R1 высокий уровень, т.е. R1 1, а на выходе приоритета второго порта R2 0. Элементы 2 и 4 необходимы длятого, чтобы состояние блока вычисления приоритета не менялось после прихода CS2. Инверсия признака совпадения адреса появляется на входе элемента 19, на выходе которого устанавливается низкий уровень, после чего разрешение записи сможет получить тот порт, который имеет приоритет. При появлении низкого уровня на входе импульса записи по второму порту, на выходе первого признака конфликтной ситуации устанавливается высокий уровень, К 1, а нау выходе второго признака низкий уровень (К-0). После этого разрешение считывания получает тот порт, который имеет приоритет, так как на входах элементов 15 и 16 устанавливается низкий уровень. Низкий уровень на входах элементов 2 и 4 (строб входного буфера) блокирует изменение состояния блока вычисления приори

1й

10

1.5

20

25 30

35

40

45

50

55

тета по заднему фронту CS1, который раньше пришел, раньше и заканчивается. Сброс происходит по заднему фронту CS2, если это произойдет раньше, возможны нежелательные всплески на выходах разрешения записи или считывания по второму порту. Сброс осуществляется следующим образом. На входе элемента 10 высокий уровень (приоритет первого порта) поддерживается, когда на первый вход приходит положительный задний фронт сигнала выборки второго порта. Отрицательный импульс на выходе элемента 10 осуществляет сброс триггера на элементах 13 и 14 в исходное состояние. После окончания конфликтной ситуации высокий уровень на входе строб входного буфера обеспечивает готовность блока вычисления приоритета к приему новой информации..- . : Фиг. 2 иллюстрирует работу схемы.в конфликтной ситуации, когда обращение по первому порту происходит раньше, чем по

ВТОрОМу. . ; : . ; .

Формула .изобретен и я

Устройство разрешения конфликтной

ситуации в двухпортовом запоминающем

устройстве, содержащее шифратор сигнала

выборки, триггер приоритета, шифратор

конфликтов, причем первый и второй входы выборки порта устройства соединены t первыми и вторыми информационными входами шифратора сигнала выборки и шифратора конфликтов соответственно, первый и второй выходы шифратора сигнала выборки соединены с входами установки и сброса триггера приоритета соответственно, третий информационный вход шифрато. ра конфликтов - с входом признака совпадения адреса устройства, отличающееся тем, что, с целью обеспечения возможности записи или считывания по разным адресам и считывания по одному адресу, .оно содержит шифратор разрешения считывания и шифратор разрешения записи, прямой и инверсный выходы триггера приоритета соединены с первым и вторым информационными входами шифратора разрешения считывания и шифратора разрешения записи, а также с четвертым и пятым информационными входами шифратора конфликтов соответственно, шестой, и седьмой информационные входы которого соединены с первым и вторым входами разрешения записи устройства и с третьим и четвертым информационными входами шифратора разрешения записи соответственно, синхровход шифратора сигнала выборки соединен с первым выходом шифратора конфликтов и синхровходом

шифратора разрешения считывания, второй

и третий выходы шифратора конфликтов соединены слятым и шестым информационными входами шифратора разрешения записи соответственно, выходы которого и выходы

ют одноименные выходы устройства, трети и четвертый информационные входы ш й ратора разрешения считывания соединен с первым и вторым входами сигнала выбо

шифратора разрешения считываний образу- 5 ки порта устройс тва соответственно, гг.

ют одноименные выходы устройства, третий и четвертый информационные входы ш йф1- ратора разрешения считывания соединены с первым и вторым входами сигнала выбор1817134

: ; . ,...--. - --

Ј5/ --- L

rSZ ----J ---LJ.1--L-..-.dfz.--,

ж Д

я

ЈS

csz &)Ј/

6/5Z

Д

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ АРБИТРАЖА ДОСТУПА ГРУППЫ АБОНЕНТОВ К ОБЩИМ РЕСУРСАМ | 1999 |

|

RU2153775C1 |

| СПОСОБ И УСТРОЙСТВО ПЕРЕДАЧИ ДАННЫХ МЕЖДУ ПЕРИФЕРИЙНЫМИ УСТРОЙСТВАМИ И ГЛАВНЫМ БЛОКОМ | 1992 |

|

RU2113764C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОДНОВРЕМЕННОЙ ВЫБОРКОЙ НЕСКОЛЬКИХ СЛОВ | 1990 |

|

RU2022371C1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| УСТРОЙСТВО ДЛЯ ОПТИМИЗАЦИИ ОРГАНИЗАЦИИ ДОСТУПА К ОБЩЕЙ ШИНЕ ВО ВРЕМЯ ПЕРЕДАЧИ ДАННЫХ С ПРЯМЫМ ДОСТУПОМ К ПАМЯТИ | 1991 |

|

RU2110838C1 |

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Многопортовое запоминающее устройство | 1990 |

|

SU1758648A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1989 |

|

SU1667090A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ МАТРИЦЫ НЕПОЛНОГО ПАРАЛЛЕЛИЗМА | 2009 |

|

RU2421804C2 |

Изобретение относится к вычислительной технике, а более конкретно к запоминающим устройствам, и м.б. использовано при разработке асинхронного двухпортового ОЗУ Цель изобретения - обеспечение возможности записи и считывания по разным адресам и одновременного считывания по одному адресу. Устройство содержит шифратор сигналов выборки, триггер приоритетам шифратор конфликтов, шифратор разрешения считывания. Устройство рабо- 1 тает в отсутствие.и при конфликтной ситуации. 2 ил.

ш

CSZ

№1

-.

А и/7

6

Фиг.1

| СПОСОБ ПОЛУЧЕНИЯ 2,2',2"-АМИНОТРИАЛКОКСИСИЛАНОВ, СОДЕРЖАЩИХ СВЯЗЬ Si—Н | 0 |

|

SU192209A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Патент США № 4620118 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-05-23—Публикация

1990-03-05—Подача