Изобретение относится к автоматике и вычислительной технике и предназначено для передачи информации в автоматизированных системах управления медленно текущими процессами.

Цель изобретения - сокращение аппаратурных затрат.

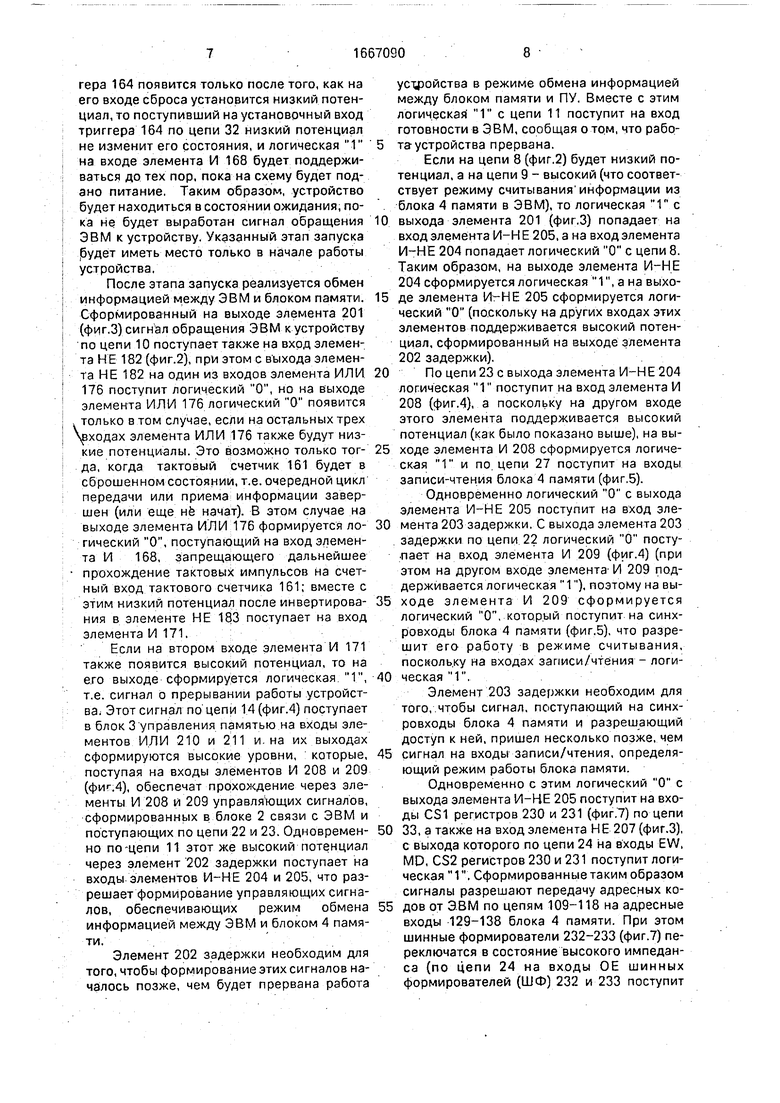

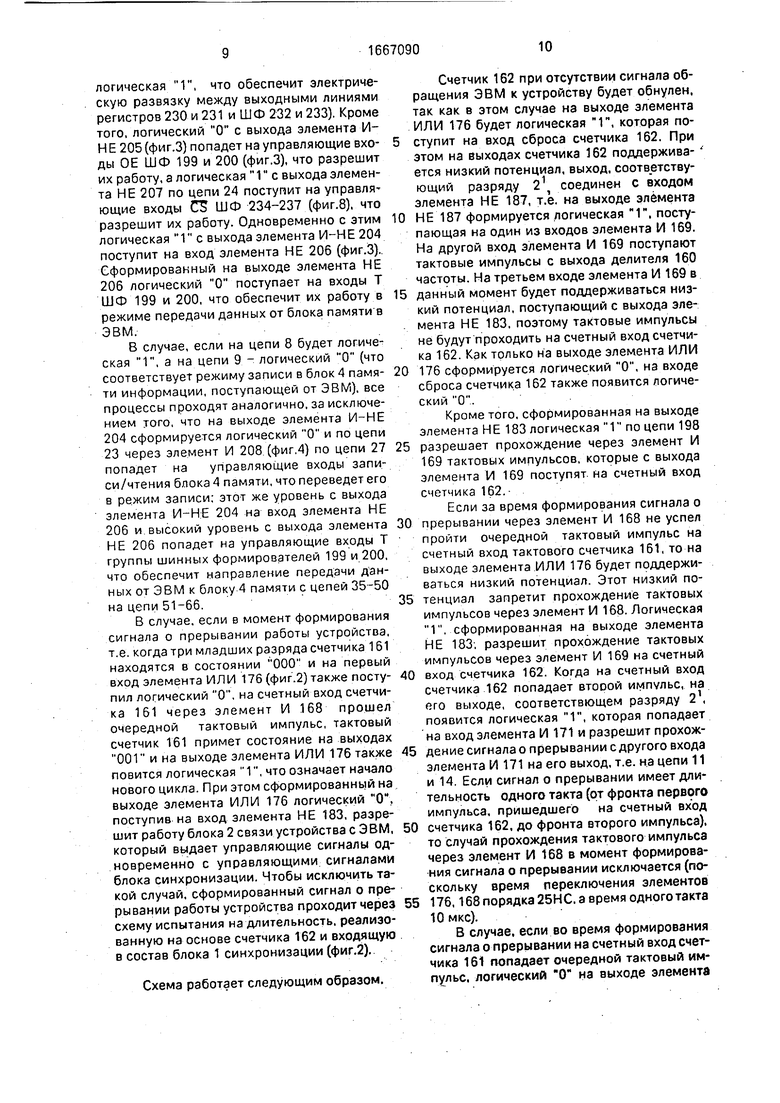

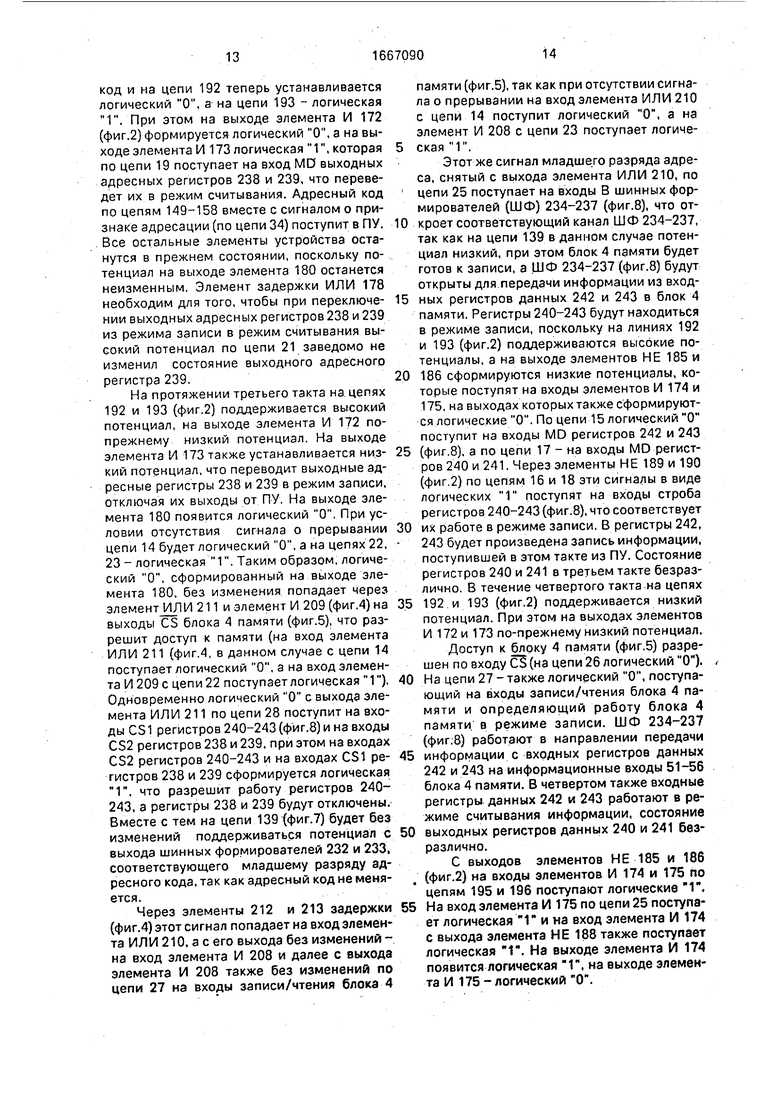

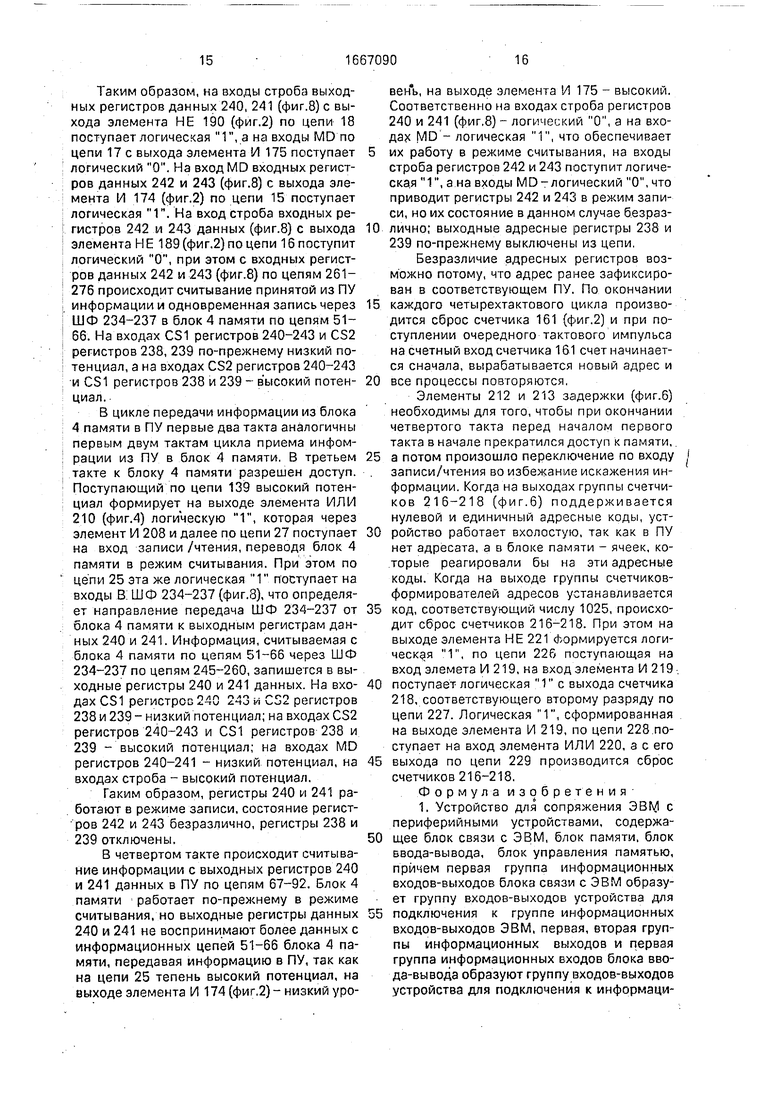

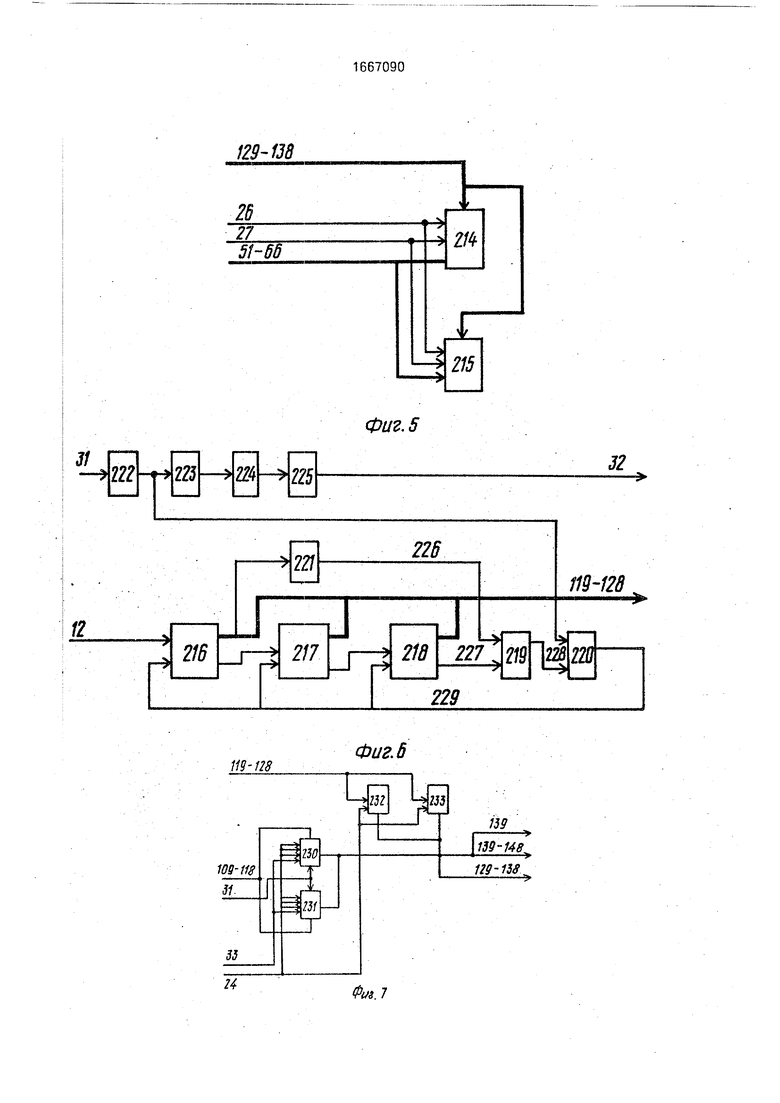

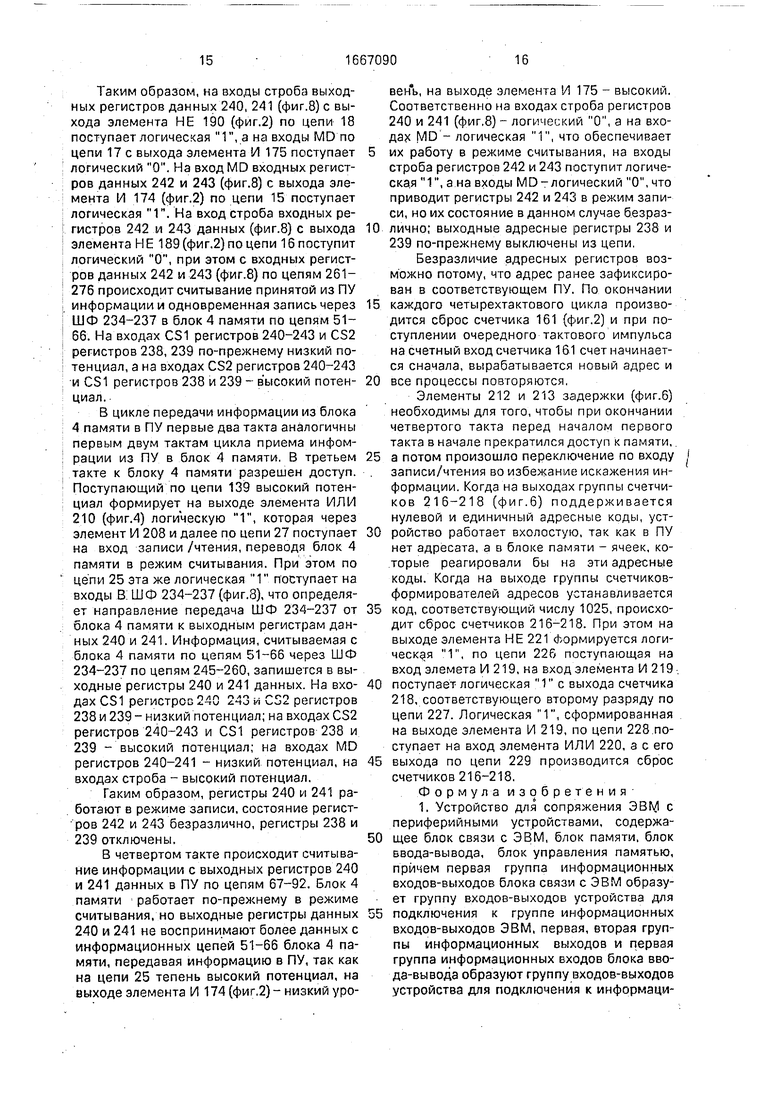

На фиг.1 представлена блок-схема устройства; на фиг.2 - блок синхронизации; на фиг.З - блок связи с ЭВМ; на фиг.4 - блок управления памятью; на фиг.5 - блок памяти; на фиг.6 - блок формирования адреса; на фиг.7 - блок коммутации адреса; на фиг.8 - блок ввода-вывода.

Устройство содержит (фиг.1) блок 1 синхронизации, блок 2 связи с ЭВМ, блок 3 управления памятью, блок 4 памяти, блок 5 формирования адреса, блок 6 коммутации адреса, блок 7 ввода-вывода, цепи 8 и 9 связи с ЭВМ, цепи 10-28 связи между блоками, цепь 29 подачи сигнала начальной установки, цепь 30 подачи сигнала запуска, цепи 31-33 связи между блоками, цепь 34 подачи периферийным устройствам сигнала

признака адресации, 16-разрядные шины 35-50,51-66, 67-92. 93-108 данных, 10-разрядные шины 109-118, 119-128, 129-138, 139-148, 149-158 адреса.

Блок 1 синхронизации (фиг.2) предназначен для формирования сигналов управления, необходимых для синхронизации работы устройства, и содержит генератор 159 тактовых импульсов (ГТИ), делитель 160 частоты, счетчики 161 и 162, триггеры 163 и 164, одновибратор 165, элементы И 166- 175, элементы ИЛИ 176 и 177, элементы 178 и 179 задержки, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 180. элементы НЕ 181-191. Позиции 192-198 обозначают внутренние связи блока.

Блок 2 связи с ЭВМ (фиг.З) предназначен для преобразования слова-состояния выходного процессорного элемента ЭВМ, записанного в регистре состояния, в управляющие сигналы и содержит шинные формирователи 199-200, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 201, элементы, 202 и 203

Ј

О

о

vj О Ч О

задержки, элементы И-НЕ 204 и 205, элементы НЕ 206 и 207.

Блок 3 управления памятью (фиг.4) предназначен для обеспечения приоритета ЭВМ при работе с блоком 4 памяти и содержит элементы И 208 и 209, элементы ИЛИ 210 и 211. элементы 212 и 213 задержки.

Блок 4 памяти (фиг.5) предназначен для оперативного хранения информации, предназначенной для передачи в сеть или посту- пающей из сети, и содержит два оперативных запоминающих узла 214 и 215 с организацией 1024x8.

Блок 5 формирования адреса (фиг.6) предназначен для выработки адресных кодов и содержит счетчики 216-218. элемент И 219, элемент ИЛИ 220, элементы НЕ 221 и 222, элементы 223-225 задержки, позиции 226-229 обозначают внутренние связи.

Блок 6 коммутации адреса (фиг.7) предназначен для перекоммутации адресных входов блока 4 памяти на адресные шины ЭВМ или блока 5 формирования адреса (в зависимости от наличия сигнала обращения ЭВМ к устройству), содержит регистры 230 и 231 и шинные формирователи 232 и 233.

Блок 7 ввода-вывода (фиг.8) предназначен для кратковременного хранения информации и ее одновременной выдачи или приема, для разнесения входных и выходных информационных шин, для передачи адресного кода периферийным устройствам в момент адресации, для отключения адресных линий при передаче или приеме информации и содержит шинные формирователи 234-237 данных, выходные адресные регистры 238 и 239, выходные регистры 240 и 241 данных, входные регистры 242 и 243 данных, элемент НЕ 244.

Устройство работает следующим образом.

Выделяются два режима работы устройства: режим обмена информацией между ЭВМ и блоком памяти и режим обмена информацией между блоком памяти и периферийными устройствами (ПУ), Перед началом работы устройства из ЭВМ в соответствующие ячейки памяти должна быть произведена загрузка информации, преднаначенной в дальнейшем для передачи в ПУ. Кроме того, в устройстве обеспечен приоритет ЭВМ для обмена информацией с устройством. Работа в режиме обмена информацией между блоком памяти и ПУ делится на два цикла. Первый цикл - прием информации из ПУ в блок памяти; второй цикл - передача информации из блока памяти в ПУ.

Каждому адресату в ПУ соответствует два адресных кода: четный и нечетный, соответственно в блоке памяти устройства

каждому адресату отведены две ячейки с адресными кодами, отличающиеся по младшему разряду. Одна из них (соответствующая четному адресному коду) предназначена для хранения информации, принятой из ПУ. Другая ячейка (соответствующая нечетному адресному коду) предназначена для хранения информации, которую необходимо передать в ПУ. Таким образом, млад0 ший разряд адресного кода не участвует в выборке адресата, а только определяет направление передачи информации. Если в младшем разряде адресного кода логический О, то информация поступает из ПУ;

5 если в младшем разряде адресного кода логическая 1, то информация передается в ПУ; в зависимости от логического уровня на этой линии в ПУ откроется соответствующий канал для передачи или приема дан0 ных.

Цикл приема информации из ПУ в блок памяти состоит из четырех тактов: первый - выработка адресного кода и сигнала о признаке адресации, запись адреса и сигнала о

5 признаке адресации в выходные адресные регистры; второй - передача адресного кода в ПУ вместе с сигналом о признаке адресации; третий - запись информации из ПУ во входные регистры данных: четвертый - за0 пись информации с входных регистров данных в блок памяти.

Цикл передачи информации из блока памяти в ПУ также состоит из четырех тактов: первый и второй такты аналогичны пер5 вому и второму тактам предыдущего цикла: третий такт - запись информации из блока памяти в выходные регистры данных: четвертый такт - передача информации с выходных регистров данных в ПУ.

0Поскольку в начале работы устройства

блок 5 формирования адреса сразу формирует адресный код. равный единице (т.е. нулевой адресный код исключается), а каждому адресату должны соответствовать

5 два адресных кода, различающихся только по младшему разряду, при программировании ЭВМ следует учитывать, что нулевая и первая ячейка блока памяти не должны быть задействованы и соответственно в ПУ не

0 должно быть адресатов, реагирующих на нулевой и единичный адресные коды.

Чтобы поочередно для каждого адресата выполнялись указанные циклы, в устройстве формируются и поступают на

5 управляющие входы элементов устройства сигналы в соответствии с таблицей.

Формирование управляющих сигналов организовано на основе работы двоичного четырехразрядного счетчика 161 (фиг.2). Схема включения тактового счетчика 161

разрешает счет тактовых импульсов, поступающих от тактового генератора 159 через делитель 160 частоты и элемент И 168. По приходу каждого из импульсов на вход тактового счетчика 161 на его выходах формируется определенный код. Путем преобразования этого кода посредством блока 1 синхронизации и блока 3 управления памятью формируются управляющие сигналы, обеспечивающие выполнение всех четырех тактов в циклах.

Длительность одного такта определяется частотой следования тактовых импульсов, которая выбрана в данном случае 100 кГц (длительность такта 10 мкс). Источником тактовых импульсов является ГТИ. Его кварцевый резонатор способен выдавать частоты 10-20 МГц. В состав ГТИ входит делитель частоты на девять. Установка на выходе ГТИ делителя частоты на 12 позволяет получать частоты в диапазоне 80-160 кГц.

Перед началом работы при подаче питания скачок потенциала по цепи 29 (фиг 2) через элемент 179 задержки поступает на вход одновибратора 165. В результате этого происходит формирование импульса, поступающего на вход сброса триггера 164 На его выходе устанавливается низкий потенциал, поступающий на один из входов элемента И 168. что запрещает прохождению тактовых импульсов на счетный вход тактового счетчика 161:таким образом устройство находится в состоянии ожидания

По приходу стартового сигнала по цепи 30 на установочный вход триггера 163 на его выходе установится логическая 1, поступающая на вход элемента И 166, но работа устройства начнется, если в соответствующие ячейки блока 4 памяти произведена запись информации, предназначенной в дальнейшей для передачи в ПУ. Для осуществления этого предусмотрена схема запуска, состоящая из триггеров 163 и 164. одновибратора 165. элементов И 166 и 167, элементов НЕ 181. 191. 222. элемента 179 задержки (фиг.2) и элементов 223-225 задержки (фиг.6).

Загрузка информации в блок 4 памяти производится в режиме обмена информацией между ЭВМ и блоком памяти. Сигнал обращения ЭВМ к устройству и всесигналы, необходимые для работы устройства в режиме обмена информацией между ЭВМ и блоком памяти, формируются в блоке 2 связи с ЭВМ (фиг.З) путем использования управляющих сигналов WR и RD центрального процессора К1810ВМ86. работающего в минимальном режиме. Выход RD процессорного элемента по цепи 8 и выход WR по цепи 9 соединены с входом элемента 201.

Сигнал обращения ЭВМ к устройству формируется на выходе элемента 201 (фиг.З) при поступлении по цепи 8 или 9 Низкого потенциала. Сформированный на выходе

элемента 201 сигнал обращения ЭВМ к устройству по цепи 10 поступает в блок 1 синхронизации (фиг.2) на вход элемента И 166, при этом на выходе элемента И 166 формируется высокий потенциал, поступающий на

0 вход элемента НЕ 191; сформированный на выходе элемента НЕ 191 логический О по цепи 31 поступает в блок 5 формирования адреса (фиг.6) на вход элемента НЕ 222, Сформированный на его выходе высокий

5 потенциал поступает на вход элемента ИЛИ 220. Сформированный на выходе элемента ИЛИ 220 высокий уровень поступает на входы сброса счетчиков 216-218. в результате чего счетчики 216-218 устанавливаются в

0 нулевое состояние. Кроме того, низкий уровень по цепи 31 с выхода элемента НЕ 191 поступает в блок 6 коммутации адреса (фиг.7) для сброса регистров 230 и 231, а также в блок 7 ввода-вывода (фиг.8) на входы

5 сброса выходных адресных регистров 238 и 239. выходных и входных регистров 240-243 данных.

С выхода элемента И 166 в начале работы устройства высокий потенциал через эле0 мент ИЛИ 177 (фиг.2) сбрасывает счетчик 162 Вместе с этим с выхода элемента НЕ 222 высокий уровень поступает на вход элементов 223-225 задержки. С выхода элемента 225 по цепи 32 высокий уровень

5 поступает в блок 1 синхронизации (фиг.2) на установочный вход триггера 164, на его выходе формируется логическая 1. которая, поступив на вход элемента И 168, разрешает поступление импульсов от ГТИ на счет0 ный вход тактового счетчика 161.

Элементы 223-225 задержки необходимы для задания длительности сбрасывающего импульса. достаточного для того, чтобы произошел сброс указанных элемен5 тов до поступления первого тактового импульса на счетный вход счетчика 161.

Высокие уровни с выхода элемента НЕ 222 по цепи 32 и с выхода триггера 164 попадают на входы элемента И 167, Старто0 вый сигнал (сигнал Пуск) поступает в блок 1 синхронизации по цепи 30 (фиг.1). Когда по окончании сигнала Пуск на цепи 30 установится низкий потенциал, с выхода элемента НЕ 181 на вход элемента И 167

5 также поступит логическая 1. На выходе элемента И 167 сформируется высокий потенциал, который сбросит триггер 163. На цепи 31 установится высокий потенциал, а на цепи 32 установится низкий потенциал, но поскольку логическая 1 на выходе тригrepa 164 появится только после того, как на его входе сброса установится низкий потенциал, то поступивший на установочный вход триггера 164 по цепи 32 низкий потенциал не изменит его состояния, и логическая 1 на входе элемента И 168 будет поддерживаться до тех пор, пока на схему будет подано питание. Таким образом, устройство будет находиться в состоянии ожидания, пока не будет выработан сигнал обращения ЭВМ к устройству. Указанный этап запуска будет иметь место только в начале работы устройства.

После этапа запуска реализуется обмен информацией между ЭВМ и блоком памяти. Сформированный на выходе элемента 201 (фиг.З) сигнал обращения ЭВМ к устройству по цепи 10 поступает также на вход элемента НЕ 182 (фиг.2), при этом с выхода элемента НЕ 182 на один из входов элемента ИЛИ 176 поступит логический О, но на выходе элемента ИЛИ 176 логический О появится только в том случае, если на остальных трех рходах элемента ИЛИ 176 также будут низкие потенциалы. Это возможно только тогда, когда тактовый счетчик 161 будет в сброшенном состоянии, т.е. очередной цикл передачи или приема информации завершен (или еще не начат). В этом случае на выходе элемента ИЛИ 176 формируется логический О, поступающий на вход элемента И 168, запрещающего дальнейшее прохождение тактовых импульсов на счетный вход тактового счетчика 161; вместе с этим низкий потенциал после инвертирования в элементе НЕ 183 поступает на вход элемента И 171.

Если на втором входе элемента И 171 также появится высокий потенциал, то на его выходе сформируется логическая 1, т.е. сигнал о прерывании работы устройства. Этот сигнал по цепи 14 (фиг.4) поступает в блок 3 управления памятью на входы элементов ИЛИ 210 и 211 и на их выходах сформируются высокие уровни, которые, поступая на входы элементов И 208 и 209 (фиг.4), обеспечат прохождение через элементы И 208 и 209 управляющих сигналов, сформированных в блоке 2 связи с ЭВМ и поступающих по цепи 22 и 23. Одновременно по-цепи 11 этот же высокий потенциал через элемент 202 задержки поступает на входы элементов И-НЕ 204 и 205, что разрешает формирование управляющих сигналов, обеспечивающих режим обмена информацией между ЭВМ и блоком 4 памяти.

Элемент 202 задержки необходим для того, чтобы формирование этих сигналов началось позже, чем будет прервана работа

устройства в режиме обмена информацией между блоком памяти и ПУ. Вместе с этим логическая 1 с цепи 11 поступит на вход готовности в ЭВМ, сообщая о том, что работа устройства прервана.

Если на цепи 8 (фиг.2) будет низкий потенциал, а на цепи 9 - высокий (что соответствует режиму считывания информации из блока 4 памяти в ЭВМ), то логическая Г с

0 выхода элемента 201 (фиг.З) попадает на вход элемента И-НЕ 205, а на вход элемента И-НЕ 204 попадает логический О с цепи 8, Таким образом, на выходе элемента И-НЕ 204 сформируется логическая 1, а на выхо5 де элемента И-НЕ 205 сформируется логический О (поскольку на других входах этих элементов поддерживается высокий потенциал, сформированный на выходе элемента 202 задержки).

0 По цепи 23 с выхода элемента И-НЕ 204 логическая 1 поступит на вход элемента И 208 (фиг.4), а поскольку на другом входе этого элемента поддерживается высокий потенциал (как было показано выше), на вы5 ходе элемента И 208 сформируется логическая 1 и по цепи 27 поступит на входы записи-чтения блока 4 памяти (фиг.5).

Одновременно логический О с выхода элемента И-НЕ 205 поступит на вход эле0 мента 203 задержки. С выхода элемента 203 задержки по цепи 22 логический О посту- лает на вход элемента И 209 (фиг.4) (при этом на другом входе элемента И 209 поддерживается логическая 1), поэтому на вы5 ходе элемента И 209 сформируется логический О, который поступит на синх- ровходы блока 4 памяти (фиг.5), что разрешит его работу в режиме считывания, поскольку на входах записи/чтения - логи0 ческая 1.

Элемент 203 задержки необходим для того, чтобы сигнал, поступающий на синх- ровходы блока 4 памяти и разрешающий доступ к ней, пришел несколько позже, чем

5 сигнал на входы записи/чтения, определяющий режим работы блока памяти.

Одновременно с этим логический О с выхода элемента И-НЕ 205 поступит на входы CS1 регистров 230 и 231 (фиг.7) по цепи

0 33, а также на вход элемента НЕ 207 (фиг.З), с выхода которого по цепи 24 на входы EW, MD, CS2 регистров 230 и 231 поступит логическая 1. Сформированные таким образом сигналы разрешают передачу адресных ко5 дов от ЭВМ по цепям 109-118 на адресные входы 129-138 блока 4 памяти. При этом шинные формирователи 232-233 (фиг.7) переключатся в состояние высокого импеданса (по цепи 24 на входы ОЕ шинных формирователей (ШФ) 232 и 233 поступит

логическая 1, что обеспечит электрическую развязку между выходными линиями регистров 230 и 231 и ШФ 232 и 233). Кроме того, логический О с выхода элемента И- НЕ 205 (фиг.3) попадет на управляющие входы ОЕ ШФ 199 и 200 (фиг.З), что разрешит их работу, а логическая 1 с выхода элемента НЕ 207 по цепи 24 поступит на управляющие входы С5 ШФ 234-237 (фиг.8), что разрешит их работу. Одновременно с этим логическая 1 с выхода элемента И-НЕ 204 поступит на вход элемента НЕ 206 (фиг.З). Сформированный на выходе элемента НЕ 206 логический О поступает на входы Т ШФ 199 и 200, что обеспечит их работу в режиме передачи данных от блока памяти в ЭВМ.

В случае, если на цепи 8 будет логическая 1, а на цепи 9 - логический О (что соответствует режиму записи в блок 4 памяти информации, поступающей от ЭВМ), все процессы проходят аналогично, за исключением того, что на выходе элемента И-НЕ 204 сформируется логический О и по цепи 23 через элемент И 208 (фиг.4) по цепи 27 попадет на управляющие входы записи/чтения блока 4 памяти, что переведет его в режим записи: этот же уровень с выхода элемента И-НЕ 204 на вход элемента НЕ 206 и высокий уровень с выхода элемента НЕ 206 попадет на управляющие входы Т группы шинных формирователей 199 и 200, что обеспечит направление передачи данных от ЭВМ к блоку 4 памяти с цепей 35-50 на цепи 51-66.

В случае, если в момент формирования сигнала о прерывании работы устройства. т.е. когда три младших разряда счетчика 161 находятся в состоянии 000 и на первый вход элемента ИЛИ 176 (фиг.2) также поступил логический О, на счетный вход счетчика 161 через элемент И 168 прошел очередной тактовый импульс, тактовый счетчик 161 примет состояние на выходах 001 и на выходе элемента ИЛИ 176 также ловится логическая 1, что означает начало нового цикла. При этом сформированный на выходе элемента ИЛИ 176 логический О, поступив на вход элемента НЕ 183, разрешит работу блока 2 связи устройства с ЭВМ, который выдает управляющие сигналы одновременно с управляющими сигналами блока синхронизации. Чтобы исключить такой случай, сформированный сигнал о прерывании работы устройства проходит через схему испытания на длительность, реализованную на основе счетчика 162 и входящую в состав блока 1 синхронизации (фиг.2).

Схема работает следующим образом.

Счетчик 162 при отсутствии сигнала обращения ЭВМ к устройству будет обнулен, так как в этом случае на выходе элемента ИЛИ 176 будет логическая Г, которая по- 5 ступит на вход сброса счетчика 162. При этом на выходах счетчика 162 поддерживается низкий потенциал, выход, соответствующий разряду 2 соединен с входом элемента НЕ 187, т.е. на выходе элемента

0 НЕ 187 формируется логическая 1. поступающая на один из входов элемента И 169. На другой вход элемента И 169 поступают тактовые импульсы с выхода делителя 160 частоты. На третьем входе элемента И 169 в

5 данный момент будет поддерживаться низкий потенциал, поступающий с выхода элемента НЕ 183, поэтому тактовые импульсы не будут проходить на счетный вход счетчика 162. Как только на выходе элемента ИЛИ

0 176 сформируется логический О, на входе сброса счетчика 162 также появится логический О.

Кроме того, сформированная на выходе элемента НЕ 183 логическая 1 по цепи 198

5 разрешает прохождение через элемент И 169 тактовых импульсов, которые с выхода элемента И 169 поступят на счетный вход счетчика 162.

Если за время формирования сигнала о

0 прерывании через элемент И 168 не успел пройти очередной тактовый импульс на счетный вход тактового счетчика 161, то на выходе элемента ИЛИ 176 будет поддерживаться низкий потенциал. Этот низкий по5 тенциал запретит прохождение тактовых импульсов через элемент И 168. Логическая 1, сформированная на выходе элемента НЕ 183, разрешит прохождение тактовых импульсов через элемент И 169 на счетный

0 вход счетчика 162. Когда на счетный вход счетчика 162 попадает втооой импульс, на его выходе, соответствющем разряду 21. появится логическая 1, которая попадает на вход элемента И 171 и разрешит прохож5 дение сигнала о прерывании с другого входа элемента И 171 на его выход, т.е. на цепи 11 и 14. Если сигнал о прерывании имеет длительность одного такта (от фронта первого импульса, пришедшего на счетный вход

0 счетчика 162, до фронта второго импульса), то случай прохождения тактового импульса через элемент И 168 в момент формирования сигнала о прерывании исключается (поскольку время переключения элементов

5 176.168 порядка 25НС. а время одного такта Юмкс).

В случае, если во время формирования сигнала о прерывании на счетный вход счетчика 161 попадает очередной тактовый импульс, логический О на выходе элемента

ИЛИ 176 через 50НС сменится на логическую 1, что разрешит поступление тактовых импульсов на счетный вход тактового счетчика 161 и одновременно обнулит счетчик 162, на разряде 2 которого не успевает появится логическая 1, таким образом на вход элемента И 171 высокий потенциал не проходит, что запретит прохождение на цепи 11 и 14 ложного сигнала о прерывании. Устройство в этом случае будет прервано только на следующем цикле.

В случае прекращения сигнала обращения ЭВМ к устройству на выходе элемента ИЛИ 176 устанавливается высокий потенциал, который сбрасывает счетчик 162 и разре- шает поступление тактовых импульсов на счетный вход тактового счетчика 161. т.е. устройство переходит из режима обмена информацией между ЭВМ и блоком 4 памяти в режим обмена информацией между блоком 4 памяти и ПУ.

При поступлении импульса на счетный вход счетчика 161 (фиг.2) на его выходах появится код 0001, соответственно на цепи 192 установится высокий потенциал, а на цепи 193 - низкий, при этом на выходе элемента НЕ 185 сформируется логическая 1 и поступит на один из входов элемента И 172, на другой вход элемента И 172 по цепи 192 также поступит логическая 1. На выхо- де элемента И 172 сформируется высокий потенциал и по цепи 12 поступит на счетный вход счетчика 216 (фиг.6).

При этом на выходах группы счетчиков 216-218 (на цепях 119-128) появится адрес- ный код. На счетный вход счетчика 216 импульс будет поступать только при наличии на цепи 192 логической 1 и на цепи 193 логического О, что соответствует случаю, когда на выходах тактового счетчика 161 код 0001, в любом другом случае на счетном входе счетчика 216 будет низкий потенциал, и сформированный адресный код будет удерживаться на выходах группы счетчиков 216-218 на протяжении всего четырехтакто- вого цикла.

Адресный код поступает по цепям 119- 128 на вход ШФ 232-233 (фиг.7. ШФ постоянно работают в одном направлении передачи). С выхода ШФ 232-233 по цепям 139-149 адресный код записывается в выходные адресные регистры 238-239. Входы MD этих регистров обеспечивают режим записи, находясь под низким потенциалом, который сформирован посредством следую- щих элементов: элемент НЕ 186, элемент И 173; при поступлении на их входы с цепей 192 и 193 логической 1 и логического О соответственно на обоих входах элемента И 173 окажется низкий потенциал, поэтому на

выхЪде элемента И 173 сформируется логический О и по цепи 19 поступит на входы MD выходных адресных регистров 238 и 239 (фиг.8), на входы строба EW выходных адресных регистров 238 и 239 по цепи 20 поступает логическая 1, сформированная на выходе элемента НЕ 184 (фиг.2), на входы CS1 регистров 238 и 239 поступает логический О, на входы CS2 - логическая 1, что обеспечивает работу выходных адресных регистров 238 и 239 (фиг.7) в режиме записи.

Одновременно с этим поступающая по цепи 12 на счетный вход счетчика 216 (фиг.6) логическая 1, разрешающая формирование адресного кода, поступает также через элемент 178 задержки (фиг.2) по цепи 21 в регистр 239 и фиксируется в нем. Таким образом, формируется сигнал о признаке адресации. Высокий потенциал признака адресации, поступив в дальнейшем в ПУ по отдельной цепи 34 (фиг.1) совместно с адресным кодом, несет информацию о приходе адреса. Поскольку направление передачи определяется младшим разрядом адресного кода после прохождения адреса через ШФ 232 и 233, младший разряд адреса по цепи 139 (фиг.7) подается в блок 3 управления памятью.

На этом заканчивается первый такт. Наряду с указанными процессами в течение первого такта с цепей 192 и 193 логическая 1 и логический О соответственно поступают на входы элемента 180, формируя на его выходе логическую 1, которая поступает по цепи 13 на один из входов элемента ИЛИ 211 (фиг.4), на другом входе которого при отсутствии сигнала с прерывании на будет низкий потенциал. С выхода элемента ИЛИ 211 логическая 1 поступает на один из входов элемента И 209, второй вход которого, при условии отсутствия сигнала о прерывании, находится под высоким потенциалом, т.е. на выходе элемента И 209 формируется логическая 1, которая поступает по цепи 26 на синхровходы блока 4 памяти и разрешает его работу.

Кроме того, с выхода элемента ИЛИ 211 по 28 логическая поступает на входы CS регистров 240-243 (фиг.8) и на входы CS2 регистров238 и 239. После элемента НЕ 244 этот потенциал преобразуется в логический О и поступает на входы CS2 регистров 240-243 и на входы CS1 регистров 238 и 239. тем самым разрешая работу выходных адресных регистров 238 и 239 и запрещая работу выходных и входных регистров 240-243 данных.

Во втором такте после поступления следующего тактового импульса на счетный вход счетчика 161 на его выходах меняется

код и на цепи 192 теперь устанавливается логический О, а на цепи 193 - логическая 1. При этом на выходе элемента И 172 (фиг.2) формируется логический О, а на выходе элемента И 173 логическая 1, которая по цепи 19 поступает на вход MD выходных адресных регистров 238 и 239, что переведет их в режим считывания. Адресный код по цепям 149-158 вместе с сигналом о признаке адресации (по цепи 34) поступит в ПУ, Все остальные элементы устройства останутся в прежнем состоянии, поскольку потенциал на выходе элемента 180 останется неизменным. Элемент задержки ИЛИ 178 необходим для того, чтобы при переключении выходных адресных регистров 238 и 239 из режима записи в режим считывания высокий потенциал по цепи 21 заведомо не изменил состояние выходного адресного регистра 239.

На протяжении третьего такта на цепях 192 и 193 (фиг.2) поддерживается высокий потенциал, на выходе элемента И 172 по- прежнему низкий потенциал. На выходе элемента И 173 также устанавливается низкий потенциал, что переводит выходные адресные регистры 238 и 239 в режим записи, отключая их выходы от ПУ. На выходе элемента 180 появится логический О. При условии отсутствия сигнала о прерывании цепи 14 будет логический О, а на цепях 22, 23 - логическая 1. Таким образом,логический О, сформированный на выходе элемента 180. без изменения попадает через элемент ЛЛИ 211 и элемент И 209 (фиг.4) на выходы CS блока 4 памяти (фиг.5), что разрешит доступ к памяти (на вход элемента ИЛИ 211 (фиг.4, в данном случае с цепи 14 поступает логический О, а на вход элемента И 209 с цепи 22 поступает логическая 1). Одновременно логический О с выхода элемента ИЛИ 211 по цепи 28 поступит на входы CS1 регистров 240-243 (фиг.8) и на входы CS2 регистров 238 и 239, при этом на входах CS2 регистров 240-243 и на входах CS1 регистров 238 и 239 сформируется логическая Г, что разрешит работу регистров 240- 243, а регистры 238 и 239 будут отключены. Вместе с тем на цепи 139 (фиг.7) будет без изменений поддерживаться потенциал с выхода шинных формирователей 232 и 233. соответствующего младшему разряду адресного кода, так как адресный код не меняется.

Через элементы 212 и 213 задержки (фиг.4) этот сигнал попадает на вход элемента ИЛИ 210, а с его выхода без изменений - на вход элемента И 208 и далее с выхода элемента И 208 также без изменений по цепи 27 на входы записи/чтения блока 4

памяти (фиг.5), так как при отсутствии сигнала о прерывании на вход элемента ИЛИ 210 с цепи 14 поступит логический 0м, а на элемент И 208 с цепи 23 поступает логиче- 5 екая 1.

Этот же сигнал младшего разряда адреса, снятый с выхода элемента ИЛИ 210, по цепи 25 поступает на входы В шинных формирователей (ШФ) 234-237 (фиг.8), что от0 кроет соответствующий канал ШФ 234-237, так как на цепи 139 в данном случае потенциал низкий, при этом блок 4 памяти будет готов к записи, а ШФ 234-237 (фиг.8) будут открыты для передачи информации из вход5 ных регистров данных 242 и 243 в блок 4 памяти. Регистры 240-243 будут находиться в режиме записи, поскольку на линиях 192 и 193 (фиг.2) поддерживаются высокие потенциалы, а на выходе элементов НЕ 185 и

0 186 сформируются низкие потенциалы, которые поступят на входы элементов И 174 и 175. на выходах которых также сформируются логические О. По цепи 15 логический О поступит на входы MD регистров 242 и 243

5 (фиг.8), а по цепи 17 - на входы MD регистров 240 и 241. Через элементы НЕ 189 и 190 (фиг.2) по цепям 16 и 18 эти сигналы в виде логических 1 поступят на входы строба регистров 240-243 (фиг.8), что соответствует

0 их работе в режиме записи, В регистры 242, 243 будет произведена запись информации, поступившей в этом такте из ПУ. Состояние регистров 240 и 241 в третьем такте безразлично. В течение четвертого такта на цепях

5 192 и 193 (фиг.2) поддерживается низкий потенциал. При этом на выходах элементов И 172 и 173 по-прежнему низкий потенциал. Доступ к блоку 4 памяти (фиг.5) разрешен по входу С§ (на цепи 26 логический О).

0 На цепи 27 - также логический О, поступающий на входы записи/чтения блока 4 памяти и определяющий работу блока 4 памяти в режиме записи. ШФ 234-237 (фиг.8) работают в направлении передачи

5 информации с входных регистров данных 242 и 243 на информационные входы 51-56 блока 4 памяти. В четвертом также входные регистры данных 242 и 243 работают в режиме считывания информации, состояние

0 выходных регистров данных 240 и 241 безразлично.

С выходов элементов НЕ 185 и 186 (фиг.2) на входы элементов И 174 и 175 по цепям 195 и 196 поступают логические 1.

5 На вход элемента И 175 по цепи 25 поступает логическая 1 и на вход элемента И 174 с выхода элемента НЕ 188 также поступает логическая 1. На выходе элемента И 174 появится логическая 1. на выходе элемента И 175 - логический О.

Таким образом, на входы строба выходных регистров данных 240, 241 (фиг.8) с выхода элемента НЕ 190 (фиг.2) по цепи 18 поступает логическая 1, а на входы MD по цепи 17 с выхода элемента И 175 поступает логический О. На вход MD входных регистров данных 242 и 243 (фиг.8) с выхода элемента И 174 (фиг.2) по цепи 15 поступает логическая Г. На вход строба входных регистров 242 и 243 данных (фиг.8) с выхода элемента НЕ 189(фиг.2)по цепи 16 поступит логический О, при этом с входных регистров данных 242 и 243 (фиг.8) по цепям 261- 276 происходит считывание принятой из ПУ информации и одновременная запись через ШФ 234-237 в блок 4 памяти по цепям 51- 66. На входах CS1 регистров 240-243 и CS2 регистров 238, 239 по-прежнему низкий потенциал, а на входах CS2 регистров 240-243 и CS1 регистров 238 и 239 - высокий потенциал.

В цикле передачи информации из блока 4 памяти в ПУ первые два такта аналогичны первым двум тактам цикла приема инфом- рации из ПУ в блок 4 памяти. В третьем такте к блоку 4 памяти разрешен доступ. Поступающий по цепи 139 высокий потенциал формирует на выходе элемента ИЛИ 210 (фиг.4) логическую 1й, которая через элемент И 208 и далее по цепи 27 поступает на вход записи /чтения, переводя блок 4 памяти в режим считывания. При этом по цепи 25 эта же логическая 1 поступает на входы В ШФ 234-237 (фиг.8), что определяет направление передача ШФ 234-237 от блока 4 памяти к выходным регистрам данных 240 и 241. Информация, считываемая с блока 4 памяти по цепям 51-66 через ШФ 234-237 по цепям 245-260, запишется в выходные регистры 240 и 241 данных. На входах CS1 регистров 240 243 CS2 регистров

238и 239 - низкий потенциал; на входах CS2 регистров 240-243 и CS1 регистров 238 и

239- высокий потенциал; на входах MD регистров 240-241 - низкий потенциал, на входах строба - высокий потенциал.

Таким образом, регистры 240 и 241 работают в режиме записи, состояние регистров 242 и 243 безразлично, регистры 238 и

239отключены.

В четвертом такте происходит считывание информации с выходных регистров 240 и 241 данных в ПУ по цепям 67-92. Блок 4 памяти работает по-прежнему в режиме считывания, но выходные регистры данных

240и 241 не воспринимают более данных с информационных цепей 51-66 блока 4 памяти, передавая информацию в ПУ, так как на цепи 25 тепень высокий потенциал, на выходе элемента И 174(фиг.2)-низкийуровен ь, на выходе элемента И 175 - высокий. Соответственно на входах строба регистров 240 и 241 (фиг.8) - логи ioi кий О, а на входах MD - логическая 1, что обеспечивает

их работу в режиме считывания, на входы строба регистров 242 и 243 поступит логическая 1, а на входы MD- логический О, что приводит регистры 242 и 243 в режим записи, но их состояние в данном случае безраз0 лично; выходные адресные регистры 238 и 239 по-прежнему выключены из цепи

Безразличие адресных регистров возможно потому, что адрес ранее зафиксирован в соответствующем ПУ, По окончании

5 каждого четырехтактового цикла производится сброс счетчика 161 (фиг.2) и при поступлении очередного тактового импульса на счетный вход счетчика 161 счет начинается сначала, вырабатывается новый адрес и

0 все процессы повторяются.

Элементы 212 и 213 задержки (фиг.6) необходимы для того, чтобы при окончании четвертого такта перед началом первого такта в начале прекратился доступ к памяти,

5 а потом произошло переключение по входу j записи/чтения во избежание искажения информации. Когда на выходах группы счетчиков 216-218 (фиг 6) поддерживается нулевой и единичный адресные коды, уст0 ройство работает вхолостую, так как в ПУ нет адресата, а в блоке памяти - ячеек, которые реагировали бы на эти адресные коды. Когда на выходе группы счетчиков- формирователей адресов устанавливается

5 код, соответствующий числу 1025, происходит сброс счетчиков 216-218. При этом на выходе элемента НЕ 221 Формируется логическая 1, по цепи 226 поступающая на вход элемета И 219, на вход элемента И 219

0 поступает логическая 1 с выхода счетчика 218, соответствующего второму разряду по цепи 227, Логическая 1, сформированная на выходе элемента И 219, по цепи 228 поступает на вход элемента ИЛИ 220, а с его

5 выхода по цепи 229 производится сброс счетчиков 216-218.

Формула изобретения 1. Устройство для сопряжения ЭВМ с периферийными устройствами, содержа0 щее блок связи с ЭВМ, блок памяти, блок ввода-вывода, блок управления памятью, причем первая группа информационных входов-выходов блока связи с ЭВМ образует группу входов-выходов устройства для

5 подключения к группе информационных входов-выходов ЭВМ, первая, вторая группы информационных выходов и первая группа информационных входов блока ввода-вывода образуют группу входов-выходов устройства для подключения к информационным и адресным входам-выходам периферийных устройств, отличающееся тем, что, с целью сокращения аппаратурных затрат, в устройство введены блок синхронизации, блок формирования адреса, блок коммутации адреса, причем установочный вход и вход запуска блока синхронизации являются входами устройства для подключения соответственно к установочному входу и выходу запуска ЭВМ, первый синхровыход блока синхронизации соединен с разрешающим входом блока связи с ЭВМ и является выходом устройства для подключения к входу готовности ЭВМ, первый, второй информационные входы блока связи с ЭВМ являются входами устройства для подключения соответственно к выходам записи и чтения ЭВМ, первая группа информационных входов блока коммутации адреса образует группу входов устройства для подключения к группе адресных выходов ЭВМ, информационный выход блока ввода- вывода является выходом устройства для подключения к входам признака адресации пеоиферийных устройств, при этом вторая группа информационных входов-выходов блока связи с ЭВМ соединена с группой информационных входов-выходов блока памяти и с группой информационных входов- выходов блока ввода-вывода, группа стробирующих входов которого соединена с группой синхровыходов блока синхронизации, первый разрешающий вход которого соединен с информационным выходом блока формирования адреса, группа информационных выходов которого соединена с второй группой информационных входов блока коммутации адреса, первая группа информационных выходов которого соединена с второй группой информационных входов блока ввода-вывода, стробирующий вход которого соединен с управляющим входом блока коммутации адреса и с первым информационным выходом блока связи с ЭВМ, второй информационный выход которого соединен со стробирующим входом блока коммутации адреса, вторая группа информационных выходов которого соединена с группой адресных входов блока памяти, стробирующий вход и вход записи- чтения которого соединены соответственно с первым и вторым выходами блока управления памятью, третий выход которого соединен с вторым разрешающим входом блока синхронизации и с первым входом режима работы блока ввода-вывода, второй вход режима работы которого соединен с четвертым выходом блока управления памятью, первый и второй входы логического условия которого соединены соответственно с третьим и четвертым информационными выходами блока связи с ЭВМ, пятый информационный выход которого соединен с третьим разрешающим входом блока синхронизации, второй, третий и четвертый син- хровыходы которого соединены соответственно с третьим, четвертым входами логического условия блока управления памятью и с синхровходом блока формиро0 вания адреса, установочный вход которого соединен с пятым синхровыходом блока синхронизации, с установочным входом блока ввода-вывода и с установочным входом блока коммутации адреса, младший

5 разряд первой группы информационных выходов которого соединен с пятым входом логического условия блока управления памятью.

2. Устройство по п. 1. о т л и ч а ю щ е 0 е с я тем, что блок управления памятью содержит два элемента ИЛИ, два элемента И, два элемента задержки, причем первые входы первого, второго элементов И являются соответственно первым, вторым вхо5 дами логического условия блока, первый вход первого элемента ИЛИ соединен с первым входом второго элемента ИЛИ и является третьим входом логического условия блока, второй вход второго элемента ИЛИ и

0 вход первого элемента задержки являются соответственно четвертым и пятым входами логического условия блока, выходы первого и второго элементов И являются соответственно первым и вторым выходами блока,

5 выход первого элемента ИЛИ соединен с вторым входом второго элемента И и является третьим выходом блока, выход второго элемента ИЛИ соединен с вторым входом первого элемента И и является четвертым

0 выходом блока, при этом выход первого элемента задержки соединен с входом второго элемента задержки, выход которого соединен с вторым входом первого элемента ИЛИ.

5 3. Устройство по п.1, о т л и ч а ю щ е е- с я тем, что блок связи с ЭВМ содержит два шинных формирователя, два элемента НЕ. два элемента И-НЕ, два элемента задержки, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. причем

0 группа информационных выходов первого шинного формирователя и группа информационных входов второго шинного формирователя образуют первую группу информационных входов-выходов блока,

5 группа информационных входов первого шинного формирователя и группа информационных выходов второго шинного формирователя образуют вторую группу информационных входов-выходов блока, первый вход элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ соединен с первым входом первого элемента И-НЕ и является первым информационным входом блока, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вход первого элемента задержки являютсся соответственно вторым информационным и разрешающим входами блока, выход первого элемента НЕ является первь м информационным выходом блока, выход второго элемента И-НЕ соединен с входом второго элемента задержки, с входом первого элемента НЕ, с первыми управляющими входами первого, второго шинных формирователей и является вторым информационным выходом блока, выход второго элемента задержки является третьим информационным выходом блока, выход первого элемента И- НЕ соединен с входом второго элемента НЕ и является четвертым информационным выходом блока, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом второго элемента И-НЕ и является пятым информационным выходом блока, при этом выход первого элемента задержки соединен с вторыми входами первого и второго элементов И-НЕ, выход второго элемента НЕ соединен с вторыми управляющими входами первого и второго шинных формирователей.

4. Устройство поп.1,отличающе - е с я тем, что блок формирования адреса содержит три счетчика, два элемента НЕ, элемент И, элемент ИЛИ, три элемента задержки, причем вход первого элемента НЕ является установочным входом блока, счетный вход первого счетчика является синх- ровходом блока, выход первого элемента задержки является информационным выходом блока, группы разрядных выходов первого, второго и третьего счетчиков образуют группу информационных выходов блока, при этом вход первого элемента задержки соединен с выходом второго элемента задержки, вход которого соединен с выходом третьего элемента задержки, вход которого соединен с выходом первого элемента НЕ и с первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом элемента И и с установочными входами второго, третьего и первого счетчиков, младший разряд группы разрядных выходов которого соединен с входом второго элемента НЕ, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом переноса третьего счетчика, счетный вход которого соединен с выходом переноса второго счетчика, счетный вход которого соединен с выходом переноса первого счетчика.

5, Устройство по п.1. о т л и ч а ю щ е - е с я тем, что блок синхронизации содержит два триггера, два счетчик ), генератор тактовых импульсов, делитель частоты, одновибратор, десять элементов И, два элемента ИЛИ, одиннадцать элементов НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемента задержки, причем установочный вход первого триггера соединен с входом первого эле0 мента НЕ и является входом запуска блока, вход первого элемента задержки является установочным входом блока, установочный вход второго триггера соединен с первым входом первого элемента И и является пер5 вым разрешающим входом блока, вход второго элемента НЕ соединен с первым входом второго элемента И и является вторым разрешающим входом блока, вход третьего элемента НЕ соединен с первым

0 входом третьего элемента И и является третьим разрешающим входом блока, выход четвертого элемента И является первым и вторым синхровыходами блока, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является

5 третьим синхровыходом блока, выход пятого элемента И соединен с входом второго элемента задержки и является четвертым синхровыходом блока, выход четвертого элемента НЕ является пятым синхровыхо0 дом блока, выход второго элемента задержки, выход шестого элемента И, соединенный с входом пятого элемента НЕ, выход пятого элемента НЕ, выход шестого элемента НЕ, выход седьмого элемента И, соединенный с

5 входом шестого элемента НЕ, выход седьмого элемента НЕ, выход второго элемента И, соединенный с входом седьмого элемента НЕ, образуют группу синхро- выходов, блока, при этом выход генератора

0 тактовых импульсов соединен с входом делителя частоты, выход которого соединен с первыми входами восьмого и девятого элементов И, выходы которых соединены соответственно со счетными входами первого и

5 второго счетчиков, выход первого элемента И соединен с входом сброса первого триггера, выход которого соединен с вторым входом третьего элемента И, выход которого соединен с входом четвертого элемента НЕ

0 и с первым входом первого элемента ИЛИ, выход которого соединен с установочным входом второго счетчика, выход которого соединен с первым входом четвертого элемента И и с входом восьмого элемента НЕ,

5 выход которого соединен с вторым входом девятого элемента И, третий вход которого соединен с вторым входом четвертого элемента И и с выходом девятого элемента НЕ, вход которого соединен с выходом второго элемента ИЛИ, с вторым входом первого

элемента ИЛИ и с вторым входом восьмого элемента И, третий вход которого соединен с вторым входом первого элемента И и с выходом второго триггера, вход сброса которого соединен с выходом одновибратора, вход запуска которого соединен с выходом первого элемента задержки, выход первого элемента НЕ соединен с третьим входом первого элемента И. выход третьего элемента НЕ соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с первым входом пятого элемента И, с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с первым выходом первого счетчика и с входом десятого элемента НЕ. выход которого соединен с вторым входом второго элемента И, с первыми входами шестого,

0

5

седьмого элементов И и с первым входом десятого элемента И, выход которого соединен с установочным входом первого счетчика, второй выход которого соединен с вторым входом шестого элемента И, с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с входом одиннадцатого элемента НЕ и с третьим входом второго элемента ИЛИ, четвертый вход которого соединен с третьим выходом первого счетчика и с вторым входом десятого элемента И, третий вход которого соединен с выходом одиннадцатого элемента НЕ, с вторым входом пятого элемента И, с третьим входом второго элемента И и с вторым входом седьмого элемента И, третий вход которого соединен с выходом второго элемента НЕ.

15-21

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для отладки программ | 1986 |

|

SU1383372A1 |

| Устройство для сопряжения ЭВМ с М внешними устройствами | 1986 |

|

SU1374232A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1987 |

|

SU1425692A2 |

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1989 |

|

SU1647581A2 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Логическое устройство для обработки информации | 1984 |

|

SU1339578A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1541616A1 |

| Устройство для контроля выполнения программ (его варианты) | 1985 |

|

SU1315981A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для передачи информации в автоматизированных системах управления медленно текущими процессами. Целью изобретения является сокращение аппаратурных затрат. Устройство содержит блок синхронизации, блок связи с ЭВМ, блок управления памятью, блок памяти, блок формирования адреса, блок коммутации адреса, блок коммутации адреса, блоку ввода-вывода. 4 з.п. ф-лы, 8 ил., 1 табл.

50

Фиг.1

23

Физ.4

u129-m

Л

III

т

225

12

Ur-J

т-из

230

WB-fff 31

1L и

Фиг. 5

32

226

119-128

г

218

227

229

Фиг. В

H9-f4ff

Пд-1Ъ8

Фиг. 7

| Авторское свидетельство СССР Nb 1300485, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Подвес для инструментальной головки ультразвукового станка | 1960 |

|

SU134115A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1991-07-30—Публикация

1989-08-07—Подача