фиг.1

00

ю

SO

о

со N

ю

Изобретение относится к цифровой технике и может использоваться при диагностировании цифровых блоков, содержащих структуру с произвольной логикой и цепи обратных связей.

Цель изобретения - увеличение информативности контроля.

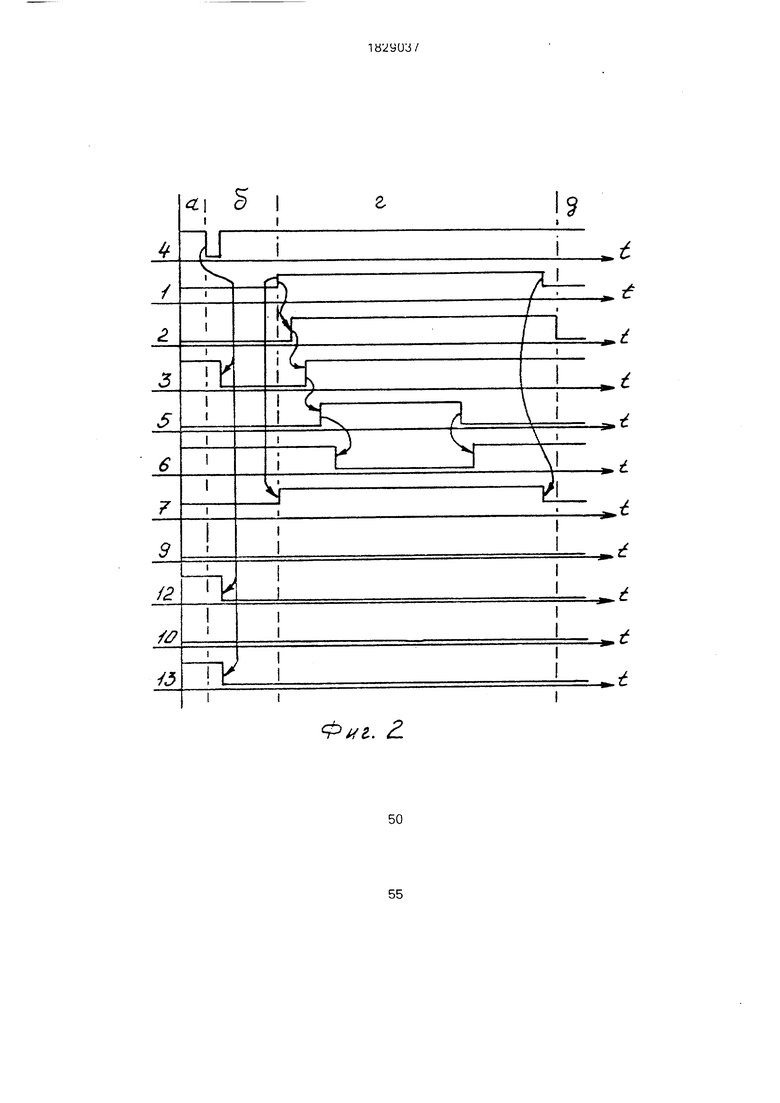

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2-4 - временные диаграммы работы устройства.

Устройство содержит информационный вход 1, пороговый элемент 2, D-триггер З, вход 4 сброса, одновибратор 5, элемент 6 И-НЕ, элемент 7 коммутации, резистор 8, сумматор по модулю два, элемент 10ИЛИ- НЕ, элемент 11 НЕ, RS-триггер 12, D-триггер 13, элементы индикации 14, элементы И 15, 16, элементы индикации 17, 18, вход 19 синхронизации, элемент 20 И, счетчик 21, блок 22 индикации.

На временных диаграммах приняты следующие обозначения:

4- уровень сигнала на входе 4 сброса;

1- уровень сигнала на информационном входе 1 устройства;

2- уровень сигнала на выходе порогового элемента 2;

3- уровень сигнала на инверсном выходе D-триггера З;

5- уровень сигнала на выходе одновиб- ратора 5;

6- уровень сигнала на выходе элемента

6И-НЕ;

7- уровень сигнала на выходе элемента

7коммутации;

9- уровень сигнала на прямом выходе RS-триггера 12;

10- уровень сигнала на выходе элемента ЮИЛИ-НЕ;

13 - уровень сигнала на инверсном выходе D-триггера 13.

Ссылки на временные диаграммы содержат две цифры через точку и букву. Первая цифра обозначает номер фигуры, где содержится описываемый процесс; вторая цифра обозначает вход или выход соответствующего элемента структуры устройства; буква обозначает режим, в котором находится устройство:

а - состояния элементов после включения устройства, причем выходы триггеров 3, 12 и 13 могут находиться в произвольном состоянии;

б - состояние элементов после подачи на вход 4 сброса короткого нулевого импульса;

в - состояния элементов после появления на информационном входе 1 устройства логического нуля;

г - состояния элементов после появления на информационном входе 1 устройства логической единицы;

д - состояния элементов после окончания проверки контролируемой цепи, причем уровень сигнала на информационном входе 1 может быть произвольным.

Функционирование устройства основано на инжектировании нулевого импульса в

контролируемый печатный проводник цифрового блока в момент первого появления высокого логического уровня в контролируемой цепи и анализе реакции исследуемой цепи на данное воздействие.

Полные входные и выходные сопротивления логических схем достаточно велики, чтобы инжектор мог мгновенно изменить состояние контролируемой цепи, а выходное сопротивление блока питания мало и

пульсатор не в состоянии изменить потенциал на шине питания.

Следовательно, наличие короткого нулевого импульса в момент инжектирования нуля в контролируемую цепь, в которой при

сутствует высокий логический уровень, свидетельствует об отсутствии короткого замыкания контролируемого печатного проводника с шиной питания.

Справедливо и обратное утверждение,

0 что отсутствие короткого нулевого импульса в момент инжектирования нуля в контролируемую цепь, в которой присутствует высокий логический уровень, свидетельствует о наличии короткого замыкания контролируе5 мого печатного проводника с шиной питания.

Функционирование устройства основано на подсчете количества тактов подачи входных воздействий до обнаружения высо0 кого логического уровня в исследуемой цепи контролируемого цифрового блока.

Тогда цепи, отнесенные к состоянию в коротких замыканиях, можно будет идентифицировать к задействованным в отдель5 ном коротком замыкании (состоящим в отдельном тракте) по количеству тактов входных воздействий, предшествующих появлению высокого логического уровня в контролируемой цепи цифрового блока,

0

Устройство работает следующим образом.

В начальном состоянии информационный вход 1 устройства не подключен к кон- 5 тролируемой цепи цифрового блока.

На вход 4 сброса устройства подается сигнал в виде короткого нулевого импульса (фиг. 2.4.а, 3.4.а, 4.4.а), который устанавливает инверсные выходы D-триггера З и 13 (фиг. 2.3.6. 2.13.6, 3.13.6, 4.3.6, 4.13.6) и прямой выход RS-триггера 12 (фиг. 2.12.6, 3.12.6, 4.12.6) в ноль.

На информационном входе 1 устройства присутствует состояние 1,5 В (фиг. 2.6, 4.6, 3.6).

Уровень логического нуля (лог. О) с инверсного выхода триггера 3 поступает на первый вход элемента 15 И, а также на первый вход элемента 16 И и на выход одновиб- ратора 5 (фиг. 2.5.6, 3.5.6, 4.5.6). Ноль с выхода одновибратора 5 поступает на второй вход элемента 6 И-НЕ.

Уровень логической единицы (лог. 1) с прямого выхода D-триггера 13 поступает на вход элемента 15 И, на выходе которого установится ноль, поступающий на элемент 17 индикации. Ноль с инверсного выхода D-триггера 13 поступает на вход элемента 16 И.

Ноль с прямого выхода RS-триггера 12 поступает на элемент 14 индикации. Единица с инверсного выхода RS-триггера 12 поступает на вход элемента 6 И-НЕ и на вход элемента 16 И, на выходе которого присутствует ноль, поступающий на элемент 18 индикации. На выходе элемента 6 И-НЕ присутствует единица (фиг. 2.5.6, 3.6.6, 4.6.6), которая установит выход элемента 7 коммутации в третье состояние с высокоимпедан- сным выходом или, иначе, в Z-состояние (фиг. 2.7.6, 3.7.6, 4.7.6), уровень которого поступит на информационный вход 1, а также на первый выход резистора 8 и на первый вход сумматора 9 по модулю два, на втором входе которого также присутствует Z-состояние (фиг. 2.1.6, 3.1.6, 4.1.6); следовательно, выход сумматора 9 по модулю два будет находиться в нуле (фиг. 2.9,6, 3.9.6, 4.9.6).

На вход элемента 10 ИЛ И-НЕ поступает единица с выхода элемента 6 И-НЕ. На выходе элемента 10 И Л И-НЕ присутствует ноль, который поступает на С-вход D-триггера 13.

Сигнал с выхода сумматора 9 по модулю два инвертируется элементом 11 НЕ, и на инверсном S-входе RS-триггера 12 присутствует единица.

На информационных выходах счетчика 21 установятся нули, которые поступают на информационные входы блока 22 индикации. Единица с прямого выхода D-триггера 3 поступает на вход элемента 20 И, на втором входе которого присутствует лог. О, поступающий с входа 19 тактирования подачи тестовых воздействий. Ноль с выхода элемента 20 И поступает на информационный вход счетчика 21.

Таким образом, после подачи короткого нулевого импульса на вход 4 сброса устройства элементы 14,17,18 индикации находятся в погашенном состоянии, и в устройстве установится режим ожидания появления лог. 1 на информационном входе 1 устройства. После подключения информационного входа 1 устройства к контролируемой цепи цифрового блока формируется сигнал, разрешающий генерацию входных тестовых воздействий, которые могут вырабатываться, например, внешним генератором тестовых воздействий. Под формированием разрешающего сигнала может пониматься, например, нажатие пользователем функциональной клавиши, которая вызовет подачу

тестовых воздействий на входные контакты цифрового блока.

Подача каждого нового тестового воздействия сопровождается подачей короткого единичного импульса на вход 19

тактирования подачи тестовых воздействий.

В процессе контроля возможны три ситуации:

1)В контролируемой цепи присутствует Z-состояние (1,5 В).

В этом случае на выходах элементов устройства никаких изменений не произойдет (фиг. 2.1.6).

Следует отметить, что данная ситуация невозможна при наличии короткого замыкания между контролируемой сигнальной цепью и шиной питания.

2)В контролируемой цепи присутствует лог. О (фиг. 3.1.в, 4.1.в), который поступит

на второй вход сумматора 9 по модулю два и вход элемента 10 ИЛ И-НЕ. Тогда на выводах резистора 8 появится разность потенциалов

40

AU0 IC

R,

где °вх - сила тока, истекающего из входного вывода интегрального элемента при наличии в цепи лог. в данном случае

это ток, истекающий из первого входа сумматора 9 по модулю два через резистор 8 в контролируемую цепь (для ТТЛ °Вх 1,6 мА);

R - величина резистора 8, расчет которой приведен ниже, причем

,

где Unop - минимальная разность потенци- алов между входами сумматора 9 мо модулю два, при которой его выход находится в состоянии лог. 1 (для ТТЛ Unop 2,0 В).

Следовательно, в устройстве для диагностирования цифровых блоков никаких изменений состояний логических уровней не произойдет (фиг. Зв, 4в).

Следует отметить, что данная ситуация невозможна при наличии короткого замыкания между контролируемой сигнальной цепью и шиной питания,

3) В контролируемой цепи присутствует лог. 1,или р-уровень лог. 1 появился в некоторый такт времени контроля (фиг. 2.1.г, 3.1.г, 4.1.г).

Тогда на выходе порогового элемента 2 произойдет изменение состояния из лог. О в лог. 1 (фиг. 2.2.г, 3.2.г, 4.2.г). Перепад из нуля в единицу поступит на С-вход D-триг- гера 3 и перебросит его инверсный выход с нуля в ед1 ицу. Причем последующие перепады из лог. О в лог. 1, поступающие на С-вход D-триггера З, не вызовут изменений состояний на его выходе; тем самым обеспечивается однократное срабатывание устройства от первого появления высокого логического уровня в контролируемой цепи.

Перепад из лог. О в лог. 1 с инверсного выхода D-триггера 3 (фиг. 2.3.г, 3.3.г, 4.3.г) поступит на первый вход элемента 15 И, на первый вход элемента 16 И и на вход одновибратора 5, который выработает единичный импульс длительностью Тимп (фиг. 2.5.г, 3.5.г, 4.5.г). На выходе элемента 6 И- НЕ появится ноль (фиг. 2.6.г, 3.6.г, 4.6.г), который переведет выход элемента 7 коммутации в лог. О (фиг. 2,7.г, 3.7,г, 4.7.г). Ноль с выхода элемента 6 И-НЕ поступит на второй вход элемента 10 ИЛИ-НЕ,

Устройство перейдет в режим инжектирования лог. О в контролируемую цепь, в которой присутствует лог. 1,

На прямом выходе D-триггера З появится лог. О, который запретит прохождение последующих импульсов тактирования подачи входных воздействий на информационный вход счетчика 21 импульсов через элемент 20 И.

Затем в зависимости от состояния, в котором находится контролируемая цепь, возможны три ситуации:

3.1) Контролируемая сигнальная цепь задействована в коротком замыкании с шиной питания.

Несмотря на то, что через резистор 8 течет ток, равный максимальному току, протекающему через открытый нижний интегральный транзистор выходного каскада элемента 7 коммутации, в контролируемой цепи и на первом входе сумматора 9 по модулю два присутствует высокий логический уровень.

Время воздействия устройства на контролируемую цепь (длительность инжектирования нуля) будет определяться

длительностью импульса Тимп, вырабатываемого одновибратором 5. Так как на обоих входах сумматора 9 по модулю два и втором входе элемента 10 ИЛИ-НЕ присутствуют высокие логическое уровни, то на выходах указанных элементов никаких изменений не произойдет (фиг, 2.9.г, 2.10.г). Следовательно, выходы триггеров 12 и 13 останутся без изменения (фиг. 2,12.г, 2.13.г).

Появление лог. О на втором входе элемента 6 И-НЕ вызовет появления на его выходе лог. 1 (фиг. 2.6.г), что приведет к переходу выхода элемента 7 коммутации в третье состояние с высокоимпедансным выходом и завершению процесса контроля цепи,

Содержимое счетчика 21 импульсов бу дет равно нулю, так как появление высокогс логического уровня в контролируемой цеш

предшествовало появлению первого им пульса тактирования подачи тестовых воз действий на втором входе элемента 20 И.

Таким образом, при наличии короткогс замыкания между контролируемой сигналь

ной цепью и шиной питания устройство от реагирует следующим образом: элементь 14 и 18 индикации погашены, а элемент 11 индикации включен.

Теперь рассмотрим ситуации, когда Е

контролируемой цепи присутствуют толькс источники логического сигнала.

Так как нижний транзистор выходногс каскада элемента 7 коммутации находится Е насыщении, то потенциал на выходе элемента 7 коммутации слабо зависит от величины втекающего в него тока от ИСТОЧНИКОЕ логического сигнала. Следовательно, можнс считать, что первый вывод резистора 8, информационный вход 1 и первый входсумматора 9 по модулю два подключены к источнику лог. О. На выходе элемента 1C ИЛИ-НЕ появится перепад из лог. О в лог. 1, который, поступив на С-вход D-триггерз 13, перебросит его прямой выход в ноль.

Уровень лог. О с прямого выхода D-триггера 13 поступит на второй вход элемента 15 И и перебросит его выход в ноль.

Уровень лог. 1 с инверсного выхода D-триггера 13 поступит на третий вход элемента 16 И.

Содержимое счетчика равно номеру такта входных воздействий, когда в контролируемой цепи появилась лог. 1. 3.2) В контролируемой цепи присутствует один источник логического сигнала, или иначе- исследуемая цепь не задействована в коротком замыкании с любой другой сигнальной цепью контролируемого цифрового блока.

На выводах резистора 8 и входах сумматора 9 по модулю два появится разность потенциалов, которая не превысит следующей величины:

Д1Г Он.тах + 1°вх К) R,

где 1н.тах - номинальная максимальная величина тока через резистор 8, в случае отсутствия короткого замыкания между сигнальными цепями (для ТТЛ н.тах 35 мА см. Скарлетт Дж. Транзисторно-транзисторные логические интегральные схемы и их применение. М.: Мир, 1974, с.57);

К - коэффициент нагрузочной способ- ности (коэффициент разветвления) (для ТТЛ типовое среднее значение нормальной нагрузочной способности, т.е. не низкая и не высокая нагрузочная способность, К 10, см. Дж.Фергусон и др. Обслуживание мик- ропроцессорных систем/Пер, с англ. М.: Мир, 1989, с.22).

Округленно AU 1,5 lH.max R, причем AU Unop,

что недостаточно для изменения логиче- ского уровня на выходе сумматора 9 по модулю два (фиг. 3.9.г), и, следовательно уровни логических сигналов на выходах RS-триггера 12 останутся без изменения (фиг. 3.12.г).

Тогда время проверки цепи будет определяться длительностью единичного импульса Т.ИМП, вырабатываемого одновибратором 5 (фиг. 3.5.г). Появление лог. О на втором входе элемента 6 И-НЕ вызовет по- явление на его выходе лог. 1 (фиг. 3.6.г), что приведет к переводу выхода элемента 7 коммутации в третье состояние с высокоимпедансным выходом (фиг. 3.7.г) и завершению процесса контроля це- пи (фиг. 3.1.г),

Таким образом, при отсутствии короткого замыкания исследуемой сигнальной цепи с любой другой сигнальной цепью контролируемого цифрового блока устройство отреагирует следующим образом: элементы 14 и 17 индикации погашены, а элемент 18 индикации включен.

3.3) В контролируемой цепи присутствует более одного источника логического сиг- нала в цепи, или иначе - исследуемая цепь задействована в коротком замыкании с другой сигнальной цепью (цепями) контролируемого цифрового блока.

При достижении током, протекающим через резистор 8, величины

mop Inop/R,

где R - величина резистора 8, которая должна удовлетворять условию

Unop/mop R Unop/Он.тах + I вх К), Inop 2 н.тах,

изменяется логический уровень на выходе сумматора 9 по модулю два с нуля на единицу (фиг. 3.9.г). Это приведет к появлению перепада из единицы в ноль на выходе элемента 11 НЕ, который установит прямой выход RS-триггера 12 в единицу (фиг, 4.12.г), и включится элемент 14 индикации.

На инверсном выходе RS-триггера 12 появится лог. О, который поступит на второй вход элемента 16 И и на первый вход элемента 6 И-НЕ, на выходе которого появится лог. 1 (фиг. 4.6.г). Элемент 7 коммутации перейдет в третье состояние с высокоимпедансным выходом (фиг. 4,7.г). На этом процесс проверки цепи завершится (фиг. 4.1.г) до окончания импульса, вырабатываемого одновибратором 5 (фиг. 4.5.г).

Таким образом, при наличии короткого замыкания между исследуемой сигнальной цепью и любой другой сигнальной цепью контролируемого цифрового блока устройство отреагирует следующим образом: элементы 17 и 18 индикации погашены, а элемент 14 индикации включен.

После окончания проверки цепи устройство перейдет в режим отображения результатов контроля (фиг. 2д, Зд, 4д), и процесс подачи тестовых воздействий можно прекратить. Для осуществления последующих проверок необходимо:

-подать сигнал в виде короткого нулевого импульса на вход 4 сброса устройства;

-подключить информационный вход 1 устройства к контролируемой цепи;

-начать или продолжить подачу тестовых воздействий в зависимости от требований, предъявляемых к процессу контроля цифрового блока.

Функционирование устройства основано на инжектировании лог. О в контролируемый печатный проводник цифрового блока в момент первого появления лог. 1 в исследуемой цепи и анализе реакции цепи на данное воздействие. Длительность инжектирования лог. О в контролируемую цепь равна: 1Имп в случае наличия короткого замыкания исследуемого сигнального печатного проводника с шиной питания (фиг. 2.1.г), а также в случае отсутствия короткого замыкания исследуемого сигнального печатного проводника с любой другой сигнальной цепью (фиг. 3.1.г); хв.п. в случае наличия короткого замыкания исследуемого сигнального печатного проводника с другим сигнальным печатным проводником (фиг. 4.1.г) контролируемого цифрового блока. Известно, что такой режим интегральный транзистор может выдержать не более 1 с и,

следовательно, воздействие устройства является допустимым по техническим услови- ям ИМС ТТЛ (см. Справочник по интегральным микросхемам//В.Б.Тараб- рин, С.В.Якубовский, Н.А.Барканов и др./Под ред. Б.В.Тарабарина. М,: Энергия, 1981,с.520).

Таким образом, можно сделать вывод, что включение выхода элемента 6 И-НЕ с входом элемента 10 ИЛ И-НЕ с точки зрения распознавания КЗ позволяет идентифицировать две ситуации: наличие и отсутствие КЗ контролируемого печатного проводника с шиной питания.

Триггеп 13 представляет собой регист- ратор факкз обнаружения перепад из лог. О в лог. 1 на выходе элемента 10 ИЛИ-НЕ:

а)факт наличия перепада свидетельствует от отсутствии КЗ контролируемого печатного проводника с шиной питания;

б)факт отсутствия перепада, в свою очередь, свидетельствует о наличии КЗ контролируемого печатного проводника с шиной питания.

Наличие элемента 15 И обеспечивает вывод информации с выхода D-триггера 13 на светодиод 17 только после регистрации появления лог. 1 на информационном входе 1 устройства.

Триггер 13 хранит информацию в ре- зультате проверки на наличие (отсутствие) КЗ контролируемого печатного проводника с шиной питания.

Элемент 15 И проверяет условия для вывода информации о результате проверки контролируемой цепи на светодиод 17 - индикатор наличия КЗ с шиной питания и тем самым исключает вывод какой-либо информации с выхода D-триггера 13, когда устройство находится в режиме ожидания появления лог. 1 на информационном входе 1 устройства.

Элемент 16 И и элемент 15 И дешифрируют две несовместимые ситуации, соответственно:

а)отсутствие КЗ с шиной питания и любой другой сигнальной цепью контролируемого цифрового блока;

б)наличие КЗ исследуемой сигнальной цепи с шиной питания.

Формула изобретения Устройство для контроля цифровых блоков по авт. св. СССР № 1709318, о т л и ч а ю щ е е с я тем, что, с целью увеличени информативности контроля, оно содержит второй и третий элементы И, счетчик, эле мент ИЛИ-НЕ, третий триггер, причем вхо; установки третьего триггера соединен с вхо дом сброса устройства и входом сброс; счетчика, инверсный выход третьего D-триг гера соединен с третьим входом первой элемента И, прямой выход третьего D-триг гера соединен с первым входом второго эле мента И, второй вход которого соединен t инверсным выходом второго D-триггера выход второго элемента И является выхо дом признака короткого замыкания устрой ства, первый и второй входы элемент; ИЛИ-НЕ соединены с информационнь входом устройства и с выходом элемент; И-НЕ соответственно, выход элемент; ИЛИ-НЕ соединен с входом синхронизацт третьего D-триггера, информационный вхо/ которого соединен с шиной логического ну ля устройства, прямой выход второго триг гера соединен с первым входом третьегс элемента И, второй вход которого соеди нен с входом синхронизации устройства выход третьего элемента И соединен с вхо дом счета счетчика, выход которого явля ется выходом количества, тактов контрол устройства.

/rOfiPm

Ј

i t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1989 |

|

SU1709318A1 |

| Устройство для автоматического контроля печатных плат | 1985 |

|

SU1291902A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1989 |

|

SU1732332A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1288700A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для контроля и настройки цифровых узлов | 1983 |

|

SU1114994A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для бесконтактного измерения импульсного тока | 1985 |

|

SU1307404A1 |

| Устройство для контроля и диагностики цифровых устройств | 1987 |

|

SU1583914A2 |

Изобретение позволяет увеличить информативность контроля. Устройство содержит триггеры 3, 12, 13, элементы И 15, 16, 20, элемент И-НЕ 6, элемент ИЛИ-НЕ 10. элемент НЕ 11, сумматор по модулю два 9, элемент коммутации 7. одновибратор 5, счетчик 21. резистор 8. 4 ил.

Ф#г. У

i

i t

| Устройство для контроля цифровых блоков | 1989 |

|

SU1709318A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ приготовления консистентных мазей | 1919 |

|

SU1990A1 |

Авторы

Даты

1993-07-23—Публикация

1990-12-17—Подача