СО

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Система асинхронной двусторонней передачи данных между передающей и приемной станциями | 1983 |

|

SU1521297A3 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

| СИСТЕМА ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ, СИСТЕМА СИНХРОНИЗАЦИИ ДЛЯ СИСТЕМЫ ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ШИФРАЦИИ ИЛИ ДЕШИФРАЦИИ ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЗАСЕКРЕЧЕННОЙ ПЕРЕДАЧИ И ПРИЕМА РЕЧЕВОЙ ИНФОРМАЦИИ | 1996 |

|

RU2099885C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Способ цикловой синхронизации с динамической адресацией получателя | 2016 |

|

RU2621181C1 |

| Устройство для кодирования и декодирования цифрового телевизионного сигнала | 1988 |

|

SU1566485A1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

Изобретение относится к вычислительной технике и связи. Его использование в технике цифровой передачи данных позволяет повысить точность симметрирования. Устройство содержит на передающей стороне регистр 1 сдвига, параллельно-последовательный регистр 2, счетчики 3, 4 четности и управляемый инвертор 5, на приемной стороне - регистр 11 сдвига, блок 14 синхронизации приема и управляемый инвертор 13. Благодаря введению на передающей стороне элемента И 6, элемента НЕ 7, блока 8 синхронизации передачи и источника 9 (логической единицы, а на приемной стороне - параллельно-последовательного регистра 13 в устройстве обеспечивается более точное симметрирование передаваемого сигнала.4 ил.

со

го

Ч)

fr 2lT т

00

Изобретение относится к вычислительной технике и связи и может быть использовано в технике цифровой передачи данных.

Цель изобретения - повышение точности симметрирования.

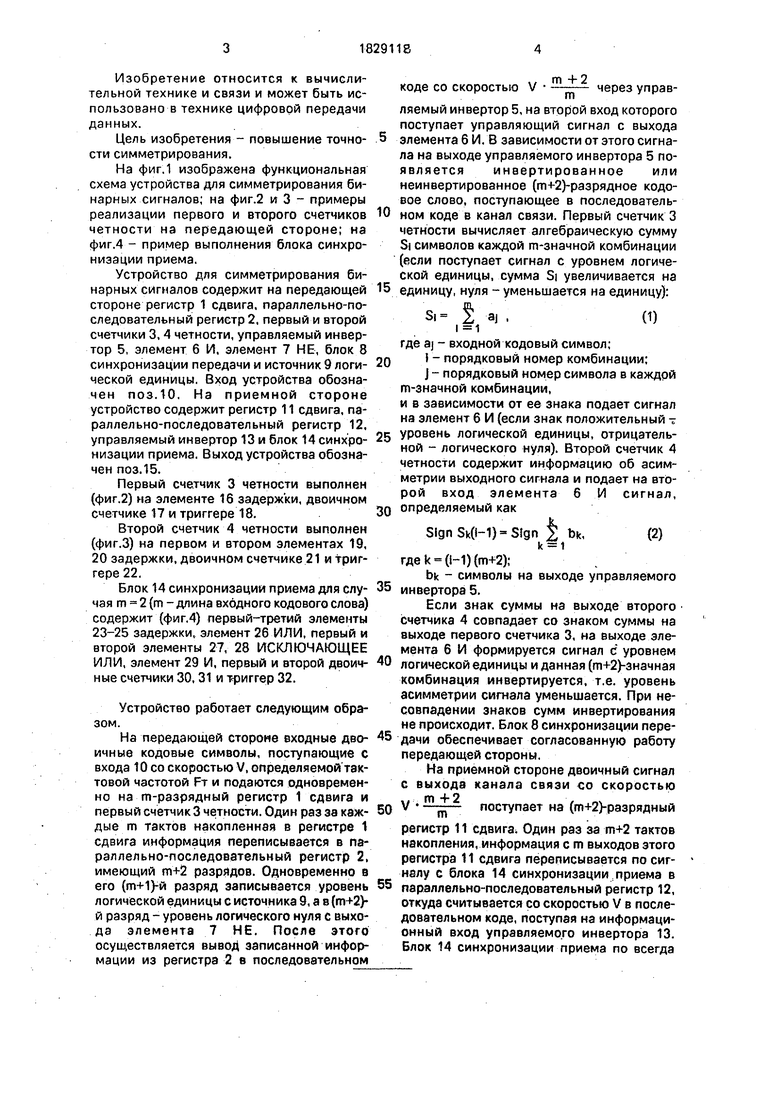

На фиг.1 изображена функциональная схема устройства для симметрирования бинарных сигналов; на фиг.2 и 3 - примеры реализации первого и второго счетчиков четности на передающей стороне; на фиг.4 - пример выполнения блока синхронизации приема.

Устройство для симметрирования бинарных сигналов содержит на передающей стороне регистр 1 сдвига, параллельно-последовательный регистр 2, первый и второй счетчики 3, А четности, управляемый инвертор 5, элемент б И, элемент 7 НЕ, блок 8 синхронизации передачи и источник 9 логической единицы. Вход устройства обозначен поз.10. На приемной стороне устройство содержит регистр 11 сдвига, параллельно-последовательный регистр 12, управляемый инвертор 13 и блок 14 синхронизации приема. Выход устройства обозначен поз. 15.

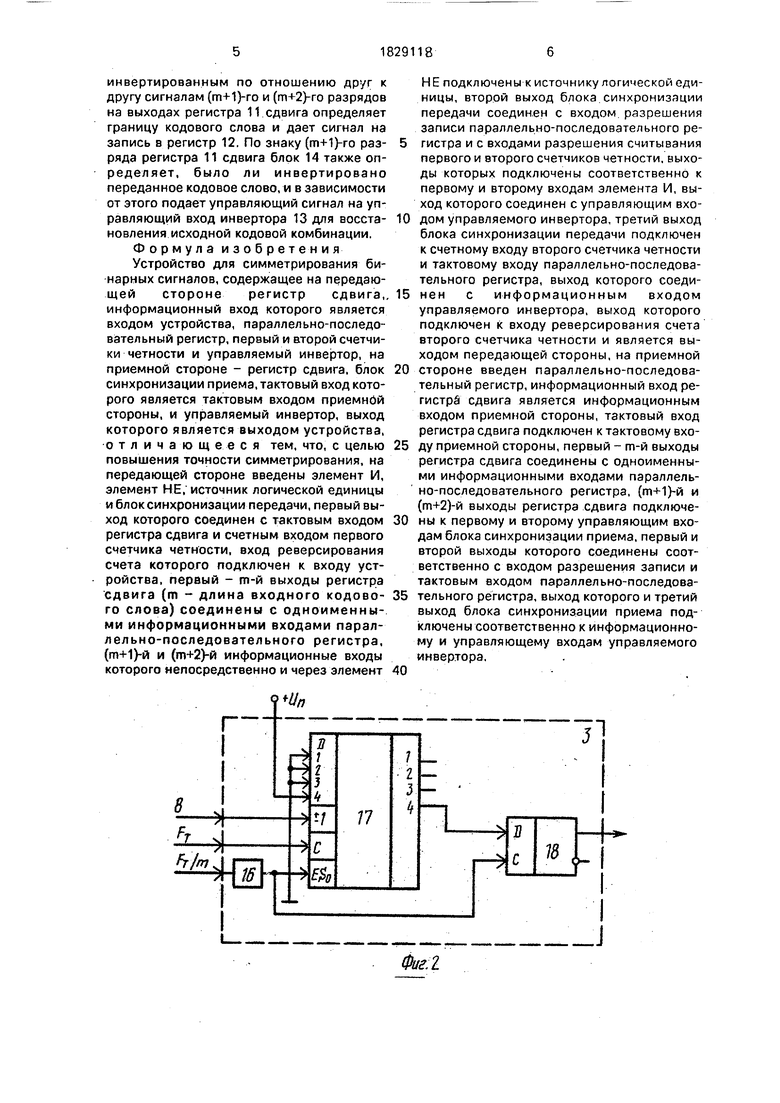

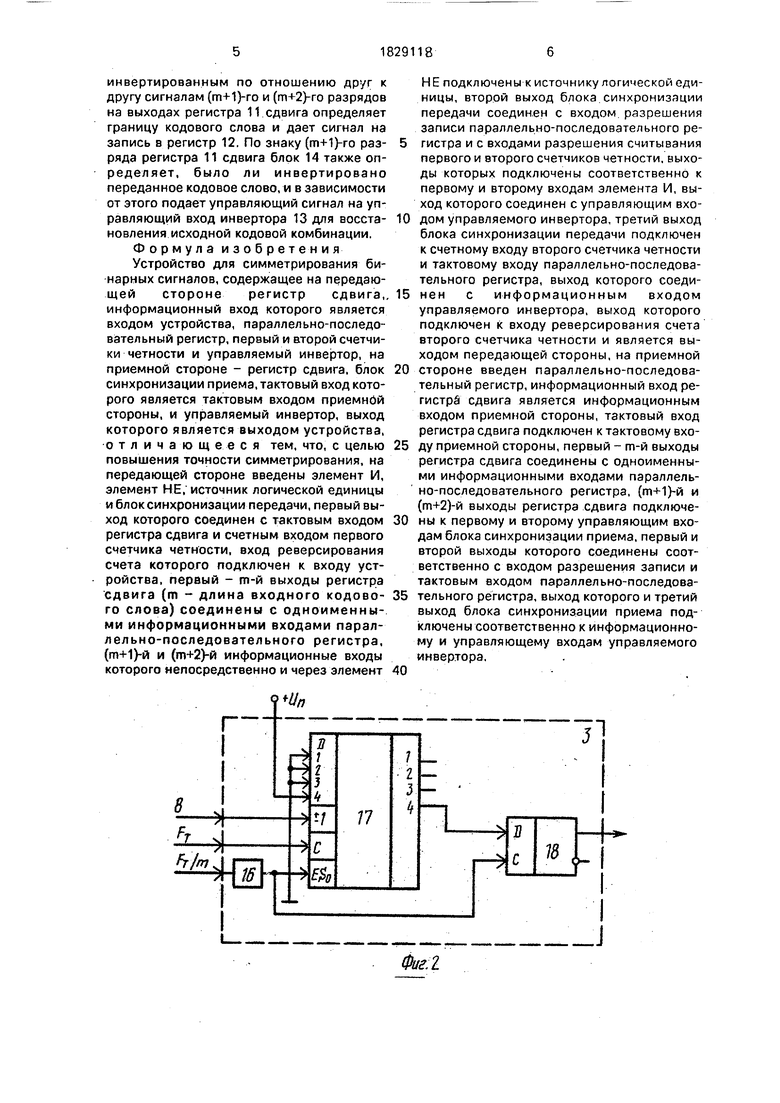

Первый счетчик 3 четности выполнен (фиг.2) на элементе 16 задержки, двоичном счетчике 17 и триггере 18.

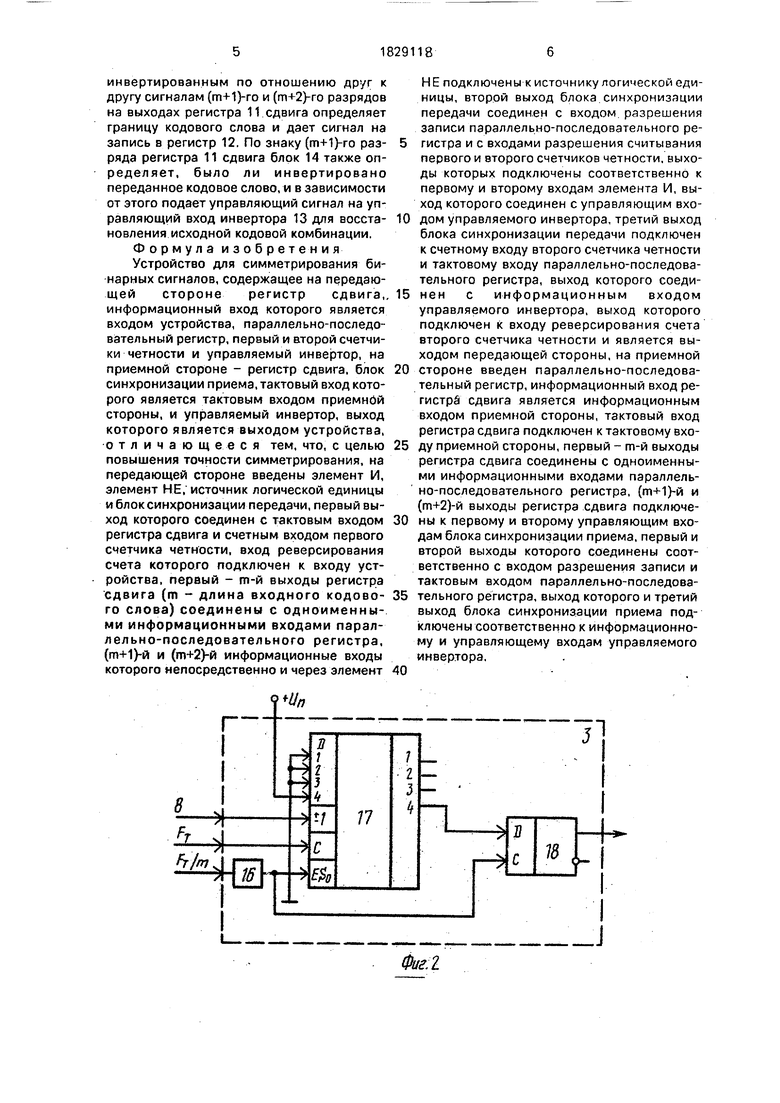

Второй счетчик 4 четности выполнен (фиг.З) на первом и втором элементах 19, 20 задержки, двоичном счетчике 21 и триггере 22.

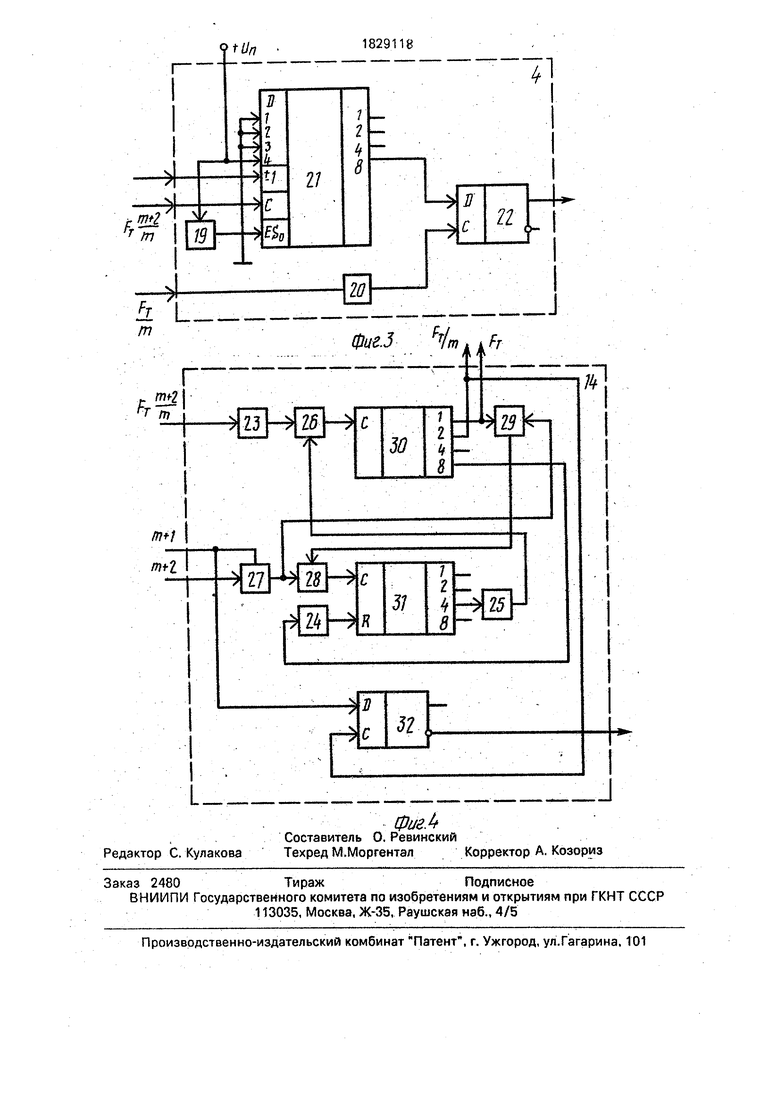

Блок 14 синхронизации приема для случая m 2 (m - длина входного кодового слова) содержит (фиг.4) лервый-третий элементы 23-25 задержки, элемент 26 ИЛИ, первый и второй элементы 27, 28 ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент 29 И, первый и второй двоичные счетчики 30,31 и триггер 32.

Устройство работает следующим образом.

На передающей стороне входные двоичные кодовые символы, поступающие с входа 10 со скоростью V, определяемой тактовой частотой FT и подаются одновременно на m-разрядный регистр 1 сдвига и первый счетчик 3 четности. Один раз за каждые m тактов накопленная в регистре 1 сдвига информация переписывается в параллельно-последовательный регистр 2, имеющий т+2 разрядов. Одновременно в его (т+1)-й разряд записывается уровень логической единицы с источника 9, а в (т+2)- й разряд - уровень логического нуля с выхода элемента 7 НЕ. После этого осуществляется вывод записанной информации из регистра 2 в последовательном

t fj

коде со скоростью V через управляемый инвертор 5, на второй вход которого поступает управляющий сигнал с выхода

элемента 6 И. В зависимости от этого сигнала на выходе управляемого инвертора 5 появляется инвертированное или неинвертированное (т+2)-разрядное кодовое слово, поступающее в последовательном коде в канал связи. Первый счетчик 3 четности вычисляет алгебраическую сумму Si символов каждой m-значной комбинации (если поступает сигнал с уровнем логической единицы, сумма Si увеличивается на

5 единицу, нуля - уменьшается на единицу):

S, 5 aj .(1)

0

5

0

i 1 где а - входной кодовый символ;

J - порядковый номер комбинации;

J - порядковый номер символа в каждой m-значной комбинации, и в зависимости от ее знака подает сигнал на элемент 6 И (если знак положительный - уровень логической единицы, отрицательной - логического нуля). Второй счетчик 4 четности содержит информацию об асимметрии выходного сигнала и подает на второй вход элемента 6 И сигнал, определяемый как

Sign Sk(M)° Sign % bk,(2)

k 1

гдек (1-1)(т+2); . .

bk - символы на выходе управляемого инвертора 5.

Если знак суммы на выходе второго счетчика 4 совпадает со знаком суммы на выходе первого счетчика 3, на выходе элемента 6 И формируется сигнал с уровнем

0 логической единицы и данная (т+2)-значная комбинация инвертируется, т.е. уровень асимметрии сигнала уменьшается. При несовпадении знаков сумм инвертирования не происходит. Блок 8 синхронизации пере5 дачи обеспечивает согласованную работу передающей стороны.

На приемной стороне двоичный сигнал с выхода канала связи со скоростью

V --- поступает на (т+2)-разрядный

5

0

5

m

регистр 11 сдвига Один раз за т+2 тактов накопления, информация с m выходов этого регистра 11 сдвига переписывается по сигналу с блока 14 синхронизации,приема в параллельно-последовательный регистр 12, откуда считывается со скоростью V в последовательном коде, поступая на информационный вход управляемого инвертора 13. Блок 14 синхронизации приема по всегда

инвертированным по отношению друг к другу сигналам (m+1)-ro и (т+2)-го разрядов на выходах регистра 11 сдвига определяет границу кодового слова и дает сигнал на запись в регистр 12. По знаку (т+1)-го раз- ряда регистра 11 сдвига блок 14 также определяет, было ли инвертировано переданное кодовое слово, и в зависимости от этого подает управляющий сигнал на управляющий вход инвертора 13 для восста- новления исходной кодовой комбинации. Формула изобретения Устройство для симметрирования бинарных сигналов, содержащее на передающей стороне регистр сдвига, информационный вход которого является входом устройства, параллельно-последовательный регистр, первый и второй счетчики четности и управляемый инвертор, на приемной стороне - регистр сдвига, блок синхронизации приема, тактовый вход которого является тактовым входом приемной стороны, и управляемый инвертор, выход которого является выходом устройства, о т л и ч а ю щ ее с я тем, что, с целью повышения точности симметрирования, на передающей стороне введены элемент И, элемент НЕ, источник логической единицы и блок синхронизации передачи, первый выход которого соединен с тактовым входом регистра сдвига и счетным входом первого счетчика четности, вход реверсирования счета которого подключен к входу устройства, первый - т-й выходы регистра сдвига (т - длина входного кодово- го слова) соединены с одноименными информационными входами параллельно-последовательного регистра, (т+1)-й и (т+2)-й информационные входы которого непосредственно и через элемент

.

Фаг.1

НЕ подключены к источнику логической единицы, второй выход блока.синхронизации передачи соединен с входом, разрешения записи параллельно-последовательного регистра и с входами разрешения считывания первого и второго счетчиков четности, выходы которых подключены соответственно к первому и второму входам элемента И, выход которого соединен с управляющим входом управляемого инвертора, третий выход блока синхронизации передачи подключен к счетному входу второго счетчика четности и тактовому входу параллельно-последовательного регистра, выход которого соединен с информационным входом управляемого инвертора, выход которого подключен к входу реверсирования счета второго счетчика четности и является выходом передающей стороны, на приемной стороне введен параллельно-последовательный регистр, информационный вход ре- гистр§ сдвига является информационным входом приемной стороны, тактовый вход регистра сдвига подключен к тактовому входу приемной стороны, первый - m-й выходы регистра сдвига соединены с одноименными информационными входами параллельно-последовательного регистра, (т+1)-й и (т+2)-й выходы регистра сдвига подключены к первому и второму управляющим входам блока синхронизации приема, первый и второй выходы которого соединены соответственно с входом разрешения записи и тактовым входом параллельно-последовательного регистра, выход которого и третий выход блока синхронизации приема подключены соответственно к информационному и управляющему входам управляемого инвертора.

L

Редактор С. Кулакова

ФиеЛ

Составитель О. Ревинский

Техред М.МоргенталКорректор А. Козориз

| Устройство симметрирования бинарных сигналов | 1972 |

|

SU476696A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| РЕГУЛЯТОР РОСТА И РАЗВИТИЯ РАСТЕНИЙ | 1992 |

|

RU2072998C1 |

Авторы

Даты

1993-07-23—Публикация

1990-10-22—Подача