Изобретение относится к области автоматики и вычислительной техники и может быть эффективно использовано при организации псевдослучайного тестирования многоразрядных суммирующих схем.

Целью изобретения является уменьшение длительности интервала времени псевдоисчерпывающего тестирования параллельного двоичного, сумматора.

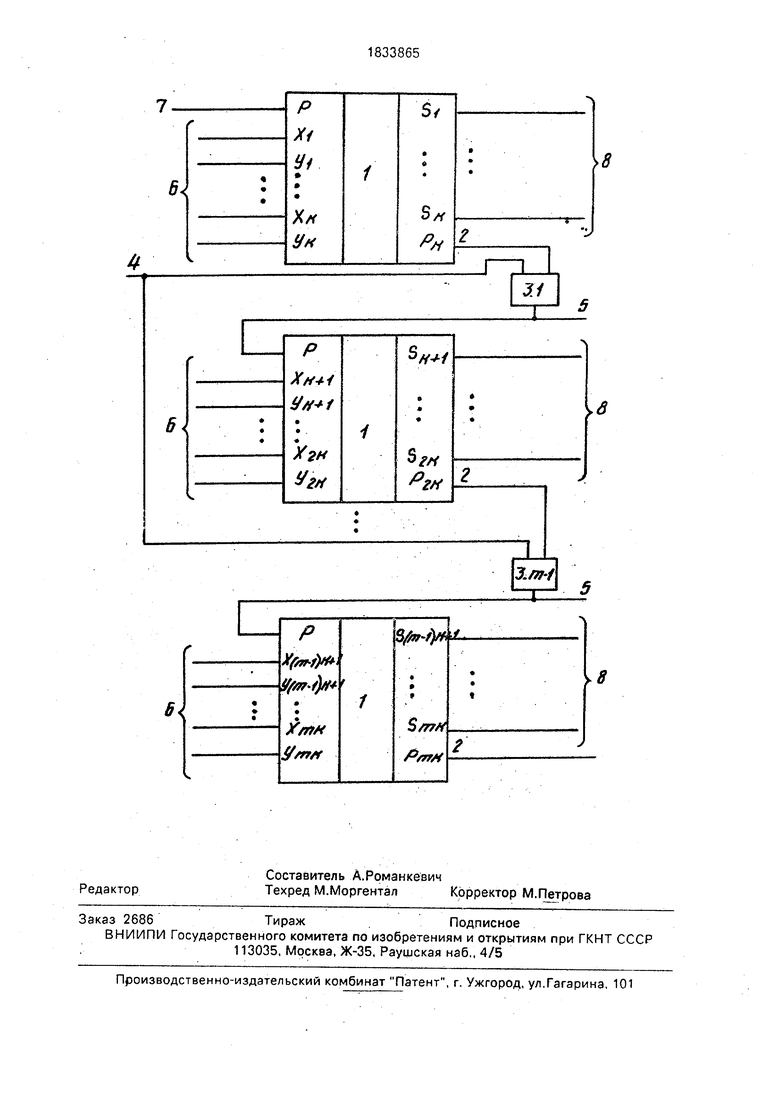

На чертеже представлена структура N- разрядного параллельного сумматора.

. N-разрядный параллельный двоичный сумматор содержит группу из mk-разрядных двоичных сумматоров i (N « nv k), выход 2 переноса каждого из которых (кроме m-ro сумматора 1) подключен к первому входу

соответствующего двухвходового сумматора 3 по модулю два группы. Второй вход каждого из сумматоров 3 группы связан с тестовым входом 4 параллельного суммато- ра. При этом выход 5 i-го (i 1, m - 1) сумматора 3 группы из (т -1) двухвходовых сумматоров 3 по модулю два подсоединен одновременно к входу переноса (I + 1)-го сумматора 1 группы и к соответствующему тестовому выходу 5 параллельного сумматора. Входы 6 каждого из сумматоров 1 группы являются входами суммирования операндов. Вход 7 первого сумматора 1 группы является входом суммирования внешнего переноса N-разрядного параллельного сумматора. Выходы 8 каждого из сумматоров 1

00

со со

00

о ел

группы являются выходами суммы М-раз- рядного параллельного сумматора.

Предлагаемый сумматор функционирует в двух режимах: первый - системный режим (выполнение функции суммирования системных операндов), второй - тестовый режим (проведение проверки правильности функционирования N-разрядного параллельного сумматора).

Рассмотрим работу N-разрядного параллельного сумматора в системном режиме. На входе 4 оператором с пульта управления устанавливается потенциал, соответствующий уровню логического нуля. При этом сумматоры 3 группы выполняют функции повторителей сигналов с выходов 2 соответствующих сумматоров 1 группы. На входы 6 параллельного сумматора поступают N-разрядные (N m k) двоичные опе- ранды, а на выходах 8 формируется N-разрядная суммарна выходе 2 последнего сумматора 1 группы формируется сигнал переноса). Выходы 5 N-разрядного параллель- ного сумматора не используются как информационные.

В тестовом режиме на входы 4, 6 и 7 N-разрядного параллельного сумматора поступают стимулирующие воздействия с вы- ходов генератора псевдослучайных последовательностей, а выходы 5, 8 и 2 под- . ключаются к входам многоканального сигнатурного анализатора. В результате при проведении псевдослучайного тестирования проверка N-разрядного параллельного сумматора сводится к параллельной и независимой проверке mk-разрядных двоичных сумматоров 1, что уменьшает время псевдоисчерпывающего тестирования N-разрядного параллельного сумматора. Параллельная и независимая проверка mk- разрядных сумматоров 1 обеспечивается следующим свойством сумматора по модулю два: при подаче на один из входов двух- входового сумматора 3 по модулю два псевдослучайной последовательности (т.е. последовательности двоичных сигналов с вероятностью появления Рпсп 0,5 единичного (нулевого) сигнала) вероятность появления единичного (нулевого) сигнала на выходе сумматора по модулю два будет также равна 0,5:

Рсм2 Рпсп + Рс-2РПсп Рс,

где РСм2, Рпсп, Рс - вероятности появления единичного сигнала на выходе двухвхо- дового сумматора по модулю два, выходе генератора псевдослучайных последовательностей и з системной последовательности сигналов, поступающих на второй вход двухвходово о сумматора по модулю два в тестовом режиме, соответственно. Так как Рпсп 0,5, то Рсм2 0,54ЈРс-2 -0,5 Рс 0.5 Следствие: сигналы на выходе сумматора по модулю два являются статистически

независимыми от системных сигналов при

подаче на один из его входов псевдослучайной последовательности.

Таким образом, технико-экономическая эффективность заявляемого N-разрядного параллельного сумматора по сравнению .с

прототипом определяется уменьшением длительности псевдоисчерпывающего тестирования за счет того, что при проведении процедуры псевдослучайного тестирования проверяемый параллельный сумматор разбивается на группу двоичных сумматоров меньшей разрядности, тестируемых параллельно и независимо друг от друга.

С наибольшей эффективностью можно использовать заявляемый N-разрядный параллельный сумматор для организации самотестирования комбинационных схем, входящих в состав БИС и СБИС, где наибольшее распространение нашли методы компактного тестирования.

Формула изобретения

N-разрядный параллельный сумматор, содержащий группу из m К-разрядных двоичных сумматоров (причем N m К), первый и второй информационные входы которых

соединены с входами соответствующих разрядов первого и второго слагаемого сумматора, выходы результата которого соединены с выходами суммы всех К-разрядных двоичных сумматоров группы и переноса m-ro К-разрядного двоичного сумматора группы, вход переноса первого К-разрядного двоичного сумматора группы соединен с входом переноса сумматора, отличающийся тем, что, с целью уменьшения длительности псевдоисчерпывающего тестирования, сумматор содержит группу сумматоров по модулю два, причем выход

i-ro сумматора по модулю два (где 1 1,2

m - 1) соединен с входом переноса (I + 1)-го

К-разрядного двоичного сумматора группы и с i-м тестовым выходом сумматора, выход переноса i-ro К-разрядного двоичного сумматора группы соединен с первым входом 1-го сумматора по модулю два группы, второй вход которого соединен с тестовым входом сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

| Устройство для умножения | 1988 |

|

SU1603379A1 |

| Преобразователь @ -разрядного двоичного числа в его представление по модулю @ | 1982 |

|

SU1076899A1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ M N-РАЗРЯДНЫХ ЧИСЕЛ | 2012 |

|

RU2486576C1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| Конвейерный сумматор | 1983 |

|

SU1137460A1 |

| Тестопригодный цифровой автомат | 1990 |

|

SU1829036A1 |

| Матричный вычислитель | 1983 |

|

SU1137464A1 |

| Генератор псевдослучайных чисел | 1979 |

|

SU868734A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении легко тестируемых многоразрядных суммирующих схем. Целью изобретения является уменьшение длительности псевдоисчерпывающего тестирования параллельного сумматора, N- разрядный параллельный сумматор содержит mk-разрядных (k N) сумматоров 1, выходы 2 переноса сумматоров, группу из (т -1) двухвходовых сумматоров 3 по модулю два, тестовый вход 4 сумматора, тестовые выходы. 5. входы 6 суммирования операндов, вход 7 переноса, выходы 8 суммы. N-разрядный параллельный сумматор позволяет сократить время контроля суммирующих схем псевдослучайными наборами и может быть эффективно использован для построения контроле-пригодных цифровых блоков. 1 ил. Ч«г Ё

| Корнейчук В.И., Тарасенко В.П., Ми- шинский Ю.Н | |||

| Вычислительные устройства на микросхемах, Справочник | |||

| Киев, Техника, 1986, рис, 2.19в, стр | |||

| Льночесальная машина | 1923 |

|

SU245A1 |

| Корнейчук В.И., Тарасенко В.П., Ми- шинский Ю.Н | |||

| Вычислительные устройства на микросхемах, Справочник, Киев, Техника, 1986, рис | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Льночесальная машина | 1923 |

|

SU245A1 |

Авторы

Даты

1993-08-15—Публикация

1991-04-18—Подача