Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных устройств, работающих в коде "1 из К".

Целью изобретения является повышение производительности последовательного К-ичного сумматора.

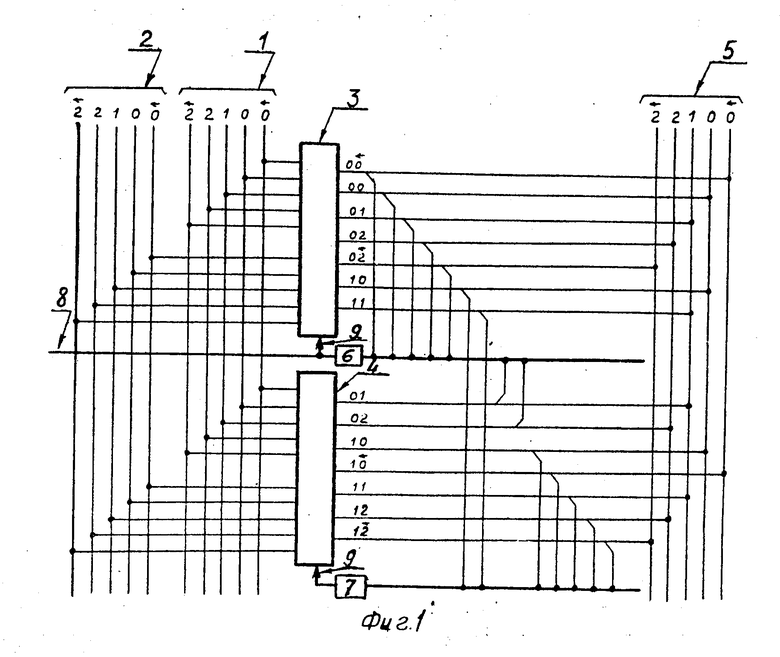

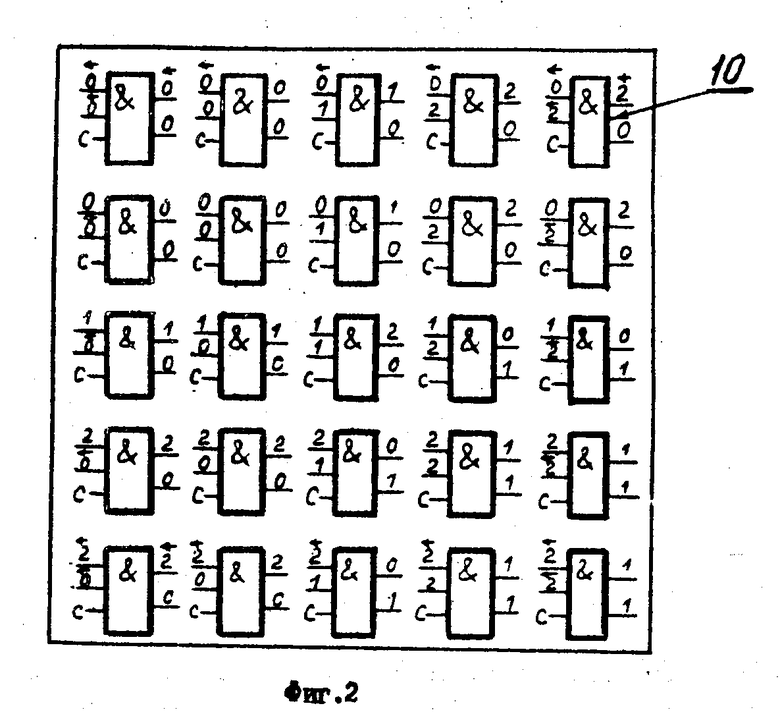

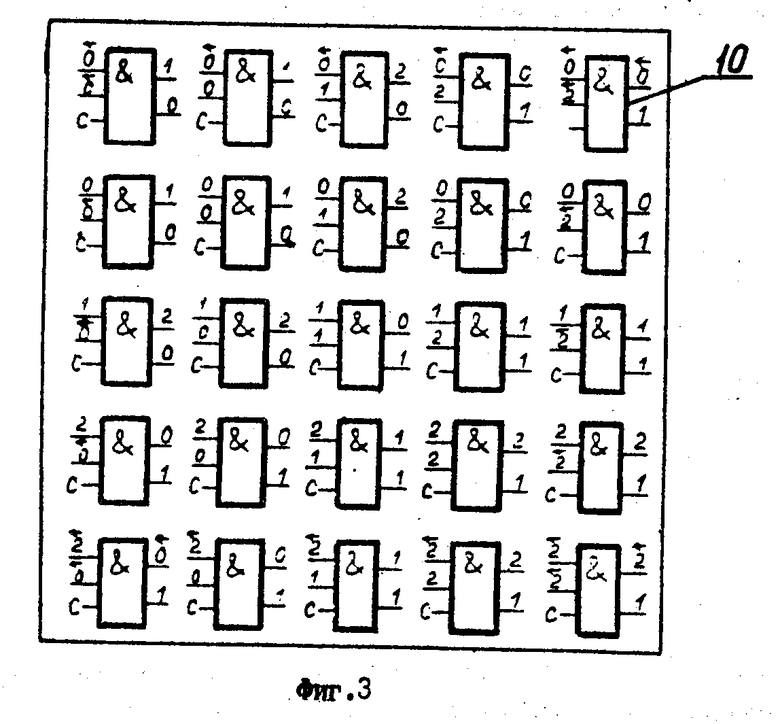

На фиг. 1 приведена структурная схема последовательного К-ичного сумматора для К 3 и N 2; на фиг. 2 и 3 вариант построения сумматора цифр с учетом его использования в качестве первого и второго для структуры последовательного сумматора, приведенной на фиг. 1.

Последовательный К-ичный сумматор содержит входы 1 и 2 операндов, сумматоры 3 и 4 цифр (СЦ), выход 5 суммы, элементы 6 и 7 задержки, вход запуска 8. Каждый сумматор цифр содержит также управляющий вход 9. Каждый сумматор цифр представляет собой матрицу из (К+2)N двухвыходных элементов И 10.

Повышение производительности достигается за счет автоматического вырабатывания сигнала конца счета (сигнала останова). Этот сигнал есть реакция на поступление на вход сумматора цифр старших значащих разрядов складываемых чисел. Вырабатывание его позволяет, не теряя времени, включить в работу другие устройства, зависящие от сумматора. Для этой цели цифровой алфавит расширяется символами  и

и  , введенными во все входы и выход сумматора. При этом

, введенными во все входы и выход сумматора. При этом  соответствует окончанию положительного числа, а

соответствует окончанию положительного числа, а  окончанию отрицательного числа. Таким образом, последовательный сумматор способен суммировать положительные и отрицательные числа с переменной разрядностью, фиксируя реальный момент окончания суммирования.

окончанию отрицательного числа. Таким образом, последовательный сумматор способен суммировать положительные и отрицательные числа с переменной разрядностью, фиксируя реальный момент окончания суммирования.

Последовательный сумматор работает следующим образом.

Цифры складываемых чисел поступают на входы разрядно и потактно, т.е. в такте t 0 поступает пара цифр (хо2хо1), в такте t 1 пара цифр [ x 1, а на вход 2 -

1, а на вход 2 - 2, генерируя соответствующий сигнал на выходе СЦ. При этом возможны два случая: или на выходе появится сигнал, отличный от

2, генерируя соответствующий сигнал на выходе СЦ. При этом возможны два случая: или на выходе появится сигнал, отличный от  , или на выходе появится сигнал, совпадающий с

, или на выходе появится сигнал, совпадающий с  где τ

где τ  , или

, или

. Вследствие этого следующий такт нельзя еще гарантированно считать моментом окончания счета (ибо возможно в этом такте появление сигнала, отличного от

. Вследствие этого следующий такт нельзя еще гарантированно считать моментом окончания счета (ибо возможно в этом такте появление сигнала, отличного от  ). В таком случае на вход сумматора еще раз подается пара сигналов

). В таком случае на вход сумматора еще раз подается пара сигналов  . После этого в следующем такте на выходе гарантированно появится сигнал

. После этого в следующем такте на выходе гарантированно появится сигнал  означающий, что в числе, изображающем сумму, появился старший разряд, левее которого в бесконечном количестве сплошь идет сигнал τ (.000Yr+1. если сумма число положительное,222Yr+1. если сумма число отрицательное). Появление на выходе сигнала

означающий, что в числе, изображающем сумму, появился старший разряд, левее которого в бесконечном количестве сплошь идет сигнал τ (.000Yr+1. если сумма число положительное,222Yr+1. если сумма число отрицательное). Появление на выходе сигнала  служит, таким образом, сигналом окончания счета в сумматоре и в следующий момент можно включать в работу зависящие от него устройства. На этом основана экономия времени счета, ибо таким способом фиксируется момент получения суммы независимо от количества разрядов в ней: трехразрядная сумма будет зафиксирована в такте t 3, а двадцатиразрядная в такте t 20, причем делается это автоматически самим сумматором.

служит, таким образом, сигналом окончания счета в сумматоре и в следующий момент можно включать в работу зависящие от него устройства. На этом основана экономия времени счета, ибо таким способом фиксируется момент получения суммы независимо от количества разрядов в ней: трехразрядная сумма будет зафиксирована в такте t 3, а двадцатиразрядная в такте t 20, причем делается это автоматически самим сумматором.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования | 1977 |

|

SU734678A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

| Устройство для сложения чисел в из-быТОчНОй СиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824199A1 |

| Устройство для умножения последовательного действия | 1983 |

|

SU1157541A1 |

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| Устройство для суммирования | 1976 |

|

SU674018A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах, работающих в коде 1 из К. Целью изобретения является повышение производительности. Цель достигается введением в последовательный сумматор, содержащий N сумматоров цифр и N элементов задержки, в каждой группе входов и в группе выходов дополнительных входов и выходов положительного и отрицательного окончания, имеющих веса соответственно младшей и старшей цифры. Введены также новые связи сумматоров цифр с введенными входами и выходами и изменена структура сумматора цифр. Это позволяет фиксировать реальные моменты окончания суммирования положительных и отрицательных чисел в последовательном К-ичном коде независимо от количества разрядов в представлении чисел. 3 ил.

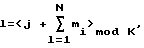

ПОСЛЕДОВАТЕЛЬНЫЙ К-ИЧНЫЙ СУММАТОР ДЛЯ ОДНОВРЕМЕННОГО СЛОЖЕНИЯ N ЧИСЕЛ, содержащий N сумматоров цифр и N элементов задержки, группы входов с первой по N-ю всех сумматоров цифр соединены с соответствующими входами операндов последовательного сумматора, управляющие входы сумматоров цифр соединены с выходами соответствующих элементов задержки, а управляющий вход первого сумматора цифр подключен к входу запуска сумматора, каждый i-й выход первой группы выходов j-го сумматора цифр, где i = 0, ..., N (K - 1), j = 0, ..., (N - 1), соединен с <i+j>modK-м выходом последовательного сумматора, где <x>modR означает остаток отделения X на R, каждый i-й выход второй группы выходов j-го сумматора цифр соединен с входом >i+j<modK-го элемента задержки, где >x<modR означает ближайшее меньшее частное от деления X на R, каждый сумматор цифр содержит КN двухвыходных элементов И, причем каждый l-й вход каждого элемента И соединен с одним из входов l-й группы входов сумматора цифр, где l = 1, ..., N, так, что образуются все возможные сочетания номеров входов в группах, (N + 1)-е входы всех элементов И соединены с управляющим входом сумматора цифр, первый и второй выходы каждого элемента И соединены с j-ми выходами соответственно первой и второй групп выходов так, что

где mi - номер входа в i-й группе входов, к которому подключен i-й вход данного элемента И, mi = 0, ..., (К - 1),

отличающийся тем, что, с целью повышения производительности, в каждой группе входов и в группе выходов введены дополнительные входы и выходы положительного и отрицательного окончания, а каждый сумматор цифр содержит дополнительно (К + 2)N - Кn элементов И, причем для каждого j-го сумматора цифр, где j = 0, ..., (N - 1), входы дополнительных элементов И соединены со всеми возможными сочетаниями входов положительного и отрицательного окончания между собой и с другими входами, (N + 1)-й вход каждого дополнительного элемента И соединен с управляющим входом сумматора цифр, если входы дополнительного элемента И соединены с входами сумматора цифр, отличными от входов положительного и отрицательного окончаний, то его первый выход соединен с l - m выходом последовательного сумматора, где  mi > m o d K, mi - номера входов, mi = 0, ..., (К - 1), второй выход элемента И соединен с входом j-го элемента задержки, если все входы элементы И соединены с входами положительного и отрицательного окончаний, при этом m входов соединены с входами отрицательного окончания (0 ≅ m ≅ N - 1) и q = m, то первый выход элемента И соединен с выходом положительного окончания последовательного сумматора, а второй выход - с входом m-го элемента задержки, если m входов элемента И соединены с входами отрицательного окончания (1 ≅ m ≅ N) и q = m - 1, то первый выход элемента И соединен с выходом отрицательного окончания последовательного сумматора, а второй выход - с входом (m - 1)-го элемента задержки, если m входов элемента И соединены с входами отрицательного окончания (0 ≅ m ≅ N) и q ≠ m и q ≠ m - 1, то первый выход элемента И соединен с (l - m)-м выходом последовательного сумматора, где

mi > m o d K, mi - номера входов, mi = 0, ..., (К - 1), второй выход элемента И соединен с входом j-го элемента задержки, если все входы элементы И соединены с входами положительного и отрицательного окончаний, при этом m входов соединены с входами отрицательного окончания (0 ≅ m ≅ N - 1) и q = m, то первый выход элемента И соединен с выходом положительного окончания последовательного сумматора, а второй выход - с входом m-го элемента задержки, если m входов элемента И соединены с входами отрицательного окончания (1 ≅ m ≅ N) и q = m - 1, то первый выход элемента И соединен с выходом отрицательного окончания последовательного сумматора, а второй выход - с входом (m - 1)-го элемента задержки, если m входов элемента И соединены с входами отрицательного окончания (0 ≅ m ≅ N) и q ≠ m и q ≠ m - 1, то первый выход элемента И соединен с (l - m)-м выходом последовательного сумматора, где

входы положительного и отрицательного окончаний имеют веса соответственно младшей и старшей цифр, а второй выход элемента И соединен с входом q-го элемента задержки, где  mi > m o d K.

mi > m o d K.

| Авторское свидетельство СССР N 1752097, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1996-02-27—Публикация

1989-12-04—Подача