1

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных системах, работающих в избыточной системе счисления.

Известно устройство для сложения чисел содержащее два функциональных регистра, два шифратора, сумматор и выходной регистр, в котором производится одновременное сложение нескольких чисел в избыточной системе счисления с последовательным поразрядным вводом операндов 1.

Однако устройство осуществляет слжение N чисел только в двоичной избыточной системе счисления.

Наиболее близким к предлагаемому является устройство для сложения N чисел в избыточной двоичной системе счисления, содержащее первый и второй т-разрядные двоичные сумматоры, соединенные с входными шинами соотвественно отрицательных и положительных значений слагаекых, два регистра задержки, входы которых подключены к выходам с первого по (т-1)-и разряды двоичных cyMM iTopoBr и последовательный сумматор в избыточной двоичной системе счисления, первый и второй выходы которого подключены к выходам старших т-х разрядов двоичных сумматоров, а третий и четвертый его входы соединены с выходами старших (m-l)-x разрядов регистров задержки, в которых производится последовательный поразрядный ввод одновременно N чисел 2 J.

Недостатком известного устройства является то, что оно работает толь0ко в двоичной избыточной системе счисления, т.е. при .

Цель изобретения - расширение функциональных- возможностей, заключающееся в возможности последовательно5го . поразрядного сложения N чисел в избыточной системе счисления с основанием .

Для достижения поставленной цели в устройство, содержащее, первый и

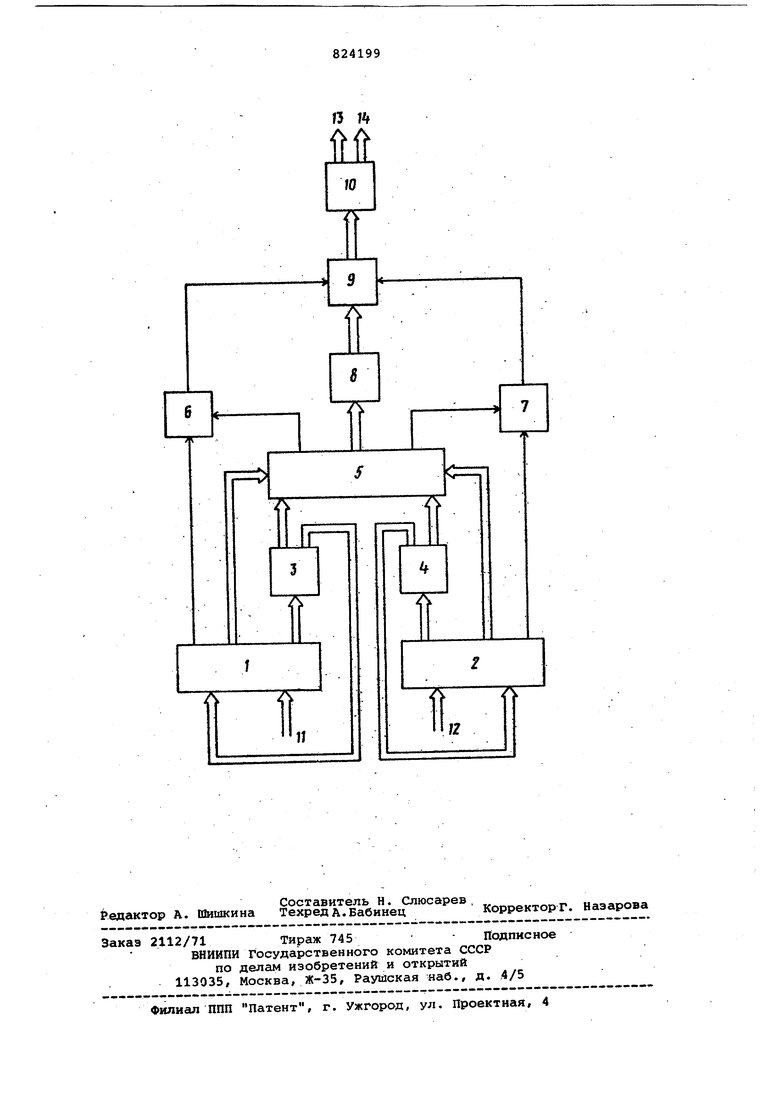

0 второй п-разрядные двоичные сумматоры lo.g2N(p-l),jN(p-l)+k, где m-2k, 3k...,Ь входы первых k разрядов которых подключены соответственно к Nk положительным и Nk отри5цательных входным шинам, операндов устройства/ первый и второй регистры задержки, подключенные к выходам (m-k) младших разрядов соответственно первого и второго двоичных сумма0торов, входы разрядов которых с (k+l)-ro по (m-k)-ft подключены к выходам (m-2k) младших разрядов соответственно первого и второго регистров задержки, и сумматор для избыточной системы счисления, введены дв элемента ИЛИ, третий регистр задержки, комбинационный суг-иматор и блок коммутации результата, причем выходы k старших разрядов первого двоичного сумматора и первого регистра задержки подключены к первой и второй группам положительных входов операндов сумматора для избыточной системы счисления, первая и вторая группы отрицательных входов которого соединены с выходами k старших разрядов второго двоичного сумматора и второго регистра задержки, выходы переноса первого и второго двоичных cyNMaTopoB соединены с первыми входами соответственно первого и второго элементов ИЛИ, вторыми входами соединенных с выходами соответственно положительного и отрицательного переносов сумматора в избыточной системе счисления; выходы суммы которого подключены к входам третьего регистра задержкиj подключенного выходом к первым входам разрядов комбинационного аумматора,.у которого второй вход первого разряда соединен с выходом первого элемента ИЛИ, вторые входы остальных разрядов соединены с выходом второго элемента ИЛИ, а выходы подключены к входам блока коммутации результата, соединенного с выходными положительными и отрицательными шинами результата. Кроме того, выход переноса ком бинационного сумь атора соединен с входом переноса его первого разряда. На чертеже приведена структурная схема устройства для сложения N чисел в избыточной системе счисления. Устройство содержит первый и второй двоичные сумматоры 1 и 2, первый и второй регистры 3 и 4 задержки, суМ матор 5 для избыточной системы счисления, элементы ИЛИ 6 и 7, третий ре гистр 8 задержки, комбинационный сум матор 9 и блок 10 коммутации результ та. Входы первых k разрядов первого и второго двоичных сумматоров 1 и 2 соединены с выходными Nk положительны ми 11 . и Nk отрицательными 12 шинами соответственно. Выходы (m-k) младших разрядов первого и второго двоичных сумматоров 1 и 2 соединены с вхо дами первого и второго регистров 3 и 4 задержки, выходы (т-2k) младших разрядов которых подключены к входам разрядов с (k+l)-ro по (m-k)-и соответственно первого и второго двоичных сумглаторов 1 и 2. Выходы k. старших разрядов первого двоичного сумматора 1 и первого регистра 3 задержки соединены с первой и второй группами положительных входов сумматора 5 для избыточной систе мы счисления, первая и вторая группа отрицательных входов которого подключены к выходам k старших разрядов второго двоичного сумматора 2 и второго регистра 4 задержки. Выходы переноса первого и второго двоичных сумматоров 1 и 2 соединены с первыми входами соответственно первого и второго элементов ИЛИ 6 и 7, вторые входы которых подключены к выходам соответственно положительного и отрицательного переносов су1 1матора 5 для избыточной системы счисления, выходы которого подключены к входам третьего регистра 8 задержки. Выходы третьего регистра 8 задержки .соединены с первыми входами разрядов комбинационного сумматора 9, у которого второй вход первого разряда соединен с выходом первого элемента ИЛИ б, вторые входь остальных разрядов подключены к выходу второго элемента ИЛИ 7, а выходы подключены к входам блока 10 коммутации результата, соединенного с выходными положительными 13 и отрицательными 14 шинами результата. Выход переноса комбинационного сумматора 9 соединен с входом его первого разряда. Устройство работает следующим образом. В каждом i-м такте работы на входы первых k разрядов первого и второго двоичных т-разрядных сумматоров 1 и 2 (log,,.,N(p-l)m 2k,3k, . . . , 1 ( р-1) 4-k ) по Nk поло;: ительным шинам 11 И- по Nk отрицательным шинам 12 подаются значения i-го разряда N суммируемых аргументов, начиная со старшего разряда, выраженные -цифрами Р-1, Р, , Т, 0,1. . . Р-2, Р-1. В двоичных сумматорах 1 и 2 образуются двоичные коды сумм соответственно положительных и отрицательных значений i-ro разряда N суммируемых аргументов, которые суммируются с двоичными кодами состояния, поступающими на входы разрядов с (k+l)-ro по (m-k)-й с выходов (т-2k) младших разрядов соответственно первого и второго регистров 3 и 4 задержки. На выходах первого и второго двоичных сумматоров 1 и 2 получают (ni+l)-e разрядные положительную S и отрицательную S суммы значений i-ro разряда суммируемых аргументов и значений кодов состояния предыдущего (i-l)-ro такта сложения. Знaчeния(m-k) младших разрядов сумм S и $7 с выходов разрядов с первого по {m-k)-й первого и второго двоичных сумматоров 1 и 2 подгиотся соответственно в первый и второй регистры 3 и 4 задержки, образуя коды состояния для следующего {i+l)-ro такта сложения. Значения разрядов суммы S с (m-k+l)-ro по m-й с выходов старших разрядов первого двоичного сумматора 1 подаются на первую группу положительных входов сумматора 5 для избыточной системы счислени образуя положительное значение перво го числа , отрицательное значение которого подается на первую группу отрицательных входов сумматора 5 с выходов k старшихразрядов второго двоичного сумматора 2, С выходов k старших разрядов первого регистра 3 задержки на вторую группу положитель ных входов сумматора 5 подается положительное значение второго числа Ь-, отрицательное значение которого подается на вторую группу отрицательны входов сумматора 5 с выходов k старших разрядов второго регистра 4 задержки. Сложение чисел и bv в сум маторе 5 производитсяв обратном коде, поэтому отрицательные значения чисел и преобразуются в обратный код. На выходах сумматора 5 получают значения переноса П и суммы С, - - по следум-чему алгоритму 1 при 1 при Oj О при р-1 а -1-Ь р-- + b,- -р при П q -V- Ъ -vp - при П « при П О Полученное значение сумглы С- в ви це (k+l)-ro разрядного числа в обрат ном коде подается в регистр 8 задерж ки, где задерживается на один такт сложения и подается на первые входы разрядов комбинационного сумматора 9 Значения переноса П с выходов положительного и отрицательного переносов сумматора 5 подаются на вторые входы соответственно первого и второ го элементов ИЛИ 6 и 7, на первые входы которых подаются зн ачения (т+1)-го разряда сумм и с выходов переноса соответственно первого и вт рого двоичных сумматоров 1 и 2. Ком Z3en ni LllIK ini.

а бинационный сумматор 9 суммирует задержанную регистром 8 сумму с значениями переносов с выходов элементов ИЛИ 6 и 7 в обратном коде и выдает результат Z в виде (k+1) разрядного числа, старший разряд которого является знаковым. Так как .Р-1 то получаемая JB комбинационном сумматоре 9 сумма р-1 . Положитель.ное значение переноса поступает на второй вход первого разряда комбинационного сумматора 9, а на вторые входы остальных его разрядов подается отрицательное значение переноса . В соответствии с правилами сложения чисел в обратном коде при Переполнении комбинационного сумматора 9 с выхода переноса на вход переноса его первого разряда подается единица В зависимости от знака суммы П. , блок 10 коммутации результате подает прямые значения k разрядов этой сумг«1Ы на положительные шины 13 результата (при jO) или инверсные значения k разрядов на отрицательные шины 14 результата (при П;, 0) . По выходным шинам 13 и 14 выводятся поразрядные значения результата Zy (где - число разрядов сдвига результата в сторону старших разрядов), начиная со старшего разряда. Для пояснения работы устройства в таблице приведен пример сложения трех чисел , и в избыточной системе счисления с основанием , т.е. при k 2, , , А 3231 В 3232 С 3302

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

| Устройство для сложения чисел в избыточной системе счисления | 1978 |

|

SU763896A1 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Устройство для сложения в избыточнойСиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824198A1 |

| Устройство для сложения в избыточной двоичной системе | 1977 |

|

SU717763A1 |

Результат сложения Z, ч-к доказывает работоспособность устройства.

Таким образом, путем введения в устройство двух элементов ИЛИ, регистра задержки, комбинационного сумматора и блока коммутации результата, получ(ена возможность поразрядного сложения N в избыточной системе

счисления с основанием . При этом ввод операндов и вывод результата старшими разрядами вперед осущёствляется одновременно, что увеличивает быстродействие примерно в п раз (п число разрядов суммируемых аргументов) по сравнению с суммированием аргументов младшими разрядами вперед. Для сложения N чисел с помощью послеяовательных сумматоров для сложения двух чисел в избыточной системе счис ления потребовалось бы не менее N-1 таких сумматоров, что сложнее пред- лагаемого устройства примерно в N/2 раза. Формула изобретения Устройство для сложения N чисел в избыточной системе счисления, содержащее первый и второй т-разрядные двоичные сумматоры DogiN(p-l) ,3k, . . , ,log3,N(p-l)+k3, входы первых k разрядов которых подключены соответственно к Nk положительным и Nk отрицательным входным шинам операндов устройства, первый и второй регистры задержки подключены к выходам (m-k) - младших разрядов соответственно первого и второго двоичных сумматоров, входы разрядов которых c(k+l)-ro по {m-k)подключены к выходам {m-2k) младших разрядов соответственно первого и второго регистров задержки, и сумматор в избыточной системе счисления отличающееся тем, что, с целью расширения функциональных возможностей, заключающегося в возмо ности последовательного поразрядного сложения N чисел в избыточной системе счисления с основанием Р. 2 в него введены два элемента ИЛИ, третий регистр задержки, комбинационный сумматор и блок коммутации результата, причем выходы k старших разрядов первого двоичного сумматора и первого регистра задержки подключены к первой и второй группам положительных входов операндов сумматора для избыточной системы счисления, первая и вторая группы отрицательных входов операндов которого соединены с выходами k старших разрядов второго двоичного сумматора и второго регистра задержки, выходы переноса первого и второго двоичных сумматоров соединены с первыми входами соответственно первого и второго элементов ИЛИ, вторыми входами соединенных с выходами соответственно положительного и отрицательного переносов сумматора в избыточной системе счисления, выходы суммы которого подключены к входам третьего регистра задержки, подключенного выходом к первым входам разрядов комбинационного сумматора, второй вход, первого разряда которого соединен с выходом первого элемента ИЛИ, вторые входы остальных разрядов соединены с выходом второго элемента ИЛИ, а выходы подключены ко входам блока коммутации результата, соединенного с выходНЕлми положительными и отрицательными шинами результата устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 634274, кл. G Об F 7/385, 1976. 2.Авторское свидетельство СССР по заявке 2665233/18-24, кл. G 06 F 7/385, 1978 (прототип).

Авторы

Даты

1981-04-23—Публикация

1979-07-04—Подача