1

Изобретение относится к области ш.1адслитепьной техншй и может быть испош aiOBaHo, нгшример, в качестве сумматора н арифметическо-яогическом устройстве, или в качестве преобразователя из одной системы счисления в другую в устройст, Bdx ввода и вывода шлфровых вычислительных машин. °.

Известные последовательные сумматорЬ1, предназначенные для cywsvrajwBara.MHсел, записанных в системах счисления отличных от двоичной, обычно состоят из одаого или двух двоичных сумматоров и схемы коррекции результатов, предназначенной для коррекции результата суммирования двоичных кодов чисеп l .

Известны также последоватепьно араллельные сумматорь для суммироваиая чисел, наприм, в десятично лвоя шрй системе счисления, состоящие из чегъфех рйзрйдного параллельного сумматора, в котором последовательно суммируются двоичные Тетрада: десятичных разрядов, вз схемы коррекции для образования десятичнбгчэ переноса и из схемы задержки для задержки на один такт переноса в старший разряд 2.

Суммирование чисел в тшсих сумматорах осуществляется младшими разрядами вперед для того, чтобы можно было в следующем- старшем разряде учесть, перенос . из младшего разряда.

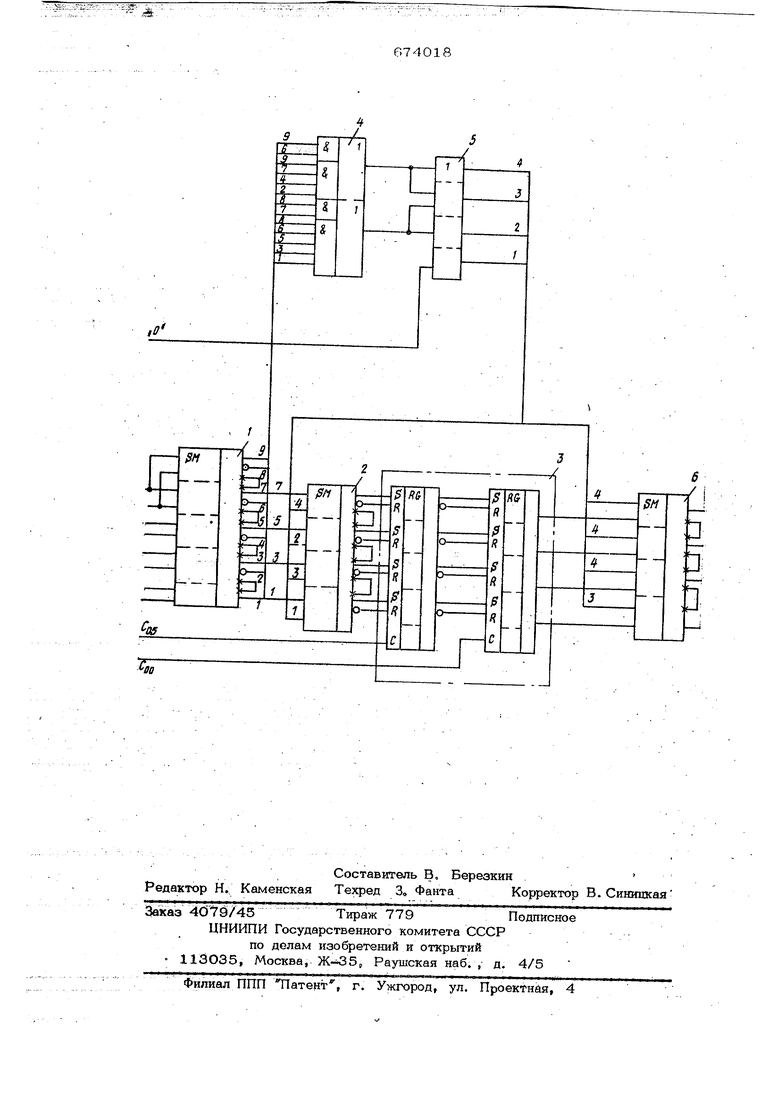

Такие сумматоры обладают сушественвым недостатком, заключающимся в том, что множительные устррйства последовательных арифметическо-логических устройсгв АЛУ, состоящие из таких сумматоров и регистров, имеют низкое быстродействие. Это происходит потому, что при умножении двух П -разрядных чисел произведение имеет 2 п. разрядов, из которых в П - разрядном АЛУ используется только п старших разря|яов. Но так как свыхода.множительного устройства произведение поступает младшими разрядами вперед, то первые гх разрядов не могут быть использованы в дальнейших вычислениях г-в результате чего в вычислениях о0разуется задержка по крайней мере на п тактов, чго существенно снижает быстродействие АЛ У. Наиболее близким к данному изобретению является устройство для суммировани содержашее первый и второй сумматоры, узел задержки, узел управления коррекцией, узел коррекции, выходы которого соединены с первой группой входов второго сумматора, а входы - с выходами узла управления коррекцией, входы которого Соединены с выходами первого сумматора выходы которого соединены также со второй группой входов второго сумматора з Недостаткок такого устройства также является низкое быстродействие, обусловленное тем, что суммирование производится начиная с младших разрядов. Целью изобретения является увеличение быстродействия. Для достижения этой цели предлагаемое.устройство содержит третий сумматор, первая группа входов которого соединена с выходами узла корре1тин, а вторая группа входов - с выходами узла задержки, входы которого соединены с выходам второго сумматора. Введение третьего сумматора и новое, неизвестное ранее соединение блоков между собой позволяет в предлагаемом сумматоре выполнять суммирование чисел начиная со старших разрядов. При этом цифрт. числа кодируются специальным образом. В обычных системах счисления с основанием R используеТЯ Т цифр от О до R - 1, например, в десятичной системе счисления используются цифры 0,1,2, ...9. При суммировании чисел, записанных в Tajfflx системах счисления, истинное знечение старших разрядов суммы может быть определено только после того, как определены значения всех предшеcTByraaHJt разрядов и определен перенос из младших разрядов в старшие. Возможность образования так называемого сквозного переноса ог самого мпадшего разряда к самому старшему не позволяет начинать суммирование от старших разрядов. Чтобы избавиться от сквозного переноса и получить возможность начинать суммирование старшими разрядами вперед можно выбрать тской способ кодирования иифр числа, чтобы при суммировании двух чисел мог возникнуть перенос не более, чем на один разряд. При суммировании чисел в обычных системах счисления перенос в ( + f )-й разряд возникает, ее-. ли сумма ( -ых разрядных коэффициентов слагаемых с учетом переноса из ({-()го разряда окажется большей или равной Р. Будем считать, что перенос в (f + 1)-й разряд возникает всякий раз, когда сумма 1 -ых разрядных коэффициентов Cf окажется не меньшей некоторого положительного числа. ) J , или не большей отрицательного числа . I С„ер2 I причем должно быть I nepZl T (2) с учетом Переноса в старший разряд и возможного переноса из младшего разряда величина i -го разрядного коэффициента суммы С,- может изменяться в пределахnepl-I C Cnepi-bl , если нет переноса В ( +1) разряд, , если есть положительный перенос в ( 4- +1) разряд, Cj6Cj,gp.,fR4i , если есть отрицательный перенос в (6 + 1) разряд. Чтобы при суммировании в { -м разряде переноса из ( - f) {эазряда не возник повторный перенос в ( f + l) разряд, необходимо выбирать из условия сЛ т (3) Если цифры, числа вьгбйраются из условий (l) - (з), то такиё системы счисления позволяют производить суммирование чисел, начиная со старших разрядов, причем перенос не может возникнуть более, чем на один разряд вперед. Проиллюстрируем это на десятичной системы счисления с 15-юциф- ,.,. .. рами (-7, -6, ..... 6,7, которые мы будем обозначать (7,6,5, ... 6,7). Эта система счисленияудовлетворяет условиям (l) - (з), если Спер -7 нам надо сложить два десятичных 0-686 Ь 314,: . которые в предлагаемой системе счисления имеют вид При суммировании чисел а + b в обыч ной десятичной системе счиспения в млад шем разряде возникает перенос при суммировании цифр 6 , который про ходит сквозь все разряоы, так как сумма разрядных коэффициентов в них равна 9 вплоть до четвертого разряда, так что , си1-ъ баб4314- юоо при суммировании же чисел си 4-b в предлагаемой системе счиспения, начиная со старших разрядов, мы получаем в третьем разряде сумму разрядных коэффициентов „ , которая больше, чем 7 , поэтому возникает перенос в четвертый разряд равный 1, а в третьем разряде разрядный коэффициент С J О . Этот коэффициент меньше, чем R, поэтому даже, если во втором разряде образуется перенос в третий разряд, он при суммировании с 3разрядным коэффициентом не даст повтор ный перенос в четвертый разряд. Поэтом после суммирования 3-х разрядных коэффициентов сразу же определяют истинное значение 4-го разрядного коэффициента. И вообще, после суммирования (- l)разрядиых коэффициентов становится из вестиым истинное значение -го разрядного коэффициента суммы. Так что, при последавательном суммировании чисел, записанных в системе счисления, удовлетворяющей условиям (1)(3), если суммирование начинается со .старших разрядов, задержка в выдаче старшего разряда составляет один такт, а не 2.П. тактов, как, например, в прототипе. На чертеже представлена функциональная схема сумматора. Устройство содержит первый сумматор 1, второй сумматор 2, узел задержки 3, состоящий из двух послед№ателгъно соединенных регистров, узел управления коррекции 4, узел коррекции 5, третий сумматор 6. Первый сумматор 1 является пятиразрядиым даоичным комбинационным сумматором. Он предназначен для получения двоичной кодированной суммы десятичных разрядных коэффициентов двух слагаемых. Так как в описанной выще десятичной системе счисления разрядные коэффициенты могут быть как положительными, так и отрицательными, то эти коэффициенты ко- дируются дополнительными двоичными кодами. Выходы первого матора 1 соединены со вторыми входами второго сумматора 2 и со входа ми узла утгравления коррекций 4.. Узел управления коррекцией 4 является комбинационной схемой И-ИЛИ и служит для вьфаботки двух управляющих сигналов для узла коррекций 5. Первый из этих сигналов является управляющим сигналом коррекции, когда сумма разряднь1х коэффициентов в сумматоре 1 больше или равна C,,gp| , т.е. при возникновении положительного переноса. Логическая формула этого управляющего сигнала имеет вид П -ОдДад уОдЛа ла ла ла , (4) где сигнал управления при положительном переносе, «.. сигналы на выходах 1-го, ... ., 5-го двоичных разрядов первого сумматора 1. Второй управляющий сигнал П образуется при возникновении отрицательного переноса в первом сумматоре 1, когда сумма разрядных коэффициентов члс.ла меньше или равна о2 Логическая формула feToro сигнала имеет вид a, (5) Выходы схемы управления коррекцией 4 соединены со входами узла коррекции 5. Узел коррекции 5 предназначен для образования сигнала положительного переноса (код ООО1) или отрицательного переноса (код 1111) в (J +)-й десятичый разряд по управляющим сигналам П или П I также для образования сигнала положительной или. отрицательной коррекции 1 -го десятичного разрядного коэффициента по управляющим сигналам коррекции. Узел коррекции 5 является комбинационной схемой И-И.Г1И, выполненной по логической формуле Ka(011Q)(iOfO)An П(0001)ЛТ1(1111)ЛП где К - сигнал коррекции, ОНО - двоичный ко.а числа б, корректирующего ( -и разрядный коэффициент при положительном переносе, 1О1О - двоичный код числа 10, корректирующего i -и разрядный коэффициент при отрицательном переносе, П - сигнал переноса в (i f 1 )-й разВыходы узла коррекции 5 соединены с первой группой входов второго сумматора 2 и с первой группой входов третьего сумматора 6.., .. ,ч Второй сумматор 2 предназначен для получения коррект1фованного значения i -го десятичного разрядного коэффици- ента. Он является четьфезфаэрядным двоичным комбйнахшонным сумматором. Выходы сумматора 2 соединены со входами узла задержки 3. Узел задержки 3 состоит из двух четырехразрядных регистров с синхронизацией тактирующими сериями импульсов С и Cgj , сдвинутыми на полтакта. Узел задержки 3 используется для задержки на один такт -го десятичного разрядного коэффициента суммы.; Выходы узла задер :разрядов, поступают одновременно своими i -MV. десятичными разрядами на входы первого сумматора синхронно с тактирующей серией импульсов CQO .Десятичные разрядные коэффициенты слагаемых кодируются следующими двоичными кодами. |КИ 3 соединены со второй группой входов третьего сумматора 6. Третий сумматор 6 является четьфехразрядным комбинационным сумматором и предназначен для суммирования положительной или отрицательной единицы переноса в (4+1) -и разряд суммы. Сумматор работает следующим образом, Суммируемые числа в каждом такте работы сумматора, начиная со старших

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования | 1977 |

|

SU734678A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Устройство для умножения чисел | 1991 |

|

SU1797112A1 |

| Устройство для умножения | 1985 |

|

SU1322265A1 |

| Устройство для сложения п-разрядныхдЕСяТичНыХ чиСЕл | 1979 |

|

SU824203A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Делительное устройство | 1984 |

|

SU1239711A1 |

Цифра Код 1001 101О 1011 11ОО

6

Цифра Код 0111 ОНО 0101 О100 ООН В первом сумматоре 1 разрядные коэффйШШнтБ суйЙйруютЬя j пи правилам сум ЙйрЬШйййГ двоичных чисел в дополнительных кодах. В отличие от второго 2 и третьего 6 сумматоров первый сумматор 1 является пятиразрядным. Пятый двоичный разряд необходим, чтобы не в6знйй;попёрёйблне иие разрядной сетки при суммировании t -их десятичных разрядов. 1 Во втором 2 и третьем 6 сумматорах переполнение произойти не мбжеТ, так как система счисления выфана из условий (1) - (3). Поэтому они четьфехразрядные. Двоичная сумма -ых разрядных коэффйШёнтов сшс ВБГходов первого сумматора 1 поступает на входы узла управления коррекцией 4 и на вторую группу вйкбдов второго сумматора 2. В уа лё утфйвления коррекцией 4 происходит анйШиэ суммы, полученной в первом сумматоре 1 по логическим формулам (4) и (5), выдавай управляющие сигналы П и П на входы узла коррекции 5, где из низ формируются сигналы переноса и коррекции.

О 1101 1110 1111 0000 0010 0001 При этйй, если сумма в первом сумматоре окажется больше или равна 7, то из полученной суммы i -ых разрядных коэффициентов необходимо вычесть десять или (чгго для дополнительных двоичных кодов то же самое) прибавить число 6 (двоичный код ОНО), а к ( -4-1)-Му р аЗрядному коэффициенту надо прибавить + 1(код 0001). Если же сумма Л -ых разрядных коэффициентов окажется меньше или равна минус 7, то к полученной сумме необходймо прибавить десять (код 1010), а из ( J +1)-го разрядного коэффициента вычесть 1 (прибавить дополнительный код 1111). Суммирование числа 10 или 6 с суммой 1 -ых разрядных коэффициентов про изводцтся во втором .сумматоре 2. Двоичныё коды чцсел 10 и 6 вьфабатьгоаются в узле коррекши 5 из управляющих сигналов П и П . Скорректированная таким образом сумма ,} -ых: разрядных коэффициентов по тактирующей серии импульсов , которая подается через полтакта после серии С t записывается в первый регистр ск&лы задержки. (Величина такта выб1фается такой, чтобы переходные процессы в комби национных сумматорах 1 и 2, а также в узлах 4 и 5 закончились меньше, чей за полтакта). Еще через полтакта эта сумма по серии импульсов Ср переписьгоается во второй регистр узла задержки 3. Таким образом осуществляется задержка i -го разрядного коэффициента суммы на один такт. Задержка производится для того, чтобы в следующем такте прибавить или вычесть из i -го разрядного коэффициента единицу, еспи при I суммировании ( J -1)-х разрядных коэффициентов в первом сумматоре 1 узел управления коррекцией 4 вьщает управляющийсигнал (Т или П . Суммирование происходит в третьем сумматоре 6, о&разуя истинное значение i -го разрядного коэффициента суммы двух слагаемых, . Таким образом происходит последовательное суммирование всех десятичных разрядов слагаемых, . начиная со старших разрядов. Общая задержка информации в сумматоре - один такт. Устройство может быть использовано не только для суммирования чисел, но и для преобразования чисел в предлагаемую систему счисления из обычной двоично-десятичной системы счисле шя с цифрами : О, 1, 9. Для чего п еводимое число, начиная со старших разрядов,, сво ими тетрадами, подается на первые входы четьфех младших разрядов первого сумматора 1, а на Первый вход пятого разряда подается знаковый разряд числа. Навторой вход всех разрядов первого сумматора подается нуль. Далее устройство, работает по описанному выше алгоритму, образуяна выходе преобразованное число. Устройство имеет кроме того еще и следующее достоинство. Оно без сушест бенных изменений может использоваться не только для суммирования десятичных чисел, но и чисел в системах счисления от 8- рй до . Требуется гапиь несушес-гвенно изменить со единение входов .узла коррекции 5 с выходами узла управления коррекцией 4, . так, чтобы на Tei выходы узла коррекции 5, которые соеди-: нены с первой группой входов второго сум матора 2, поступили не числа 10 или 6, а число, равное основанто выбранной системы счисления или его дополнение ло 16. Использование предложенного устройств ва для суммирования в множительном устройстве последовательно-параллельного арифметическо -логического устройства по; воляет увеличить его быстродействие в два раза, так как суммирование частичных произведений двух л-разрядных чисел происходит, начиная со старших разрядов, что позволяет использовать старший разряд произведения с задержкой на один такт. Для получения всех л -старших разрядов произведения в таком . жительном устройстве требуется такт его работы. В то же время в Поспеловательно-параллельном множительном устройстве, использующем сумматоры, суммирование в которых осуществляется, начиная с младших разрядов, для получения П старших разрядов произведения, требуется--по крайней мере 2п тактов. Так что предложенное устройство позволяет увеличить быстродействие в Формул а изобретения . - ( Устройство для суммирования, содер жащеё Первый и второй сумматоры, узел задер аш, узел управлений коррекцией, узел кор.екции:, выходы которого соединены с первой группой входов вторюго сумматора, а входы - с выходами узла управления коррекцией, входы которого соединены с .вьтходами первого сумматора, выходы которого соединены также со второй группой входов второго cyMMaTopia, о f л и ч а ю Щ е е с я тем, что, .с целью увеличения быс.тродействия, устройство содержит третий сумматор, первая группа входов которого соединена с выходами узла коррекции, а вторая группа входовс выходами узла задержки, входы которого соединены с выходами второго сумматора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 457084, кл. Q 06 F 7/385, 1972 2. Шигин А. Г. Цифровые вычислительные машины, М. , Энергия, 1971, с. 232-234. 3. Авторское свидетельство СССР № 387364, кл. Q 06 F 7/50, 1971.

Авторы

Даты

1979-07-15—Публикация

1976-12-07—Подача