Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых вычислительных системах, например, в системах внутриреакторного контроля, системах управления ядерным реактором, а также в системах, осуществляющих контроль радиационной обстановки окружающей среды.

Целью предлагаемого изобретения является упрощение устройства при анализе многоразрядных чисел, за счет сокращения одной схемы сравнения и одного регистра.

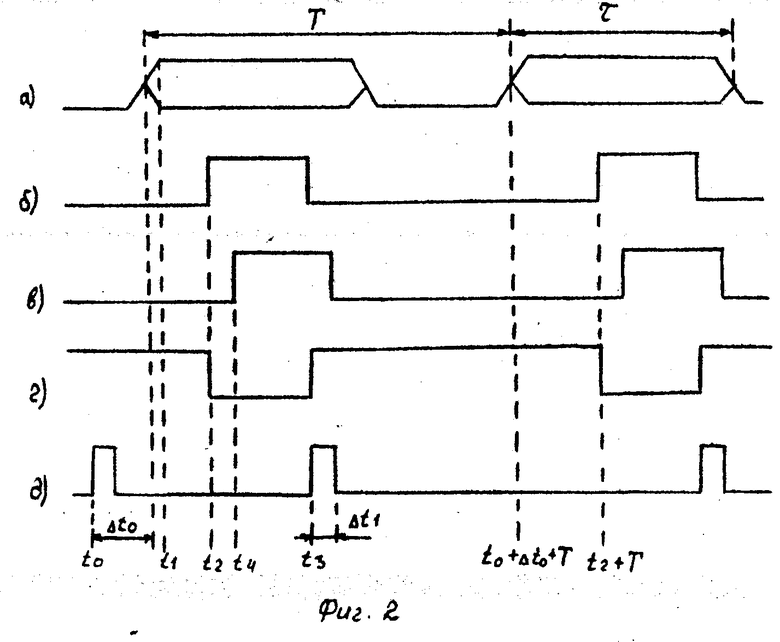

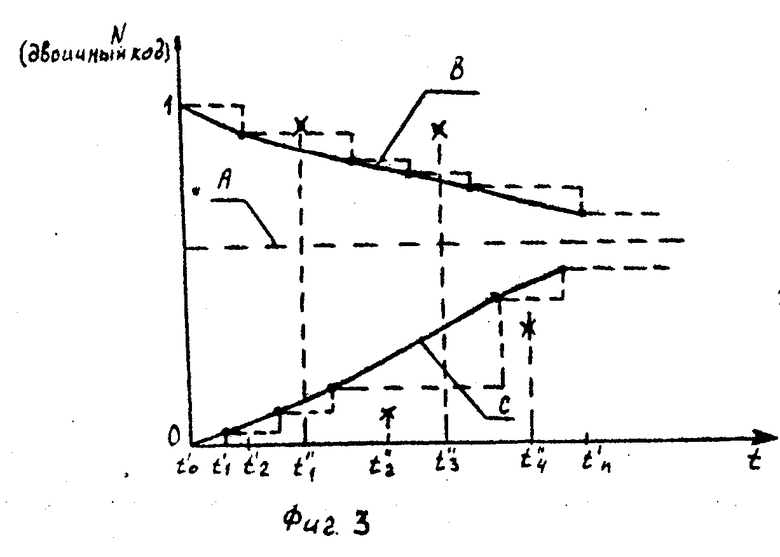

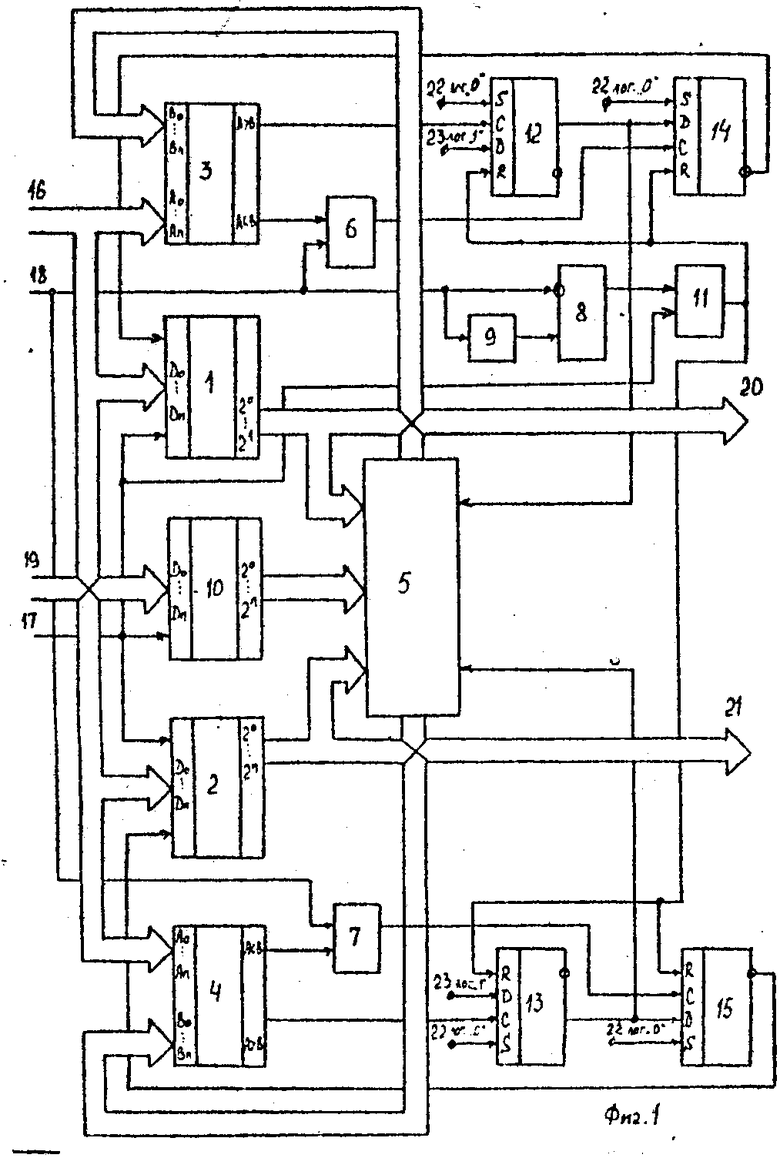

На фиг. 1 приведена структурная схема устройства для поиска числа, ближайшего к заданному; на фиг. 2 - временные диаграммы работы устройства; на фиг. 3 - график нахождения экстремальных чисел, где кривая приближения к большему значению (В) относительно зталонного значения (А); кривая приближения к меньшему значению (С) относительно эталонного значения (А); пунктиром обозначена кусочно-линейная аппроксимация данных кривых; на фиг. 4 - вариант построения коммутатора 5.

Устройство для поиска числа, ближайшего к заданному, содержит регистр 1 большего значения, регистр 2 меньшего значения, схемы сравнения 3,4; коммутатор 5, элементы И 6...8, элемент задержки 9, регистр 10 заданного числа, элемент ИЛИ 11, триггеры 12, 13 проверки эталона, триггеры 14, 15 проверки текущего значения, входы 16 анализируемого числа устройства, вход 17 управления записью устройства, вход 18 тактовых импульсов устройства, входы 19 заданного числа устройства, выход 20 ближайшего большего устройства, выход 21 ближайшего меньшего устройства, вход 22 логической единицы устройства.

В устройстве для поиска числа, ближайшего к заданному, входы 16, анализируемого числа устройства, соединены с информационными входами Do...Dn регистра 1 большего значения, с входами Ао...Аn первой группы первой схемы сравнения 3, с информационными входами Do...Dn регистра 2 меньшего значения и с входами Ао...An первой группы второй схемы сравнения 4. Выходы 2о...2n регистра 1 большего значения и регистра 2 меньшего значения сведены соответственно с информационными входами первой и второй групп коммутатора 5, первая и вторая группы выходов которого подключены соответственно к входам Во. . . Вn второй группы первой схемы сравнения 3 и входам Во...Вn второй группы второй схемы сравнения 4. А вход 17 управления записью устройства подключен к первым входам управления записью регистров 1,2 большего и меньшего значения. Вход 18 тактовых импульсов устройства соединен с первыми входами первого и второго элементов И 6, 7 и входом элемента задержки 9. Вторые входы первого и второго элементов И 6,7 соединены соответственно с выходами меньше (А < В) первой и второй схем сравнения 3,4. Синхровход С первого триггера 12 проверки эталона соединен с выходом больше (А > В) первой схемы сравнения 3. Прямой выход первого триггера 12 проверки эталона соединен с информационным D входом первого триггера 14 проверки текущего значения и первым управляющим входом коммутатора 5. Синхровход С первого триггера 14 проверки текущего значения подключен к выходу первого элемента И 6, а инверсный выход ко второму входу управления записью регистра 1 большего значения. Вход 18 тактовых импульсов устройства подключен к инверсному входу третьего элемента И 8, прямой вход которого соединен с выходом элемента задержки 9. Выход третьего элемента И 8 соединен со вторым входом элемента ИЛИ 11, первый вход которого соединен с входом 17 управления записью устройства и входом управления записью регистра 10 заданного числа, информационные входы Do...Dn которого являются входами 19 заданного числа устройства. Выходы 2о. ..2n регистра 10 заданного числа подключены к информационным входам третьей группы коммутатора 5. Выход элемента ИЛИ 11 соединен с входами R установки в ноль первого 12 и второго 13 триггеров проверки эталона и первого 14 и второго 15 триггеров проверки текущего значения. Синхровход С второго триггера 13 проверки эталона соединен с выходом больше (А > В) второй схемы сравнения 4. Прямой выход второго триггера 13 проверки эталона соединен с информационным D входом второго триггера 15 проверки текущего значения и со вторым управляющим входом коммутатора 5. Синхровход С второго триггера 15 проверки текущего значения подключен к выходу второго элемента И 7, а инверсный выход - ко второму входу управления записью регистра 2 меньшего значения. Выходы 2о...2n регистров 1,2 большего и меньшего значений являются соответственно выходами 20,21 ближайшего большего и ближайшего меньшего устройства, входы 22 логической единицы устройства соединены с информационными D входами триггеров 12, 13 проверки эталона.

Устройство работает следующим образом.

На вход 17 управления записью с внешнего устройства в момент времени to (фиг. 2д) поступает импульс начальной установки, который по информационным входам Do. . . Dn регистра 10 заданного числа записывает в него заданное число, поступающее на входы 19 заданного числа устройства. Тот же импульс устанавливает в единичное состояние регистр 1 большего значения и в нулевое состояние регистр 2 меньшего значения и через первый вход схемы ИЛИ 11 триггеры 12,13 проверки эталона и триггеры 14, 15 проверки текущего значения. При этом триггер 12 проверки эталона по первому управляющему входу коммутатора 5 управляет работой коммутатора таким образом, что он подключает выходы 2о. . .2n регистра 10 заданного числа к входам Во...Вn первой схемы сравнения 3, а триггер 13 проверки эталона по второму управляющему входу коммутатора 5 управляет работой коммутатора таким образом, что он подключает выходы 2о. . .2n регистра 2 меньшего значения к входам Во...Вn схемы сравнения 4.

Затем через время Δ to на входы 16 анализируемого числа устройства периодически, с периодом (Т) тактовых импульсов (вход 18), поступает последовательность анализируемых чисел (фиг. 2а).

Если первое поступающее на входы 16 (входы Ао...Аn схемы сравнения 3) число (момент времени t6+ Δ to, фиг.2 а) больше эталонного, то положительный фронт импульса с выхода "больше" (А > В) схемы сравнения 3 устанавливает в единичное состояние триггер 12 проверки эталона. Данный триггер переключает коммутатор 5 из режима подключения входов Во...Вn схемы сравнения 3 к выходам 2о...2n регистра 10 заданного числа в режим подключения этих входов к выходам 2о...2n регистра 1 большего значения. При значении числа, хранящегося в регистре 1 большего значения, больше числа, поступающего на входы 16 анализируемого числа устройства, на выходе "меньше" (А < В) в момент времени t1 устанавливается единичный потенциал, который через элемент И 6 по синхровходу триггера 14 проверки текущего значения в момент времени t2 (фиг. 2) устанавливает данный триггер в единичное состояние, с инверсного выхода которого на второй вход управления записью регистра 1 больше значения поступает нулевой потенциал. В момент времени t3 (фиг. 2д) импульс сброса, формируемый элементом задержки 9 и элементом И8 из тактового импульса (фиг. 2б), поступающего по входу 18 тактовых импульсов устройства в течение времени t3+Δ t1, через схему ИЛИ 11, устанавливает в нулевые состояния триггер 12 проверки эталона и триггер 14 проверки текущего значения. При этом начало момента установки в нулевые состояния триггеров 12, 14 определяется моментом начала действия импульса сброса, т.е. моментом времени t3. В момент времени t3 (фиг. 2д) фронт положительного импульса, поступающий с инверсного выхода триггера 14 проверки текущего значения на второй вход регистра 1 большего значения, записывает в данный регистр новое значение числа, поступившего на входы 16 анализируемого числа устройства. Затем через период Т (фиг. 2) на входы 16 анализируемого числа устройства в момент времени to+ Δto+ T приходит новое значение информации, сопровождаемое тактовым импульсом, поступающим в момент времени t2+T (фиг. 2б) по входу 18 тактовых импульсов устройства, и в случае удовлетворения условия, что данное значение больше заданного, хранящегося в регистре 10 заданного числа и меньше значения, хранящегося в регистре 1 большего значения, цикл повторяется, и в регистр 1 записывается новое значение информации, которое стоит к заданному ближе, чем предыдущее.

Если значение числа, приходящего на входы 16 анализируемого числа устройства, меньше заданного, то триггер 12 проверки эталона в единичное состояние не установится, следовательно, не установится в единичное состояние и триггер 14 проверки текущего значения, и число, пришедшее на входы 16 анализируемого числа устройства, не запишется в регистр 1 большего значения, т. к. потенциал на инверсном выходе триггера 14 остается неизменным (единичным) на время τ -поступления новой информации (фиг. 2а).

Если значение числа, приходящего на входы 16 анализируемого числа устройства, больше заданного и больше числа, хранящегося в регистре 1 большего значения, то новое значение также не запишется в данный регистр, т.к. на выходе меньше (А<В) схемы сравнения 3 единичный потенциал не формируется. Следовательно на синхровход триггера 14 проверки текущего значения данный потенциал не поступит, и триггер не изменит своего нулевого состояния.

Если первое, поступающее на входы 16 анализируемого числа устройства (входы Ао. ..Аn схемы сравнения 4), число (момент времени to+Δ to фиг. 2а) больше значения, хранящегося в регистре 2 меньшего значения, то положительный фронт импульса с выхода "больше" (А>В) схемы сравнения 4 установит в единичное состояние триггер 13 проверки эталона. Данный триггер переключит коммутатор 5 из режима подключения входов Во...Вn схемы сравнения 4 к выходам 2о. ..2n регистра 2 меньшего значения в режим подключения этих входов к выходам 2о...2n регистра 10 заданного числа. При значении заданного числа, хранящегося в регистре 10, больше числа, поступающего на входы 16 устройства, на выходе "меньше" (А<В) схемы сравнения 4 в момент времени t1 установится единичный потенциал, который через элемент И 7 по синхровходу триггера 15 проверки текущего значения в момент времени t2 (фиг. 2) установит данный триггер в единичное состояние, с инверсного выхода которого на второй вход управления записью регистра 2 меньшего значения поступит нулевой потенциал. В момент времени t3 (фиг. 2д) импульс сброса, формируемый элементом задержки 9 и элементом И8 из тактового импульса (фиг. 2б), поступающего по входу 18 тактовых импульсов устройства в течение времени t3 + Δ t1 через схему ИЛИ 11, установит в нулевое состояние триггер 13 проверки эталона и триггер 15 проверки текущего значения. При этом начало момента установки в нулевые состояния триггеров 13, 15 определяется моментом начала действия импульса сброса, т.е. моментом времени t3. В момент времени t3 (фиг. 2д) фронт положительного импульса, поступивший с инверсного выхода триггера 15 проверки текущего значения на второй вход управления записью регистра 2 меньшего значения, записывает в данный регистр новое значение числа, поступившего на входы 16 анализируемого числа устройства. Затем через период Т (фиг. 2) на входы 16 устройства в момент времени to+ Δto+ T приходит новое значение информации, сопровождаемое тактовым импульсом, поступающим в момент времени t2+T (фиг. 2б) по входу 18 тактовых импульсов устройства, и в случае удовлетворения условия, что данное значение больше значения, хранящегося в регистре 2 меньшего значения, и меньше значения заданного числа, хранящегося в регистре 10, цикл повторяется, и в регистр 2 запишется новое значение информации, которое стоит к заданному ближе, чем предыдущее. Если значение числа, пришедшего на входы 16, меньше значения числа, хранящегося в регистре 2 меньшего значения, то триггер 13 проверки эталона в единичное состояние не установится, следовательно, не установится в единичное состояние и триггер 15 проверки текущего значения, и число, пришедшее на входы 16 устройства, не запишется в регистр 2 меньшего значения, т. к. потенциал на инверсном выходе триггера 15 остается неизвестным (единичным) на время τ -поступления новой информации (фиг. 2а). Если значение числа, пришедшего на входы 16 устройства, больше значения числа, хранящегося в регистре 2 меньшего значения и больше заданного, то новое значение также не запишется в регистр 2 меньшего значения, т.е. на выходе "меньше" (А<В) схемы сравнения 4 единичный потенциал не формируется. Следовательно, на синхровход триггера 15 проверки текущего значения данный потенциал не поступит, и триггер не изменит своего нулевого состояния.

Импульс начальной установки триггеров 12, 13 проверки эталона и триггеров 14, 15 проверки текущего значения формируется в моменты времени t3+ Δ t1+Tn, где n - целое число, характеризующее последовательность чисел (фиг. 2), элементом задержки 9 и элементом И 8 при каждой смене чисел, поступающих на входы 16 анализируемого числа устройства независимо от их значения по сравнению со значениями, хранящимися в регистре 10 заданного числа и регистрах 1, 2 большего и меньшего значений. Таким образом, если триггеры 12, 13 проверки эталона установятся в единичное состояние, а триггеры 14, 15 проверки текущего значения нет, то к началу прихода нового, из последовательности чисел, числа, все триггеры будут находиться в нулевом состоянии и цикл отбора экстремальных чисел повторится.

Импульс начальной установки (фиг.2д) формируется в соответствии с временной диаграммой (фиг. 2), при этом информация (фиг. 2а) на время (t3-t2) длительности каждого тактового импульса не изменяет своего числового значения. Тактовые импульсы, поступающие на инверсный вход элемента И 8, инвертируются (фиг. 2г), а задержанный тактовый импульс (фиг. 2в) в момент времени 14 поступает на прямой вход элемента И 8 с выхода элемента задержки 9.

Элементы И 6, 7 необходимы для разделения переключения режима "больше" на режим "меньше" схем сравнения 3, 4 относительно начала прихода нового, из последовательности чисел числа, (фиг. 2а, моменты времени to+ Δto+Tn) по сравнению с передним фронтом тактового импульса (фиг. 2б, момент времени t2).

Таким образом, каждое новое число, пришедшее на входы 16 анализируемого числа устройства, находит свое значение с помощью триггеров проверки эталона и триггеров проверки текущего значения, количество которых не зависит от разрядности сравниваемых чисел. В прототипе же для той же цели используется дополнительная схема сравнения 9 и, при анализе последовательностей чисел в параллельном двоичном коде, дополнительный регистр 1, количество элементов , на которых построены данные схема сравнения и регистр, значительно увеличивается при увеличении разрядности сравниваемых чисел.

Ближайшее большее (меньшее) значение хранится в регистре 1(2) большего (меньшего) значения и выдается данным устройством на выход 20 (21) ближайшего большего (меньшего) устройства. Значения чисел на выходе 20 (21) характеризуется в каждый момент времени, соответствующим значением на кривой В(С) (фиг. 3).

Запись заданного значения в регистр заданного числа и установка в максимальное (минимальное) состояние регистра 1(2) большего (меньшего) значения производится в момент времени t'o. Затем в моменты времени t' 1, t' 2...t' n, кратные пеpиоду тактовых импульсов, в регистр большего (меньшего) значения производится перезапись нового значения в случае удовлетворения условия, что текущее значение больше (меньше) заданного и меньше (больше) значения, записанного в регистр большего (меньшего) значения. Если новое текущее значение не удовлетворяет этим условиям, то его значение не запишется в данный регистр (моменты времени t''1 , t''2 , t''3 , t''4 , (фиг. 3)).

Положительный эффект в предлагаемом устройстве достигается за счет управления выходными потенциалами схем сравнения четырьмя триггерами, которые синхронизируют работу регистров большего, меньшего значений и коммутатора. Данное решение позволило упростить устройство при анализе многоразрядных чисел за счет сокращения схемы сравнения и регистра, количество элементов на которых они построены значительно увеличиваются при увеличении разрядности сравниваемых чисел. Расчет показал, что при анализе шестнадцатиразрядных чисел, выигрыш составил две микросхемы четырехразрядных цифровых компараторов типа 564ИП2, и четыре четырехразрядных регистра типа 564ИР9.

В устройстве-прототипе необходим анализ, последовательно записываемых в 1 регистр чисел с числом хранящимся в четвертом регистре (заданного) числа. Данный анализ осуществляется с помощью дополнительной схемы сравнения 9.

В предлагаемом устройстве отпадает необходимость такого анализа за счет синхронизации, двумя триггерами проверки эталона и двумя триггерами проверки текущего значения, работы регистров большего и меньшего значений с работой коммутатора. Данное решение позволило значительно упростить устройство-прототип и следовательно повысить его надежность за счет исключения, присутствующих в нем дополнительных схемы сравнения и регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения кодов | 1990 |

|

SU1758643A1 |

| СПОСОБ РЕГУЛИРОВАНИЯ ЖИДКОСТНОГО РАКЕТНОГО ДВИГАТЕЛЯ И УСТРОЙСТВА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2085755C1 |

| Устройство для контроля вычислительных программ | 1985 |

|

SU1278856A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Генератор случайного процесса | 1982 |

|

SU1087991A1 |

| Устройство декодирования тональных сигналов | 1988 |

|

SU1570034A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Цифровой измеритель несимметричности сигналов | 1990 |

|

SU1725179A1 |

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

| Генератор случайных чисел | 1981 |

|

SU980093A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых вычислительных системах, например в системах, осуществляющих контроль радиационной обстановки окружающей среды. Цель изобретения - упрощение устройства при анализе многоразрядных чисел. Устройство содержит регистры 1 и 2 большего и меньшего значений, схемы сравнения 3, 4, коммутатор 5, регистр заданного числа 10, триггеры 12, 13, 14, 15. 4 ил.

УСТРОЙСТВО ДЛЯ ПОИСКА ЧИСЛА, БЛИЖАЙШЕГО К ЗАДАННОМУ, содержащее регистры большего и меньшего значений, регистр заданного числа, две схемы сравнения, два элемента И, элемент задержки, причем входы анализируемого числа устройства соединены с информационными входами регистров большего и меньшего значений и входами первых групп первой и второй схем сравнения, входы вторых групп которых соединены с первой и второй группами выходов коммутатора соответственно, вход тактовых импульсов устройства соединен с входом элемента задержки и первыми входами первого и второго элементов И, вторые входы которых соединены с выходами "Меньше" соответствующих схем сравнения, выходы регистров большего и меньшего значений являются выходами соответственно ближайшего большего и ближайшего меньшего устройства, информационные входы регистра заданного числа являются входами заданного числа устройства, отличающееся тем, что, с целью упрощения устройства при анализе многоразрядных чисел, оно содержит третий элемент И, элемент ИЛИ, два триггера проверки эталона и два триггера проверки текущего значения, причем выходы "Больше" первой и второй схем сравнения соединены с сихровходами соответственно первого и второго триггеров проверки эталона, информационные входы которых соединены с входом логической единицы устройства, а приемные выходы соединены с информационными входами соответственно первого и второго триггеров проверки текущего значения и первым и вторым управляющими входами коммутатора, информационные входы первой, второй и третьей групп которого соединены с выходами регистров соответственно большего и меньшего значений и заданного числа, входы управления записью которых подключены к входу управления зиписью устройства и первому входу элемента ИЛИ, выход которого подключен к входам установки в ноль всех триггеров проверки эталона и текущего значения, а второй вход соединен с выходом третьего элемента И, инверсный и прямой входы которого соединены соответственно с входом и выходом элемента задержки, выходы первого и второго элементов И соединены с синхровходами соответственно первого и второго триггеров проверки текущего значения, инверсные выходы которых подключены к вторым входам управления записью регистров большего и меньшего значений.

| Устройство для определения чисел,ближайших к заданному | 1981 |

|

SU997029A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-03-27—Публикация

1990-09-21—Подача