вания 35. выход 36 адреса, выход 37 поля адреса контрольной точки, выход 36 поля текущего адреса, выход поля логического условия 39, выход поля начального адреса 40, выход метки 41, выход поля начального адреса 42 и выход метки 43.

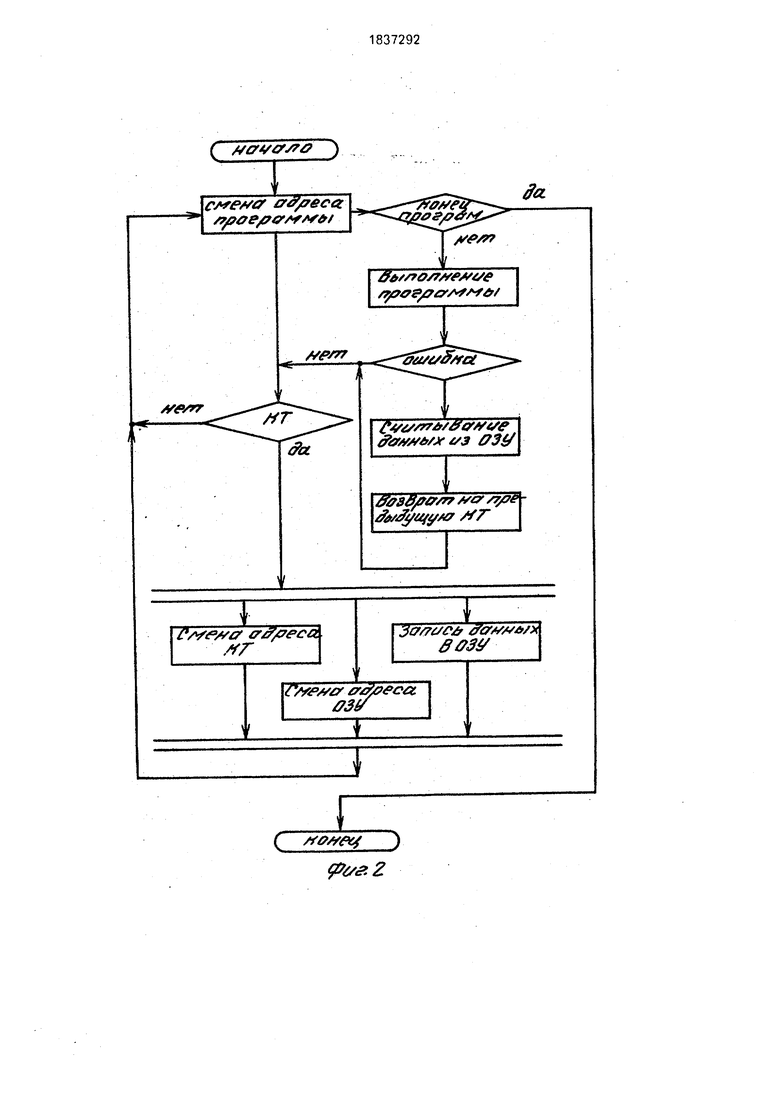

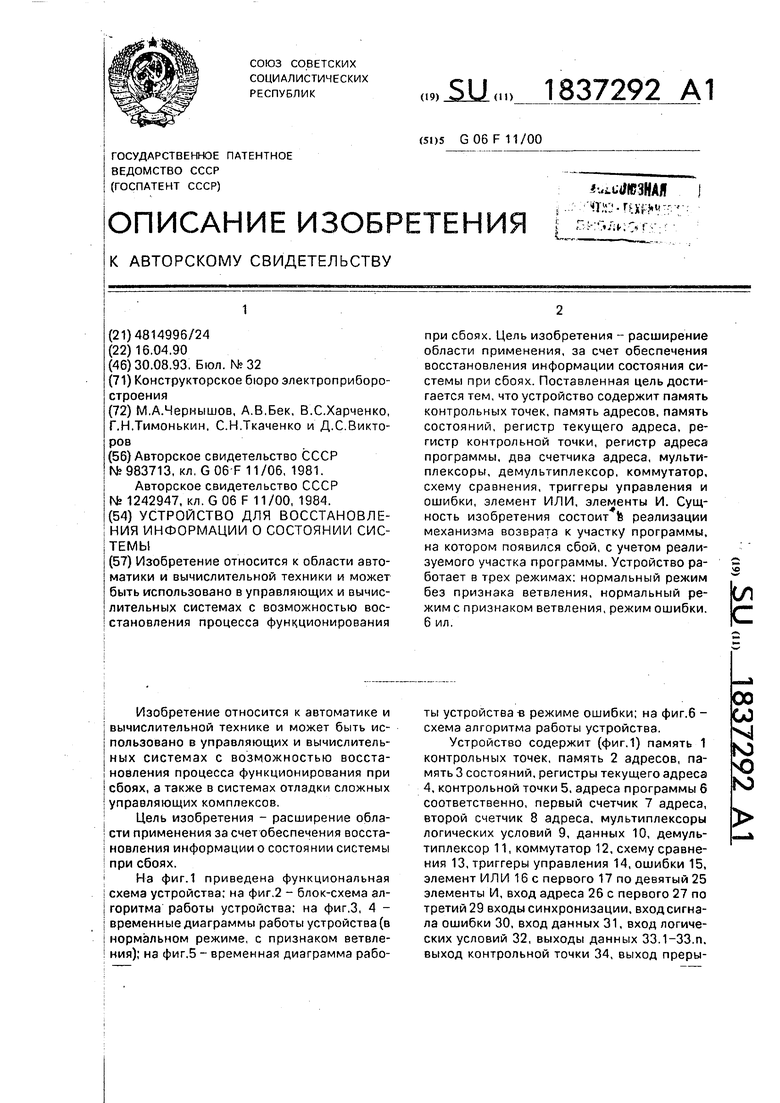

Принцип действия устройства состоит в следующем (см. фиг.6). При отсутствии сигнала от системы об ошибке устройство избирательно записывает данные от источников системы в ячейки памяти 3. Если система выдает в устройство сигнал о наличии ошибки, то на линейном участке программы устройство считывает данные из памяти 3 и осуществляет возврат на пред- идущую контрольную точку (КТ). На участке программы, где необходимо ветвление системы осуществляет возврат на предыдущую КТ с помощью регистра адреса программы. В процессе работы память 1 выдает адреса, которые используются для извлечения из памяти 2 адреса ячейки памяти 3, в которых необходимо сменить информацию.

Перед началом работы устройство находится в исходном состоянии. Начальное со- стояние характеризуется следующим: регистры 4-6 и счетчики 7-8 обнулены, триггеры 14-15 находятся в нулевом состоянии, на выходе 37 - адрес первой КТ, на выходе 38 - адрес второй КТ, на выходе 39 - теку- щее логическое состояние, на выходе 40 - начальный адрес, все остальные выходы в нулевом состоянии (цепи установки исходного состояния на фиг.1 условно не показаны).

Устройство работает в трех режимах: нормальный режим, без признака ветвления, нормальный режим с признаком ветвления, режим ошибки.

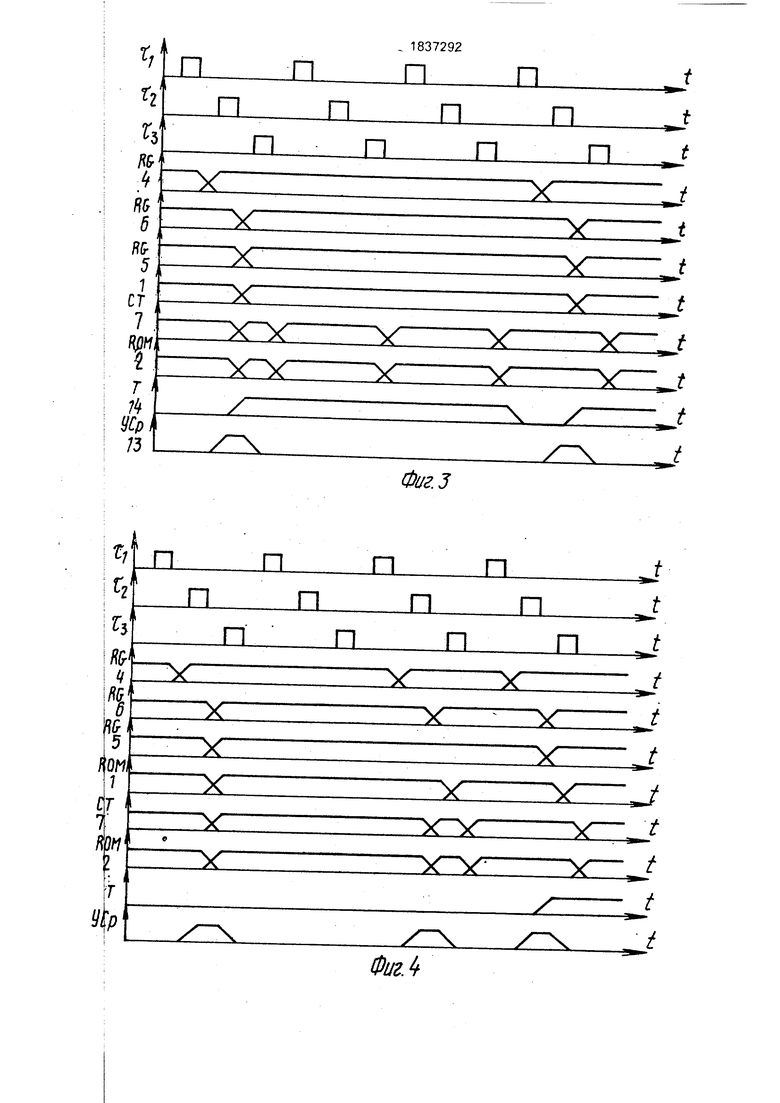

Нормальный режим без признака ветв- ления (см, фиг.1, 2, 3). Адрес первой КТ поступает на регистр текущего адреса 4 и записывает в него текущий адрес. При совпадении этого адреса с адресом, находящимся на выходе 37 памяти 1, схема сравнения установится в единичное состояние. Тем самым откроются элементы И 18- 20 и разрешат прохождение тактовых импульсов с входа синхронизации 28 на входы синхронизации счетчика адреса 7, реги- стра 5 и регистра адреса программы б.

Одновременно в регистр адреса программы 6 записывается текущий адрес из регистра текущего адреса 4, в регистр 5 за- писывается адрес следующей КТ с выхода текущего адреса 38 памяти 1 триггер управления 14 через элементы И 20 и ИЛИ 16 тактовых импульсов устанавливается в единичное состояние, в счетчик адреса 7 с

выхода начального адреса 40 памяти 1 записывается начальный адрес текущей КТ.

При записи в регистр 5 адреса следующей КТ с выхода текущего адреса 38 памяти 1, на всех ее выходах устанавливаются все атрибуты, характерные для КТ, записанной по адресу, хранящемуся в регистре 5. После установки триггера управления 14 в единичное состояние открывается элемент И 21 и И 23, разрешая прохождение тактовых импульсов с входа синхронизации 29 на счетный вход счетчика адреса 7 (тем самым модифицируется начальный адрес) и на вход записи памяти 3. С выхода 34 в систему поступает информация о начале считывания адресов ячеек памяти для данной КТ. Адреса, записываемые в счетчик, вызывают из памяти 2 адреса ячеек памяти 3, в которых необходимо сменить информацию, и эти адреса подаются на адресный вход мультиплексора данных 10, тем самым подключая необходимые источники данных на вход памяти 3, а также через коммутатор 12 на адресный вход памяти 3. В памяти 3 записываются данные. Считывание команд из памяти адресов 2 производится до тех пор, пока не будет считана последняя команда для данной КТ, в поле которой находится метка. Метка с выхода 43 памяти адресов 2 закрывает элемент И 21 и открывает элемент И 22. Открытый элемент И 22 разрешает прохождение тактовых импульсов с входа синхронизации 29 на счетный вход триггера управления 14 через элемент ИЛИ 16 и устанавливает его в нулевое состояние. Нулевое состояние триггера разрешает прохождение тактовых импульсов с входа синхронизации 27 на вход синхронизации регистра текущего адреса 4 и запрещает прохождение тактовых импульсов на счетный вход триггера управления 14. Далее в регистр текущего адреса 4 записывается следующий адрес программы и цикл повторяется. По окончании копирования, когда триггер управления устанавливается в нуль, с выхода 34 будет выдан сигнал в систему о конце копирования. Нормальный режим работы с признаком ветвления (см. фиг.1, 2, 4) отличается от режима работы, описанного выше. тем. что в команде, хранящейся в памяти 1, содержится метка. При этом с выхода метки 41 памяти единичный сигнал запретит запись текущего адреса в регистр адреса программы 6 и запись начального адреса 6 счетчик адреса памяти 7. При смене адреса в регистре текущего адреса 4 устройство работает как и в первом режиме. При появлении на выходе 39 кода логического условия осуществляется модификация младшего разряда адреса: если логическое

условие равно 0 (1), то осуществляется обра- щение к четной (нечетной) ячейке после записи адреса в регистр 5.

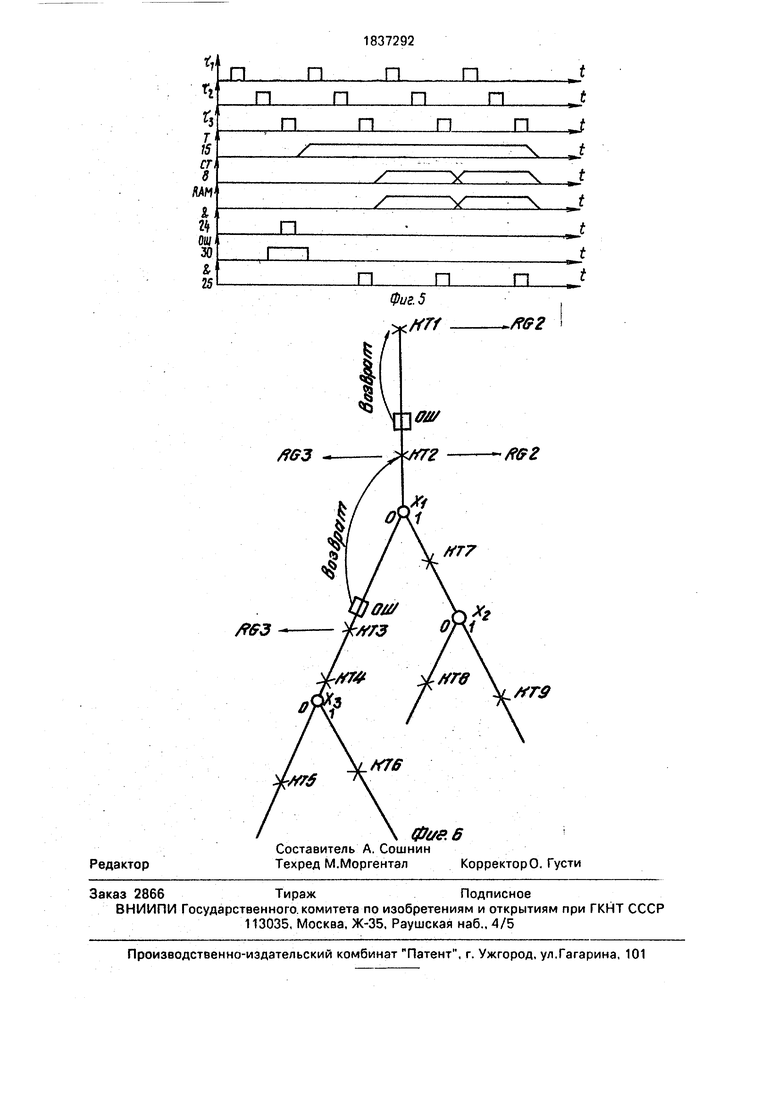

Режим ошибки (см. фиг.1, 2, 5). При поступлении с входа ошибки 30 сигнала об ошибке из системы откроется элемент И 24, тем самым разрешается проход тактовых импульсов с входа синхронизации 29 на вход синхронизации триггера ошибки 15. Сигнал ошибки поступает на вход установки в единицу триггера ошибки 15 и по тактовому импульсу он установится в единичное состояние, при этом откроется элемент И 25 и в систему будет выдан сигнал о начале считывания данных из памяти 3. Через от- крытый элемент И 25 тактовые импульсы с входа синхронизации 29 пойдут на счетный вход счетчика адреса 8. который имеет емкость, равную количеству ячеек памяти в памяти 3. Счетчик 8 формирует адреса ячеек памяти 3 и подает их через коммутатор 12, который переключен единичным состоянием триггера ошибки 8 на адресный вход памяти 3. Одновременно эти же адреса поступают на адресный вход демультиплексо- ра 11 и данные из памяти 3 поступают в систему. Производится считывание всех ячеек памяти 3. Считывание продолжается до переполнения счетчика адреса 8. i При переполнении счетчик адреса 8 вы- даст на R-вход триггера ошибки 15 единичный сигнал, который установит его по тактовым импульсам 29 в нулевое состояние. При этом с выхода ошибки 35 будет выдан в систему сигнал о конце копирова- ния данных из памяти 3. Нулевое состояние триггера ошибки 15 обеспечит блокировку элемент И 25. Далее система запрашивает адрес, хранящийся в регистре адреса программы 6 и возвращает программу на этот адрес. Работа устройства после возврата аналогична предыдущим режимам.

Таким образом, предлагаемое устройство реализует процедуру избирательного солирования источников информации, опи- :ывающих состояние системы с учетом конфетного участка программы.

; Формула изобретения I Устройство для восстановления инфор- мации о состоянии системы, содержащее память контрольных точек, регистр текущео адреса, регистр контрольной точки, реистр адреса программы, первый счетчик адреса, мультиплексор логических условий,

:оммутатор, схему сравнения, триггер управления, триггер ошибки, элемент ИЛИ, с

шрвого по девятый элементы И, причем иыход поля адреса контрольных точек пэмяи соединен с первым входом схемы сравнения, выход поля логических условий памяти контрольных точек соединен с адресным входом мультиплексора логических условий, вход логических условий устройства соединен с информационным входом мультиплексора логических условий, о т л и- ч ajojM e e с я тем, что, с целью расширения области применения, путем восстановления информации о состоянии системы при сбоях, оно дополнительно содержит память адресов, память состояний, мультиплексор данных, второй счетчик адреса, демультиплексор, причем вход адреса устройства соединен с информационным входом регистра текущего адреса, выход которого соединен с вторым входом схемы сравнения и информационным входом регистра адреса программы, выход которого является выходом адреса устройства, выход поля текущего-адреса памяти контрольных точек соединен с информационным входом регистра контрольной точки, выход которого соединен с адресным входом памяти контрольных точек, выход одного из разрядов поля текущего адреса памяти контрольных точек соединен с одним из разрядов информационного входа мультиплексора логических условий, выход кото- рого соединен с одним из разрядов информационного входа регистра контрольной точки, выход поля начального адреса памяти адресов соединен с первым информационным входом коммутатора и адресным входом мультиплексора данных, вход данных устройства соединен с информационным входом мультиплексора данных, выход которого соединен с информационным входом памяти состояний, выход второго счетчика адреса соединен с вторым информационным входом коммутатора и с адресным входом демультиллексора, выход которого является выходом данных устройства, прямой выход триггера управления является выходом контрольной точки устройства, первый вход первого элемента И соединен с первым входом синхронизации устройства, второй вход первого элемента И соединен с инверсным выходом триггера управления, выход первого элемента И соединен с входом синхронизации регистра текущего адреса, первый вход второго элемента и соединен с вторым входом синхронизации устройства, второй вход второго элемента И соединен с инверсным выходом триггера управления, третий вход второго элемента И соединен с выходом схемы сравнения, выход второго элемента И соединен с входом синхронизации регистра контрольной точки, первый вход третьего элемента И соединен с выходом схемы сравнения, второй инверсный вход третьего элемента И соединен с выходом метки памяти контрольных точек, третий вход третьего элемента И соединен с входом синхронизации устройства, выход третьего элемента И соединен с входом синхронизации регистра адреса программы, первый вход четвертого элемента И соединен с выходом схемы сравнения, второй вход четвертого элемента И соединен с инверсным выходом триггера управления, третий инверсный вход четвертого элемента И соединен с выходом метки памяти контрольных точек, четвертый вход четвертого элемента И соединен с вторым входом синхронизации устройства, выход четвертого элемента И соединен с входом синхронизации первого счетчика адреса, с первым входом элемента ИЛИ, первый инверсный вход пятого элемента И соединен с инверсным выходом триггера управления, второй вход пятого элемента И соединен с выходом метки памяти адресов, выход пятого элемента И соединен с счетным входом первого счетчика адресов, первый вход шестого элемента И соединен с выходом метки памяти адресов, второй инверсный вход шестого элемента И соединен с инверсным выходом

триггера управления, третий вход шестого элемента И соединен с выходом седьмого элемента И, выход шестого элемента И соединен с вторым входом элемента ИЛИ,

первый вход седьмого элемента И соединен с прямым выходом триггера управления, второй вход седьмого элемента И соединен с третьим входом синхронизации устройства, выход седьмого элемента

И соединен с входом разрешения записи памяти состояний, первый вход восьмого элемента И соединен с входвм ошибки устройства, второй вход восьмого элемента И соединен с третьим входом синхронизации устройства, выход восьмого элемента И соединен с входом установки в 1 триггера ошибки, первый вход девятого элемента И соединен с третьим входом синхронизации устройства, второй вход девятого элемента И соединен с выходом триггера ошибки, выход девятого элемента И соединен со счетным входом второго счетчика адреса, вход установки в О триггера ошибки соединен с выходом переполнения второго

счетчика адреса, выход триггера ошибки соединен с управляющим входом коммутатора и является выходом прерываний устройства.

Фиг. 1

( #0V0Sr0 У

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Программный управляющий модуль с контролем | 1990 |

|

SU1758634A1 |

| Программируемый контроллер | 1990 |

|

SU1714599A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100625A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

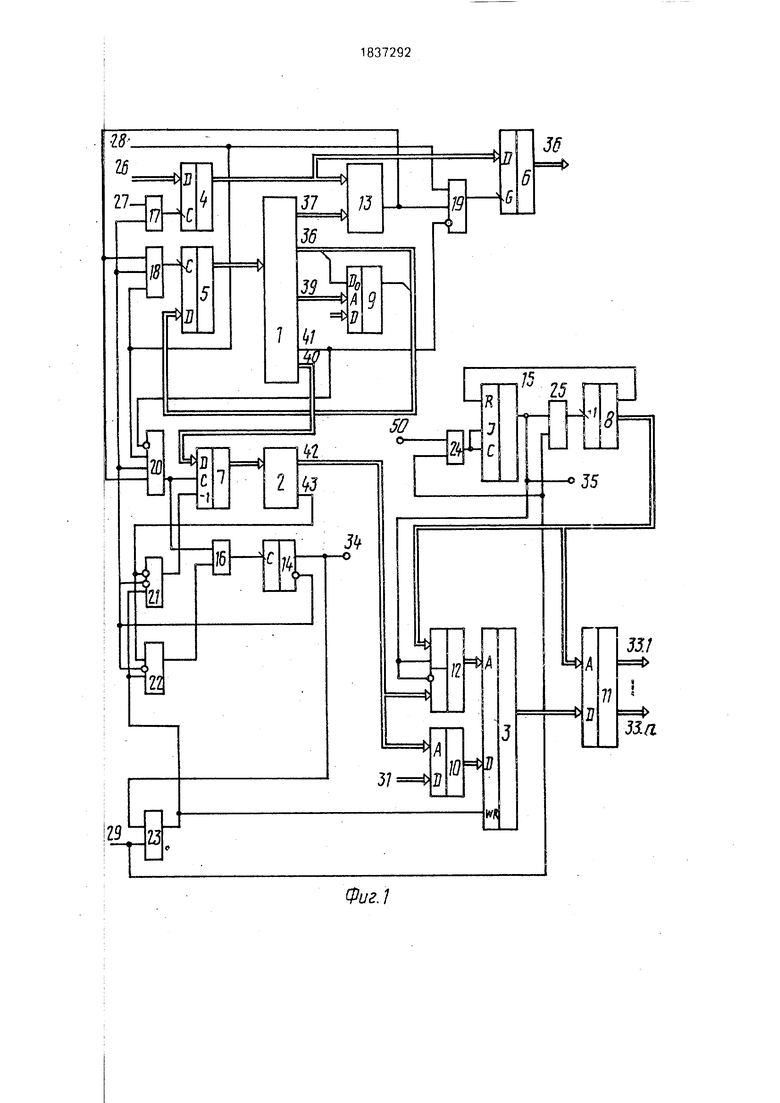

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в управляющих и вычислительных системах с возможностью восстановления процесса функционирования Изобретение относится к автоматике и вычислительной технике и может быть использовано в управляющих и вычислительных системах с возможностью восстановления процесса функционирования при сбоях, а также в системах отладки сложных управляющих комплексов. Цель изобретения - расширение области применения за счет обеспечения восстановления информации о состоянии системы при сбоях. На фиг.1 приведена функциональная схема устройства: на фиг.2 - блок-схема алгоритма работы устройства; на фиг.З, 4 - временные диаграммы работы устройства (в нормальном режиме, с признаком ветвления); на фиг.5 - временная диаграмма рабопри сбоях. Цель изобретения - расширение области применения, за счет обеспечения восстановления информации состояния системы при сбоях. Поставленная цель достигается тем, что устройство содержит память контрольных точек, память адресов, память состояний, регистр текущего адреса, регистр контрольной точки, регистр адреса программы, два счетчика адреса, мультиплексоры, демультиплексор, коммутатор, схему сравнения, триггеры управления и ошибки, элемент ИЛИ, элементы И. Сущность изобретения состоит fe реализации механизма возврата к участку программы, на котором появился сбой, с учетом реализуемого участка программы. Устройство работает в трех режимах; нормальный режим без признака ветвления, нормальный режим с признаком ветвления, режим ошибки. 6 ил. ты устройства-в режиме ошибки; на фиг.6 - схема алгоритма работы устройства. Устройство содержит (фиг.1) память 1 контрольных точек, память 2 адресов, память 3 состояний, регистры текущего адреса 4, контрольной точки 5, адреса программы 6 соответственно, первый счетчик 7 адреса, второй счетчик 8 адреса, мультиплексоры логических условий 9, данных 10, демультиплексор 11, коммутатор 12, схему сравнения 13, триггеры управления 14, ошибки 15, элемент ИЛИ 16с первого 17 по девятый 25 элементы И, вход адреса 26 с первого 27 по третий 29 входы синхронизации, вход сигнала ошибки 30, вход данных 31, вход логических условий 32, выходы данных 33.1-33.п. выход контрольной точки 34, выход прерыW Ё СО ч hO О hO 5

&&/ffec z лр0ер0/ / б/

i

&&/7есл #Г

(&#Ј erateeccc. 03Ј/

( /tesreief 0

06// o/r/sf#Ј/e

/yff0S / &A# f&/

C //f7A/ffa //t/e аЪ/мй/х &з 03 У

0030/t0/rr - #A/Jyufys0 /fT

I

.X

Редактор

0f/e. 6

Составитель А. Сошнин

Техред М.МоргенталКорректор О. Густи

tfffZ

ЯГ&

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-08-30—Публикация

1990-04-16—Подача