Изобретение относится к вычислительной технике и может быть использовано для построения устройств управления ЭВМ с повышенной устойчивостью к отказам и сбоям.

Целью изобретения является повышение устойчивости устройства к отказам и сбоям.

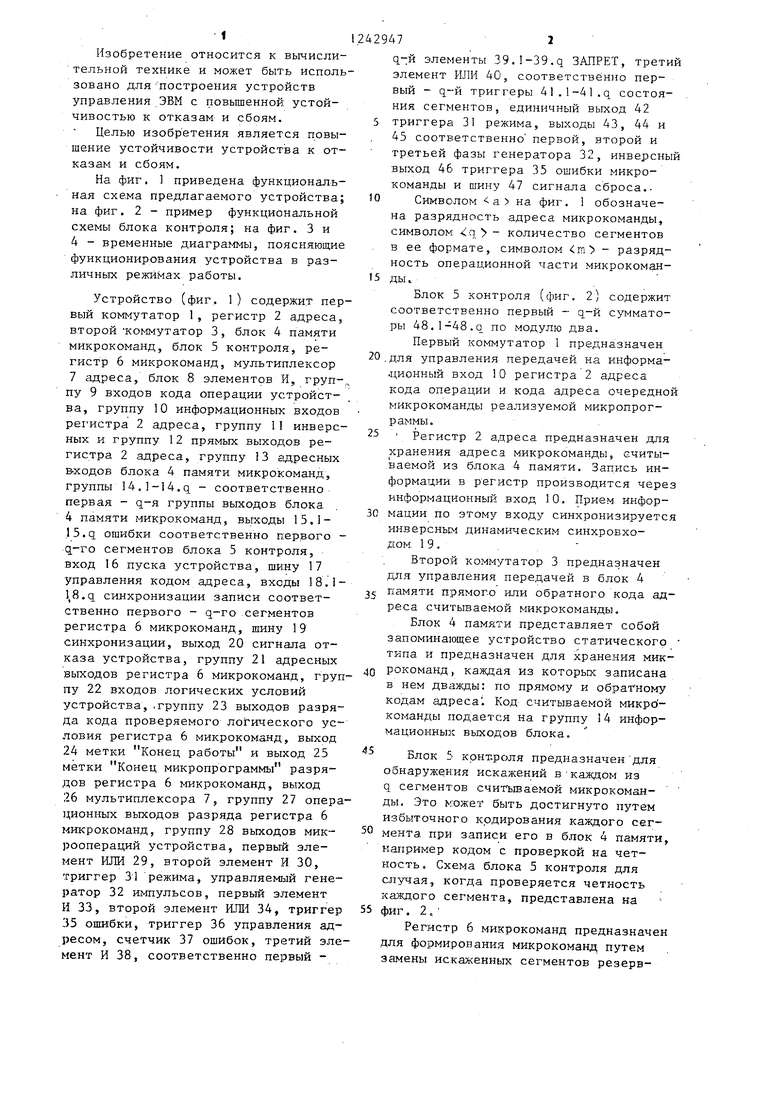

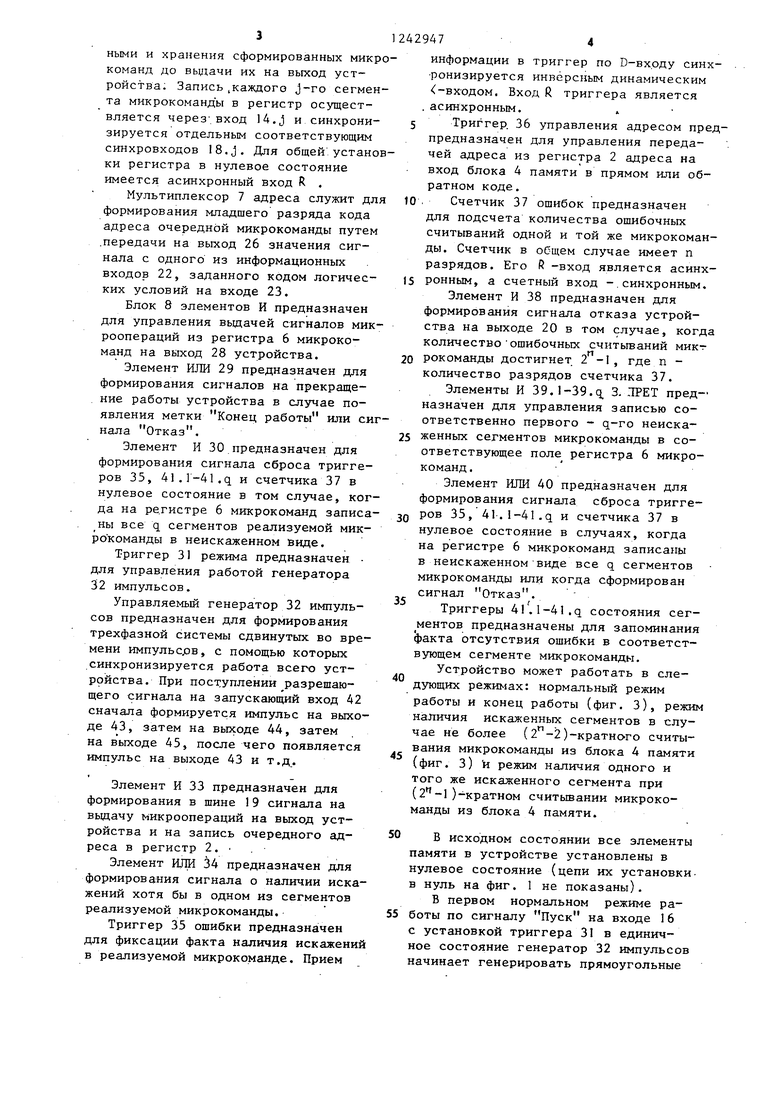

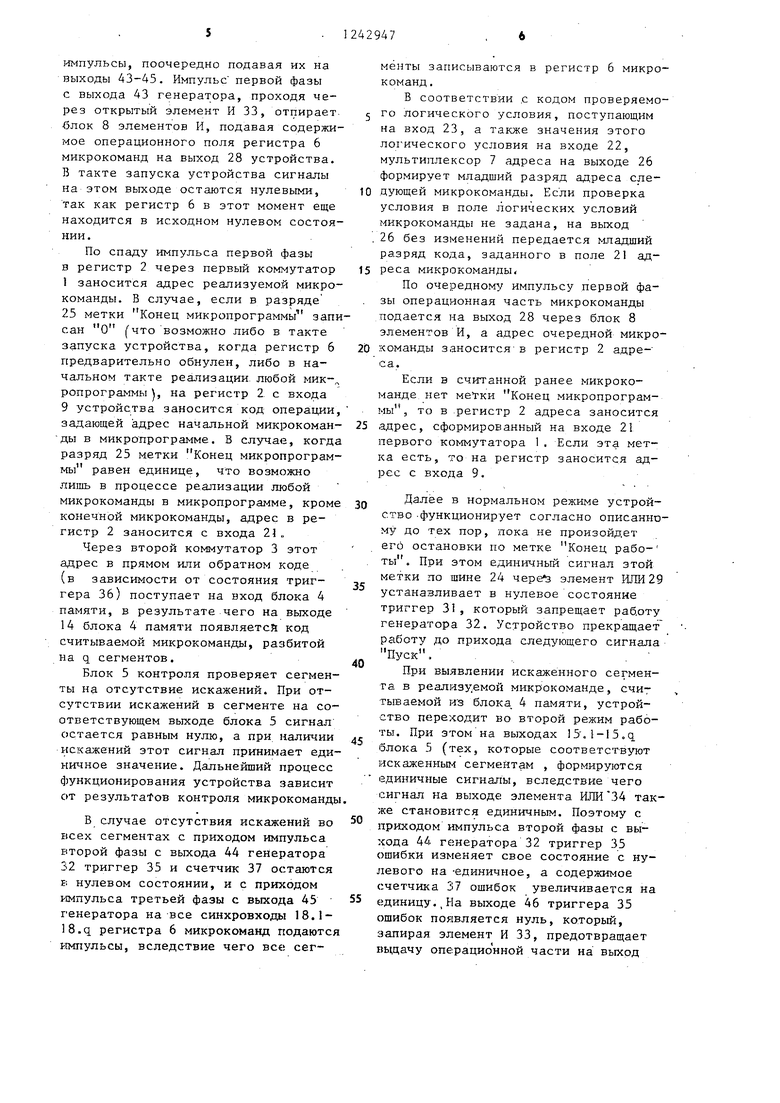

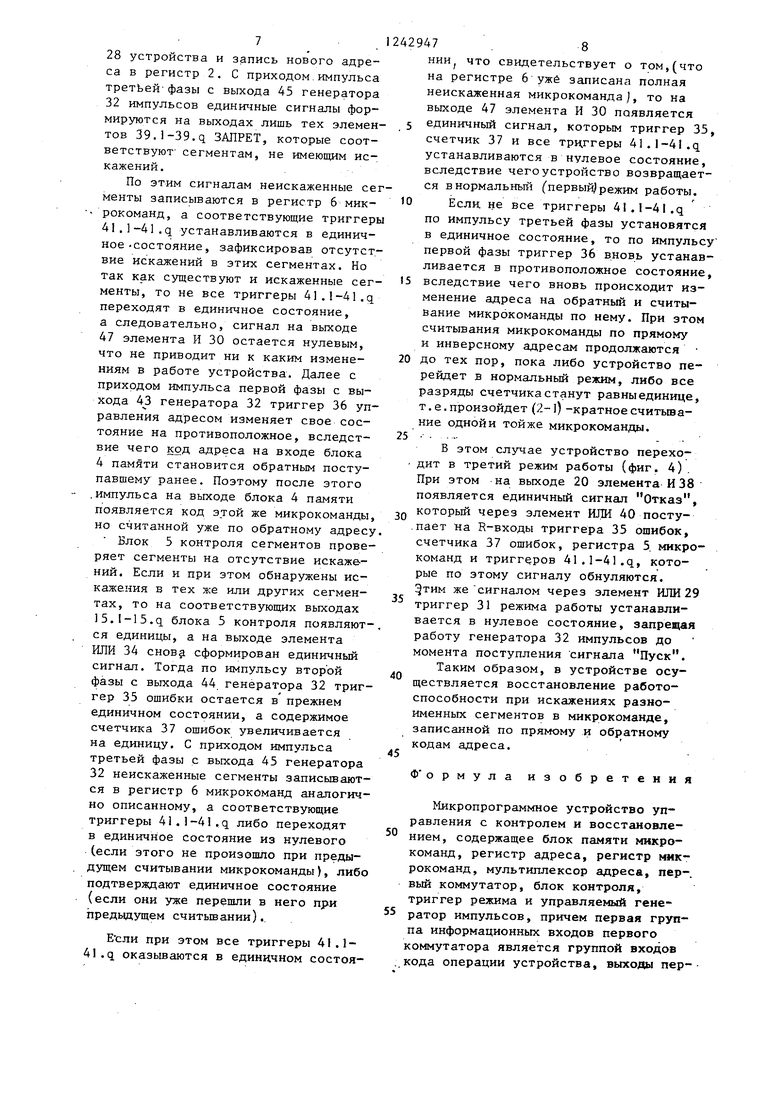

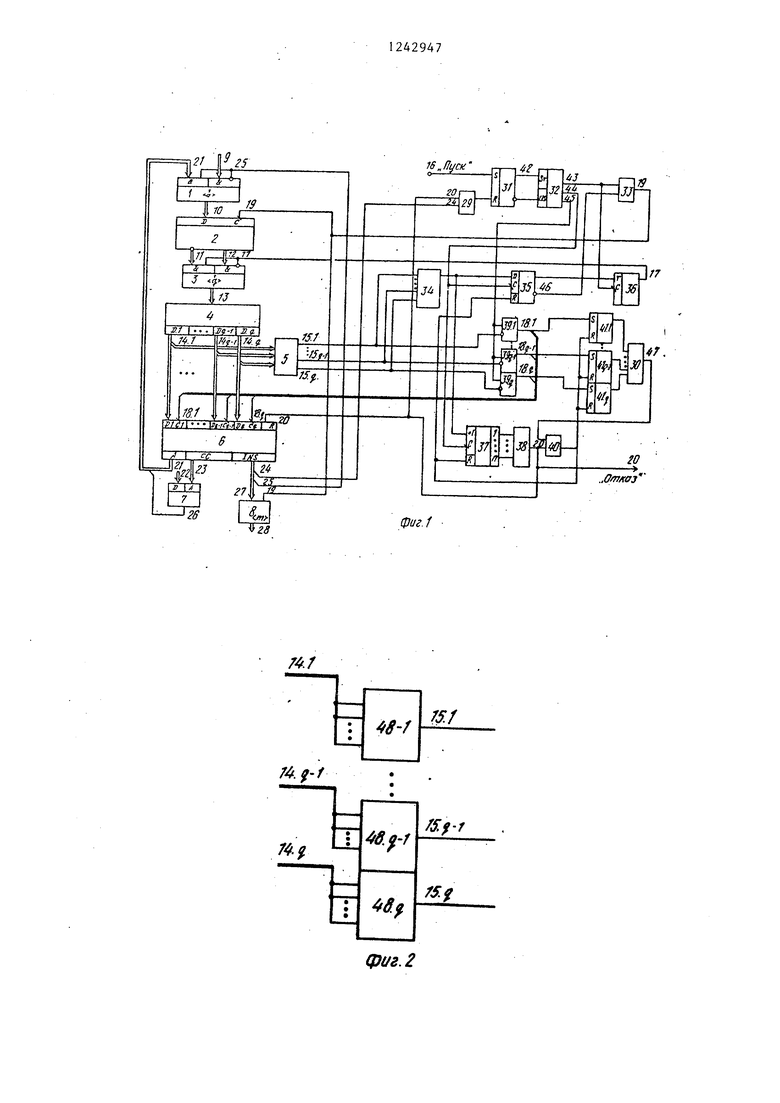

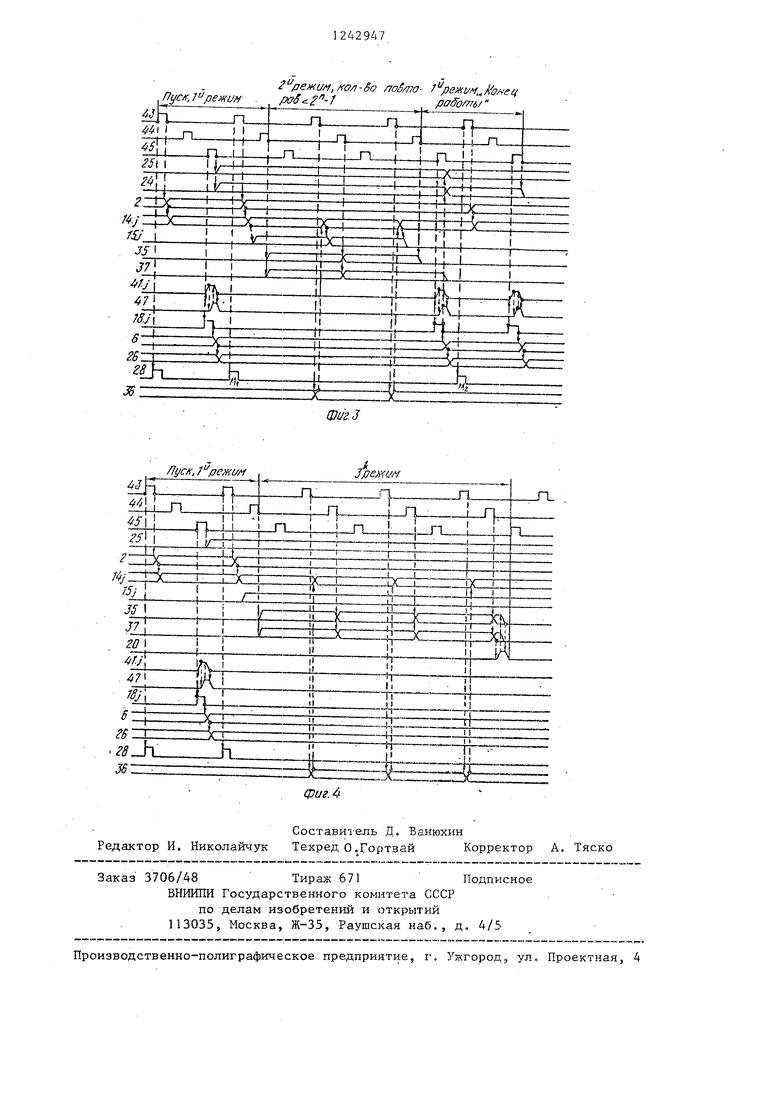

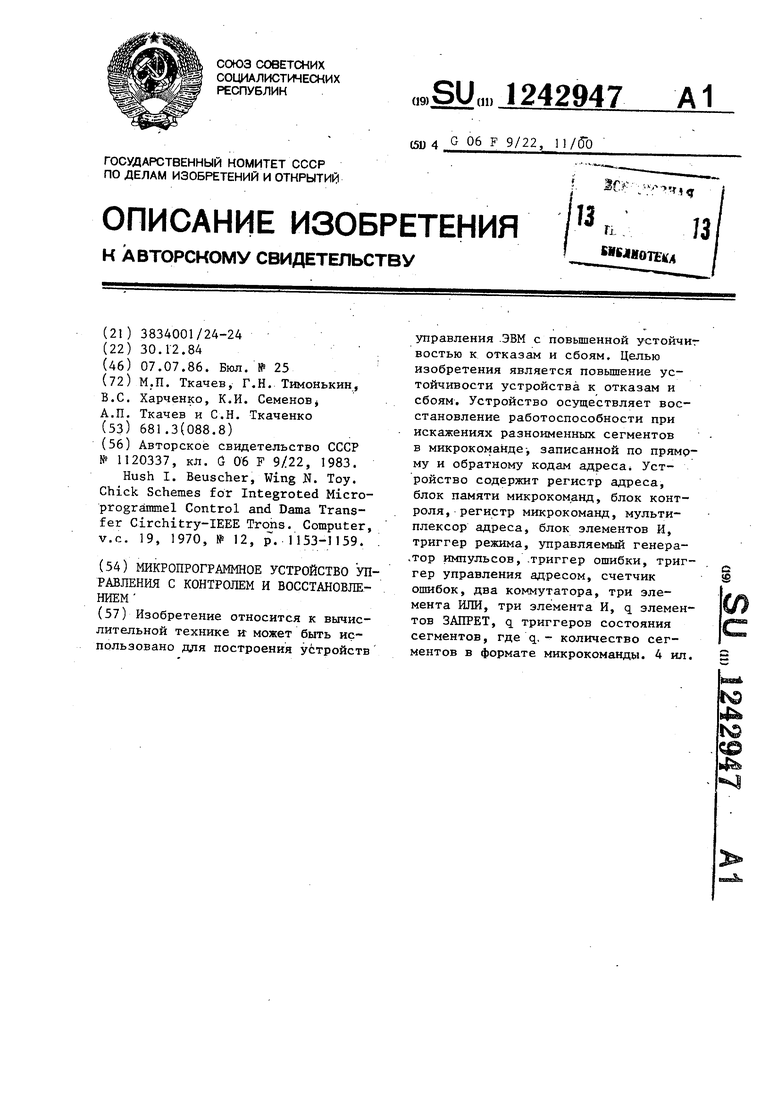

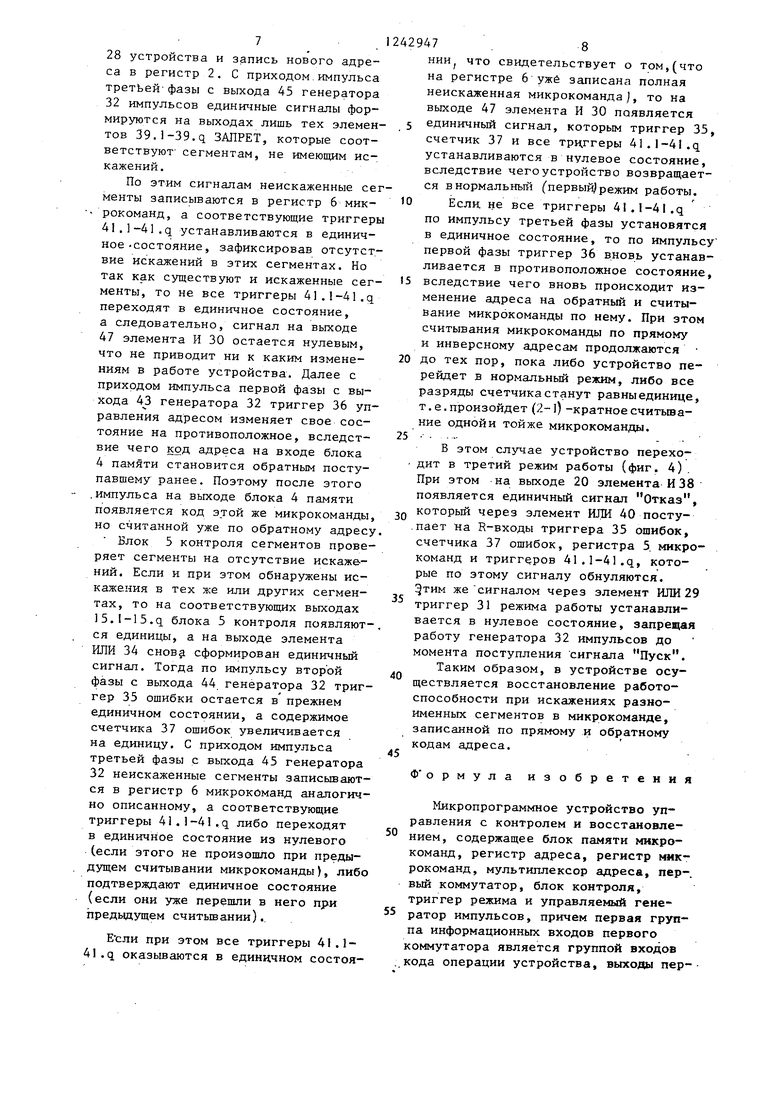

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - пример функциональной схемы блока контроля; на фиг. 3 и 4 - временные диаграи-оты, поясняющие функционирования устройства в различных режимах работы.

Устройство (фиг. 1) содержит первый коммутатор 1, регистр 2 адреса, второй коммутатор 3, блок 4 памяти микрокоманд, блок 5 контроля, регистр 6 микрокоманд, мультиплексор 7 адреса, блок 8 элементов И, группу 9 входов кода операции устройства, группу 10 информационных входов регистра 2 адреса, группу 11 инверсных и группу 12 прямых выходов регистра 2 адреса, группу 13 адресных в-ходов блока 4 памяти микрокоманд, группы 14.1-14.q - соответственно первая - q-я группы выходов блока 4 памяти микрокоманд, выходы 15.1- 15.q ошибки соответственно первого - q-ro сегментов блока 5 контроля, вход 16 пуска устройства, шину 17 управления кодом адреса, входы 18.1- 1,8.q синхронизации записи соответственно первого - q-ro .сегментов регистра 6 микрокоманд, шину 19 синхронизации, выход 20 сигнала отказа устройства, группу 21 адресных выходов регистра 6 микрокоманд, группу 22 входов логических условий устройства, .группу 23 выходов разряда кода проверяемого логического условия регистра 6 микрокоманд, выход 24 метки Конец работы и выход 25 метки Конец микропрограммы разрядов регистра 6 микрокоманд, выход 26 мультиплексора 7, группу 27 операционных выходов разряда регистра 6 микрокоманд, группу 28 выходов микроопераций устройства, первый элемент ИЛИ 29, второй элемент И 30, триггер 3 режима, управляемгзш генератор 32 импульсов, первый элемент И 33, второй элемент ИЛИ 34, триггер 35 ошибки, триггер 36 управления адресом, счетчик 37 ошибок, третий элемент И 38, соответственно первый 429472

q-;й элементы 39. 1-39.q ЗАПРЕТ, третий элемент ИЛИ 40, соответственно первый - q-й триггеры 41.1-41.q состояния сегментов, единичный выход 42

5 триггера 31 режима, выходы 43, 44 и 45 соответственно первой, второй и третьей фазы генератора 32, инверсный выход 46 триггера 35 ошибки микрокоманды и шину 47 сигнала сброса. О Символом а на фиг. обозначена разрядность адреса микрокоманды, символом iq - количество сегментов в ее формате, символом т - разрядность операционной части микрокоман 5 ды

Блок 5 контроля (фиг. 2) содержит соответственно первый - q-й сумматоры 48.1-48.q по модулю два.

Первый коммутатор 1 предназначен

20.для управления передачей на информа- .ционный вход 10 регистра 2 адреса кода операции и кода адреса очередной микрокоманды реализуемой микропрограммы.

25 Регистр 2 адреса предназначен для хранения адреса микрокоманды, считываемой из блока 4 памяти. Запись информации в регистр производится через информационный вход 10, Прием инфор30 мадии по этому входу синхронизируется инверсным динамическим синхровхо- дом- 19.

Второй коммутатор 3 предназначен для управления передачей в блок 4

35 памяти прямого или обратного кода адреса считываемой микрокоманды.

Блок 4 памяти представляет собой запоминающее устройство статического типа и предназначен для хранения мик40 рокоманд, каждая из которых записана в нем дважд,ы: по прямому и обратному кодам адреса . Код считываемой микрокоманды подается на группу 4 информационных выходов блока.

Блок 5 крнт.роля предназначен для обнаружения искажений в каждом из q сегментов считываемой микрокоманды. Это может быть достигнуто путем избыточного кодирования каждого сег50 мента при записи его в блок 4 памяти, например кодом с проверкой на четность , Схема блока 5 контроля для случая, когда проверяется четность каждого сегмента, представлена на

55 фиг. 2.

Регистр 6 микрокоманд предназначен для формирования микрокоманд путем зг1мены искаженных сегментов резервЭ

ными и хранения сформированных микркоманд до выдачи их на выход устройства. Запись .каждого J-ro сегмента микрокоманды в регистр осуществляется через вход 14.J и синхронизируется отдельным соответствующим синхровходов 18.J. Для общей устаноки регистра в нулевое состояние имеется асинхронный вход R .

Мультиплексор 7 адреса служит дл формирования младшего разряда кода адреса очередной микрокоманды путем .передачи на выход 26 значения сигнала с одного из информационных входов 22, заданного кодом логических условий на входе 23.

Блок 8 элементов И предназначен для управления выдачей сигналов микроопераций из регистра 6 микрокоманд на выход 28 устройства.

Элемент ИЛИ 29 предназначен для формирования сигналов на прекращение работы устройства в случае появления метки Конец работы или синала Отказ.

Элемент И 30.предназначен для формирования сигнала сброса триггеров 35, 41.1-41.q и счетчика 37 в нулевое состояние в том случае, когда на регистре 6 микрокоманд записа ны все q сегментов реализуемой микрокоманды в неискаженном виде.

Триггер 31 режима предназначен для управления работой генератора 32 импульсов.

Управляемый генератор 32 импульсов предназначен для формирования трехфазной системы сдвинутых во времени импульс 1В, с помощью которых синхронизируется работа всего устройства. При пос1:уплении разрещаю- щего сигнала на запускающий вход 42 сначала формируется импульс на выходе 43, затем на выходе 44, затем на выходе 45, после чего появляется импульс на выходе 43 и т.д.

Элемент И 33 предназначен для формирования в шине 19 сигнала на выдачу микроопераций на выход устройства и на запись очередного адреса в регистр 2.

Элемент ИДИ 34 предназначен для формирования сигнала о наличии искажений хотя бы в одном из сегментов реализуемой микрокоманды.

Триггер 35 ошибки предназначен для фиксации факта наличия искажений в реализуемой микрокоманде. Прием

429474

информации в триггер по D-вхрду синхронизируется инверсньм динамическим -входом. Вход R триггера является .асинхронным.

5 Триггер. 36 управления адресом пред- предназначен для управления передачей адреса из регистра 2 адреса на вход блока 4 памяти в прямом или обратном коде.

10. Счетчик 37 ошибок предназначен для подсчета количества ошибочных считываний одной и той же микрокоманды. Счетчик в общем случае имеет п разрядов. Его R -вход является асинх- 15 ронным, а счетный вход -.синхронным.

Элемент И 38 предназначен для формирования сигнала отказа устройства на выходе 20 в том случае, когда количество ошибочных считьгеаний мик- 20 рокоманды достигнет. 2-1, где п - количество разрядов счетчика 37.

Элементы И 39. 1-39.q. 3. ЛРЕТ предназначен для управления записью соответственно первого - q-ro неиска- 25 женных сегментов микрокоманды в соответствующее поле регистра 6 микрокоманд ,

Элемент ИЛИ 40 предназначен для формирования сигнала сброса тригге- 3Q ров 35, 41.1-41.q и счетчика 37 в нулевое состояние в случаях, когда на регистре 6 микрокоманд записаны в неискаженном виде все q сегментов микрокоманды или когда сформирован сигнал Отказ.

Триггеры 4l . l-41.q состояния сегментов предназначены для запоминания Ьакта отсутствия ошибки в соответствующем сегменте микрокоманды.

Устройство может работать в следующих режимах: нормальный режим работы и конец работы (фиг. З), режим наличия искаженных сегментов в случае не более (2 -2)-кратнО ГО считывания микрокоманды из блока 4 памяти (фиг. 3) и режим наличия одного и того же искаженного сегмента при ( )-кратном считывании микрокоманды из блока 4 памяти.

0

5

В исходном состоянии все элементы памяти в устройстве установлены в нулевое состояние (цепи их установки, в нуль на фиг. 1 не показаны).

В первом нормальном режиме работы по сигналу Пуск на входе 16 с установкой триггера 31 в единичное состояние генератор 32 импульсов начинает генерировать прямоугольные

i-iMnynbCbJ, поочередно подавая их на выходы 43-45. Импульс первой фазы с выхода 43 генератора, проходя через открытый элемент И 33, отпирает -блок 8 элементов И, подавая содержимое операционного поля регистра 6 микрокоманд на выход 28 устройства.

8такте запуска устройства сигналы

на этом выходе остаются нулевыми, так как регистр 6 в этот момент еще находится в исходном нулевом состоянии.

По спаду импульса первой фазы в регистр 2 через первый ком1 4утатор 1 заносится адрес реализуемой микрокоманды. В случае, если в разряде 25 метки Конец микропрограммы записан О (что возможно либо в такте запуска устройства, когда регистр 6 предварительно обнулен, либо в начальном такте реализации, любой мик-„ ропрограммы ), на регистр 2. с входа

9устройства заносится код операции, задающей адрес начальной микрокоман-

ды в микропрограмме. В случае, когда разряд 25 метки Конец микропрограммы равен единице, что возможно лишь в процессе реализации любой микрокоманды в микропрограмме, кроме конечной микрокоманды, адрес в регистр 2 заносится с входа 21„

Через второй коммутатор 3 этот адрес в прямом или обратном коде (в зависимости от состояния триггера 36) поступает на вход блока 4 памяти, в результате.чего на выходе 14 блока 4 памяти появляетсй код считываемой микрокоманды, разбитой на q сегментов.

Блок 5 контроля проверяет сегменты на отсутствие искажений. При отсутствии искажений в сегменте на соответствующем выходе блока 5 сигнал остается равным нулю, а при наличии искажений этот сигнал принимает единичное значение. Дальнейший процесс функционирования устройства зависит от результатов контроля микрокоманды

В случае отсутствия искажений во всех сегментах с приходом импульса второй фазы с выхода 44 генератора 32 триггер 35 и счетчик 37 остаются в нулевом состоянии, и с при содом импульса третьей фазы с выхода 45 генератора на все синхровходы 18.1- IB.q регистра 6 микрокоманд подаютс импульсы, вследствие чего вс€; сег

j

0

5 U

5

О

0

5

0 5

5

менты записываются в регистр 6 микрокоманд.

В соответствии с кодом проверяемого логического условия, поступающим на вход 23, а также значения этого логического условия на входе 22, мультиплексор 7 адреса на выходе 26 формирует младший разряд адреса следующей микрокоманды. Если проверка условия в поле логических условий микрокоманды не задана, на выход 26 без изменений передается младший разряд кода, заданного в поле 21 адреса микрокоманды.

По очередному импульсу первой фазы операционная часть микрокоманды подается на выход 28 чер.ез блок 8 элементов И, а адрес очередной микрокоманды заносится- в регистр 2 адре- са.

Если в считанной ранее микрокоманде нет метки Конец микропрограммы, то в регистр 2 адреса заносится адрес, сформированный на входе 21 первого коммутатора 1. Если эта метка есть, то на регистр заносится адрес с входа 9.

Далее в нормальном режиме устройство -функционирует согласно описанному до тех пор, пока не произойдет его остановки по метке Конец рабо- ты. При этом единичный сигнал этой метки по шине 24 чере элемент ИЛИ 29 устанавливает в нулевое состояние триггер 31, который запрещает работу генератора 32. Устройство прекращает работу до прихода следующего сигнала Пуск. ...

При выявлении искаженного сегмента в реализуемой микрокоманде, счи7 тываемой из блока, 4 памяти, устройство переходит во второй режим работы. При этом на выходах 15. 1-15.q блока 5 (тех, которые соответствуют искаженным сегментам , формируются единичные сигналы, вследствие чего сигнал на выходе элемента ИЛИ 34 также становится единичным. Поэтому с приходом импульса второй фазы с выхода 44 генератора 32 триггер 35 ощибки изменяет свое состояние с нулевого на -единичное, а содержимое счетчика 37 ошибок увеличивается на единицу.,На выходе 46 триггера 35 ошибок появляется нуль, который, запирая элемент И 33, предотвращает вьщачу операционной части на выход

7.

28 устройства и запись нового адреса в регистр 2. С приходом.импульса третьей фазы с выхода 45 генератора 32 импульсов единичные сигналы формируются на выходах лишь тех элементов 39.1-39.q ЗАПРЕТ, которые соответствуют сегментам, не имеюгцим искажений.

По этим сигналам неискаженные сегменты записываются в регистр 6 микрокоманд, а соответствующие триггеры 4I.l-41.q устанавливаются в единичное -состояние, зафиксировав отсутствие искажений в этих сегментах. Но так как существуют и искаженные сегменты, то не все триггеры 41,1-41.q переходят в единичное состояние, а следовательно, сигнал на выходе 47 элемента И 30 остается нулевым, что не приводит ни к каким изменениям в работе устройства. Далее с приходом импульса первой фазы с выхода 4J3 генератора 32 триггер 36 управления адресом изменяет свое состояние на противоположное, вследствие чего код адреса на входе блока 4 памяти становится обратным поступавшему ранее. Поэтому после этого .импульса на выходе блока 4 памяти появляется код этой же микрокоманды, но считанной уже по обратному адресу Блок 5 контроля сегментов проверяет сегменты на отсутствие искажений. Если и при этом обнаружены искажения в тех же или других сегментах, то на соответствующих выходах 15.1-15.q блока 5 контроля появляются единицы, а на выходе элемента ИЛИ 34 сновэ сформирован единичный сигнал. Тогда по импульсу второй фазы с выхода 44 генератора 32 триггер 35 ошибки остается в прежнем единичном состоянии, а содержимое счетчика 37 ошибок увеличивается на единицу. С приходом импульса третьей фазы с выхода 45 генератора 32 неискаженные сегменты записываются в регистр 6 микрокоманд аналогично описанному, а соответствующие триггеры 41.1-41.q либо переходят в единичное состояние из нулевого (если этого не произошло при предыдущем считывании микрокоманды), либо подтверждают единичное состояние (если они уже перешли в него при предьщущем считьшании)..

Е сли при этом все триггеры 41.1- 4l.q оказываются в единичном состоя42947 . 8

нии что свидетельствует о том,(что на регистре 6 уже записана полная неискаженная микрокомандаJ, то на выходе 47 элемента И 30 появляется

5 единичный сигнал, которым триггер 35, счетчик 37 и все триггеры 41.1-41.q устанавливаются в нулевое состояние, вследствие чего устройство возвращается в нормальный Cпepвый peжим работы.

10 Если не все триггеры 41.1-41.q по импульсу третьей фазы установятся в единичное состояние, то по импульсу первой фазы триггер 36 вновь устанавливается в противоположное состояние,

15 вследствие чего вновь происходит изменение адреса на обратный и считывание микрокоманды по нему. При этом считывания микрокоманды по прямому и инверсному адресам продолжаются

20 до тех пор, пока либо устройство перейдет в нормальный режим, либо все разряды счетчика станут равныединице, т.е. произойдет (2-1) -кратное считьша- ние одной и той же микрокоманды.

25 - В этом случае устройство перехо дит в третий режим работы (фиг. 4). При этом на выходе 20 элемента И 38 появляется единичный сигнал Отказ, который через элемент ИЛИ 40 поступает на R-входы триггера 35 ошибок, счетчика 37 ошибок, регистра 5. микрокоманд и триггеров 41.1-41.q, которые по этому сигналу обнуляются, тим же сигналом через элемент ИЛИ 29 триггер 31 режима работы устанавливается в нулевое состояние, запрещая работу генератора 32 импульсов до момента поступления сигнала Пуск. Таким образом, в устройстве осуществляется восстановление работоспособности при искажениях разноименных сегментов в микрокоманде, записанной по прямому и обратному кодам адреса.

30

40

45

Ф ормула изобретения

Микропрограммное устройство управления с контролем и восстаиовле-

нием, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, мультиплексор адреса, пер-. вый коммутатор, блок контроля, триггер режима и управляемый генератор импульсов, причем первая группа информационных входов первого коммутатора является группой входов кода операции устройства, выходы пер-

13ОГО коммутатора соединены с группо информационных входов регистра адреса, первая - q-я группы выходов блока памяти микрокоманд, где q - количество сегментов в формате микрокоманды, соединены с соответствующими группами информационных входов регистра микрокоманд, выход разряда метки Конец микрокоманды программы регистра микрокоманд сое динен с инверсным и прямым управляющими входами первого коммутатора, группа выходов разряда кода проверяемого логического условия регистра микрокоманд соединена с первой группой информационных, входов мулы типлексора адреса, первый вход второй группы информационных входов которого соединен с младшим разрядо группы адресных выходов регистра, микрокоманд, а остальные входы второй группы информационных входов . мультиплексора адреса соединены с группой входов логических условий устройства, выход мультиплексора адреса соединен с младшим разрядом второй группы информационных входов первого коммутатора, старшие разряды второй группы информационных входов которого соединены со старшими разрядами группы адресных выходов регистра микрокоманд, S-вхо триггера режима является входом пуска устройства, прямой и инверсный- выходы триггера режима соединены соответственно с входами запуска и останова управляемого генератора импульсов, отличающееся тем, что, с целью повышения устойчи вости устройства к отказам и сбоям, оно содержит второй коммутатор, бло элементов И, триггер ошибки,.тригге управления адресом, q-триггеров состояния сегментов, счетчик ошиб.ок, группу .элементов ЗАПРЕТ, три элемента ИЛИ и три элемента И, причем группа выходов-разряда операций регистра микрокоманд соединена с группой информационных входов блока элементов И, группа выходов которого является группой выходов микроопераций устройства, выход разряда метки Конец работы регистра микрокоманд соединен с первым входом первого элемента ИЛИ, выход которого соединен с R-входом триггера ре- жима, выход первой фазы управляемог генератора импульсов соединен с ин-

0

5

0

версным. синхровходом триггера управления, адресом и первьм входом первого элемента И, выход которого соединен с инверсным синхровходом регистра адреса и с управляющим входом блока элементов И, выход триггера управления адресом соединен с Г инверсным и прямым управляющими входами второго KoivfMyTaTopa, первая и вторая группы информационных входов BToporq коммутатора соединены соответственно с группой прямых и группой инверсных выходов регистра адреса, группа выходов .второго коммутатора соединена с группой адресных входов блока памяти микрокоманд, выход второй фазы управляемого генератора импульсов соединен с инверсными синхровходами триггера ошибки и счетчика ошибок, прямой выход триггера ошибки соединен с Т-вхо- дом триггера управления адре- сом, инверсный выход триггера ошибки соединен с вторым входом первого - элемента И, первая q-я группы выходов блока памяти микрокоманд соеди- . иены с соответствующими групп-ами входов блока контроля, q-выходов ошибки блока контроля соединены с 0 входами второго элемента ИЛИ и инверсными входами соответственно первого q-ro элементов ЗАПРЕТ группы, прямые входы первого элементов ЗАПРЕТ группы подключены к - 5 выходу третьей фазы управляемого генераторс1 импульсов, выходы первого q-ro элементов ЗАПРЕТ группы соединены с S-входами соотве тствующих - триггеров состояния сегментов- и ин- 0 версными входами синхронизации соответствующих разрядов регистра микрокоманд, выход второго элемента ИЛИ соединен со счетным входом счетчика ошибок и с D-входом триггера- ошибки, 5 выходы триггеров состояния сегментов соединены с входами второго -элемента И, выход которого соединен с первым входом третьего ИЛИ, выход которого соединен с R входами 0 триггера ошибки, триггеров состояния сегментов и входом сброса счетчика ошибок, выходы разрядов счетчика ошибок соединены с входами третьего элемента И, выход которого соединен 5 с вторьми входам - первого и третьего элементов ;ШШ, входом установки в О регистра микрокоманд и с .выходом отказа устройства.

74.f f

H.

8-f

rs.f

48.f-r

rs.f-1

8.

fS.f

фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1275442A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1016782A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1104515A1 |

| Устройство для программного управления | 1989 |

|

SU1656498A1 |

| Устройство для контроля устройства микропрограммного управления | 1988 |

|

SU1608674A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043652A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

Изобретение относится к вычислительной технике иг может быть использовано для построения устройств управления .ЭВМ с повьшенной устойчиг востью к отказам и сбоям. Целью изобретения является повьшение устойчивости устройства к отказам и сбоям. Устройство осуществляет восстановление работоспособности при искажениях разноименных сегментов в микрокоманде-, записанной по прямо ну и обратному кодам адреса Устройство содержит регистр адреса, блок памяти микрокоманд, блок контроля, регистр микрокоманд, мультиплексор адреса, блок элементов И, триггер режима, управляемый генера- .тор импульсов, .триггер ошибки, триггер управления адресом, счетчик ошибок, два коммутатора, три элемента ИЛИ, три элемента И, q элементов ЗАПРЕТ, g триггеров состояния сегментов, где q, - количество сегментов в формате микрокоманды. 4 ил. с (g

| Микропрограммное устройство управления с контролем и восстановлением | 1983 |

|

SU1120337A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Hush I | |||

| Beuscher, Wing N | |||

| Toy | |||

| Chick Schemes for Integroted Micro- programmel Control and Dama Transfer Circhitry-IEEE Trons | |||

| Computer, v,c | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Трепально-чесальный станок | 1924 |

|

SU1153A1 |

Авторы

Даты

1986-07-07—Публикация

1984-12-30—Подача