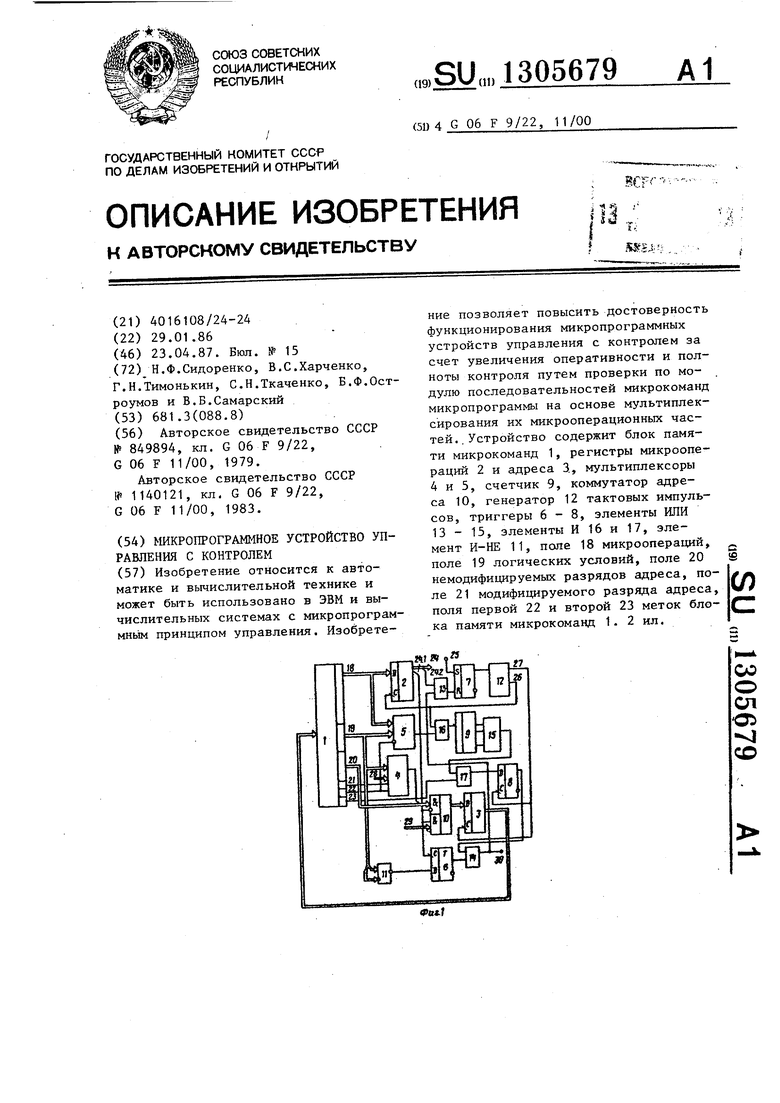

Изобретение относится к автоматике и вычислительной технике и может быть использовано в ЭВМ и вычис-i лительных системах с микропрограммным принципом управления.

Целью изобретения является повышение достоверности функционирования микропрограммного устройства управления с контролем.

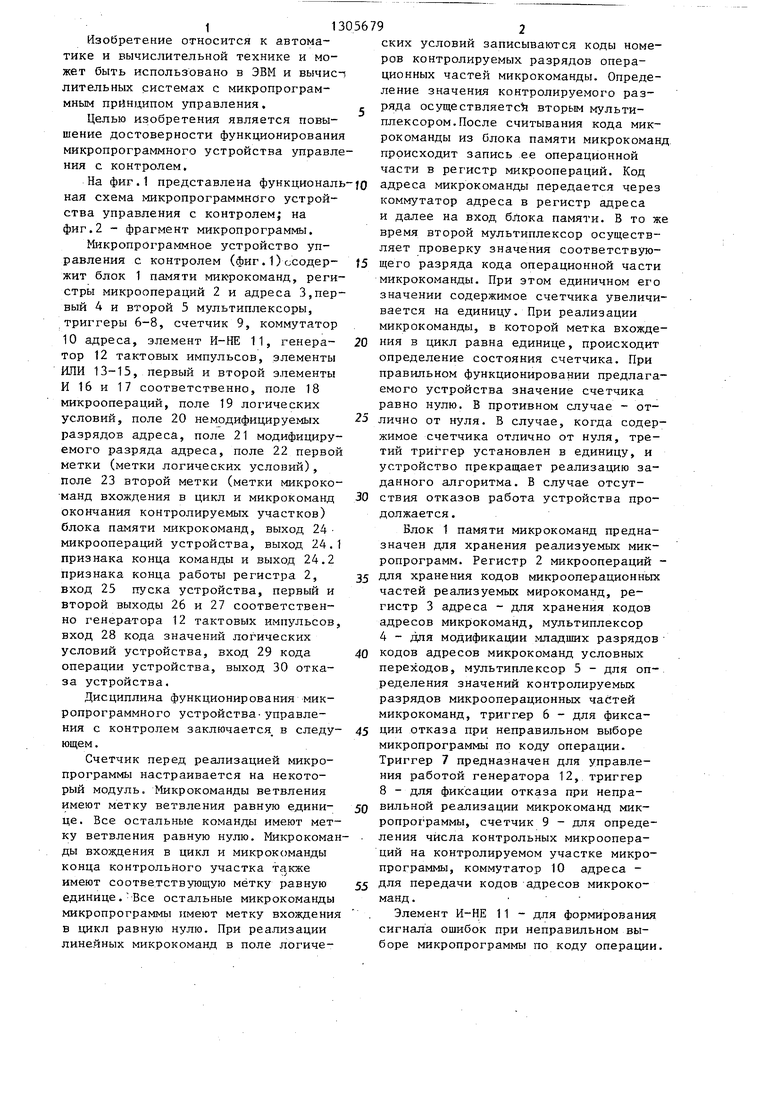

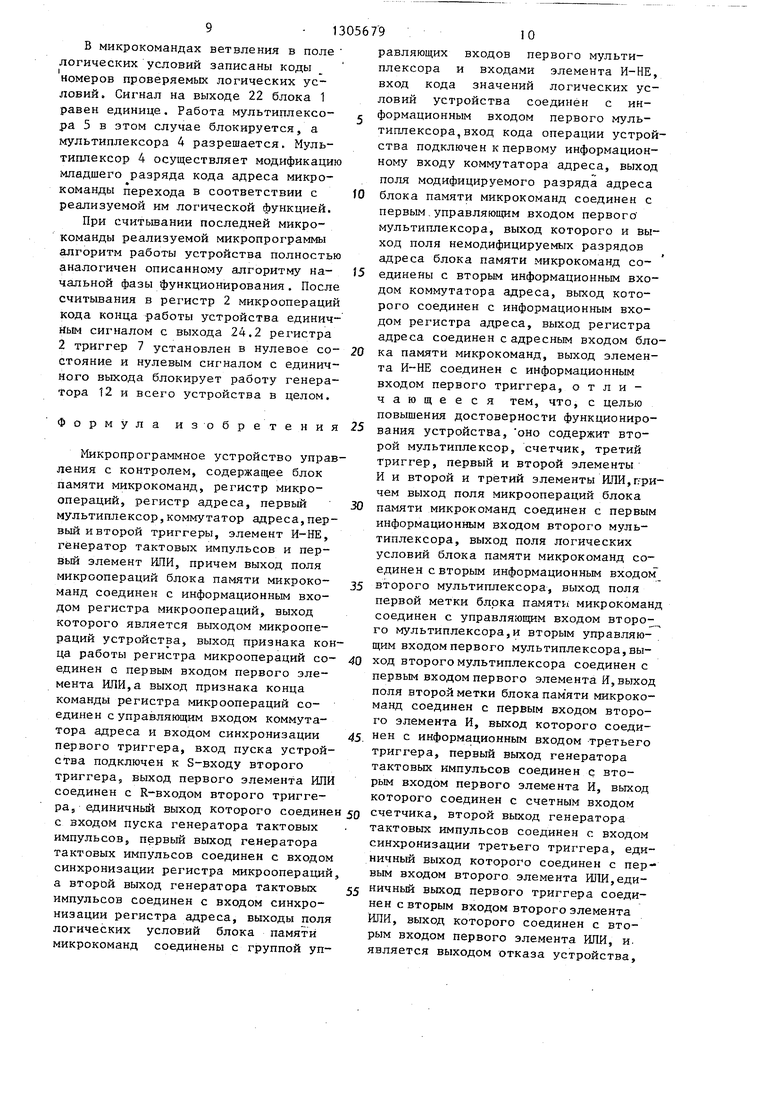

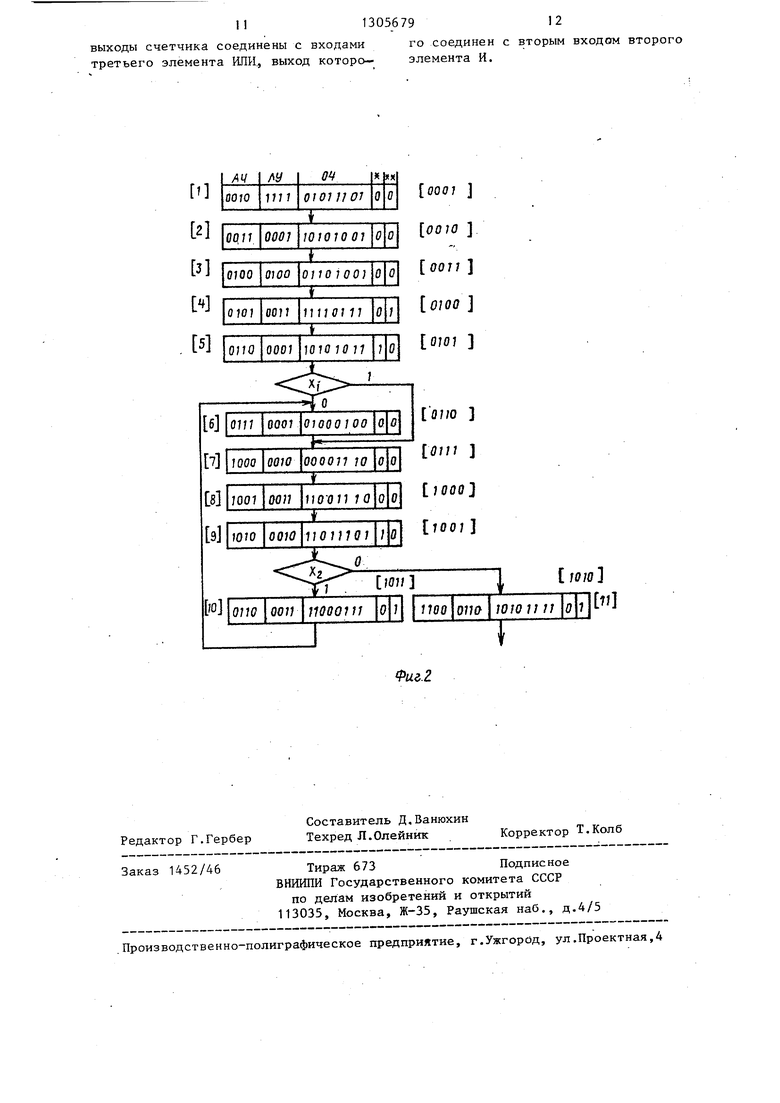

На фиг.1 представлена функциональ-jo адреса микрокоманды передается через

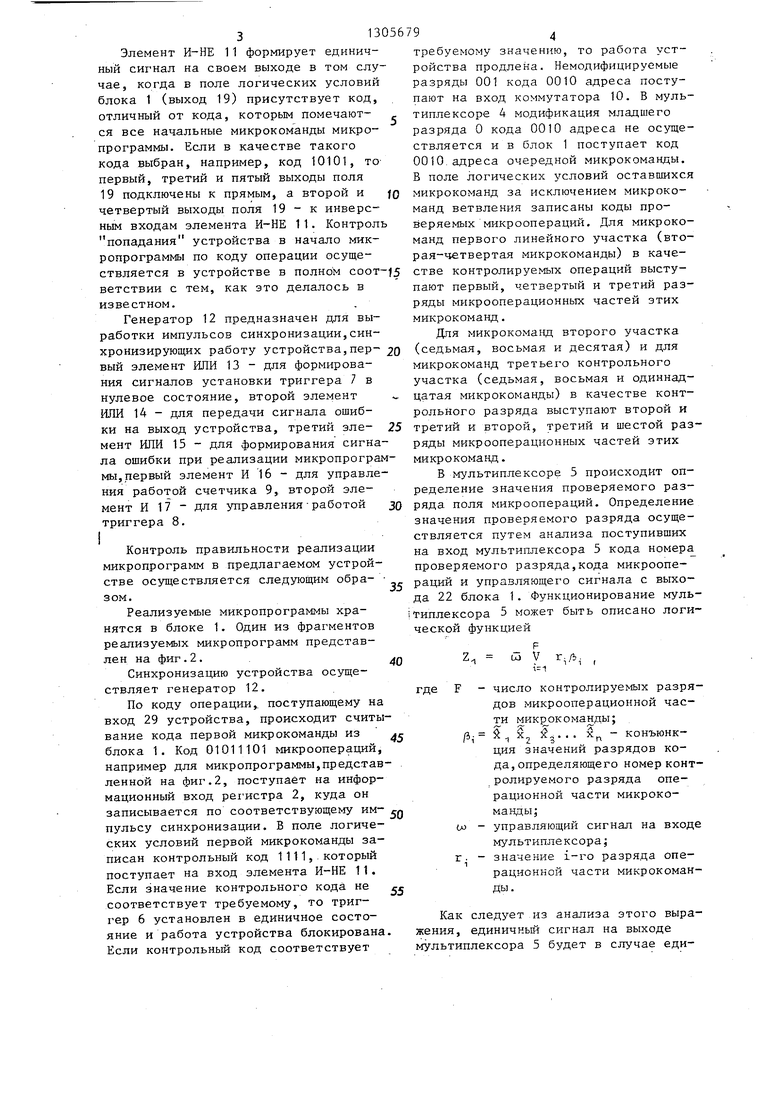

ная схема микропрограммного устройства управления с контролем; на фиг.2 - фрагмент микропрограммы.

Микропрограммное устройство управления с контролем (фиг.1)ссодер- жит блок 1 памяти микрокоманд, регистры микроопераций 2 и адреса 3,первый 4 и второй 5 мультиплексоры, триггеры 6-8, счетчик 9, коммутатор 10 адреса, элемент И-НЕ 11, генератор 12 тактовых импульсов, элементы ИЛИ 13-15, первый и второй элементы И 16 и 17 соответственно, поле 18 микроопераций, поле 19 логических условий, поле 20 немрдифицируемых разрядов адреса, поле 21 модифицируемого разряда адреса, поле 22 первой Метки (метки логических условий), поле 23 второй метки (метки микроко- манд вхождения в цикл и микрокоманд окончания контролируемых участков) блока памяти микрокоманд, выход 24 микроопераций устройства, выход 24.1 признака конца команды и выход 24.2 признака конца работы регистра 2, вход 25 пуска устройства, первый и второй выходы 26 и 27 соответственно генератора 12 тактовых импульсов, вход 28 кода значений логических условий устройства, вход 29 кода операции устройства, выход 30 отказа устройства.

Дисциплина функционирования микропрограммного устройства-управления с контролем заключается в следующем .

Счетчик перед реализацией микропрограммы настраивается на некоторый модуль. Микрокоманды ветвления имеют метку ветвления равную единице . Все остальные команды имеют метку ветвления равную нулю. Микрокоманды вхождения в цикл и микрокоманды конца контрольного участка также имеют соответствующую метку равную единице. Все остальные микрокоманды микропрограммы имеют метку вхождения в цикл равную нулю. При реализации линейных микрокоманд в поле логических условий записываются коды номеров контролируемых разрядов операционных частей микрокоманды. Определение значения контролируемого разряда осуществляете вторым мультиплексором. После считывания кода микрокоманды из бхгока памяти микрокоманд происходит запись ее операционной части в регистр микроопераций. Код

коммутатор адреса в регистр адреса и далее на вход блока памяти. В то же время второй мультиплексор осуществляет проверку значения соответствующего разряда кода операционной части микрокоманды. При этом единичном его значении содержимое счетчика увеличивается на единицу. При реализации микрокоманды, в которой метка вхождения в цикл равна единице, происходит определение состояния счетчика. При правильном функционировании предлагаемого устройства значение счетчика равно нулю. В противном случае - отлично от нуля. В случае, когда содержимое счетчика отлично от нуля, третий триггер установлен в единицу, и устройство прекращает реализацию заданного алгоритма. В случае отсутствия отказов работа устройства продолжается .

Блок 1 памяти микрокоманд предназначен для хранения реализуемых микропрограмм. Регистр 2 микроопераций для хранения кодов микрооперационных частей реализуемых мирокоманд, регистр 3 адреса - для хранения кодов адресов микрокоманд, мультиплексор 4 - для модификации младших разрядов

кодов адресов микрокоманд условных переходов, мультиплексор 5 - для определения значений контролируемых разрядов микрооперационных чайтей микрокоманд, триггер 6 - для фиксации отказа при неправильном выборе микропрограммы по коду операции. Триггер 7 предназначен для управления работой генератора 12, триггер 8 - для фиксации отказа при неправильной реализации микрокоманд микропрограммы, счетчик 9 - для определения числа контрольных микроопераций на контролируемом участке микропрограммы, коммутатор 10 адреса для передачи кодов адресов микрокоманд .

Элемент И-НЕ 11 - для формирования сигнала ошибок при неправильном выборе микропрограммы по коду операции.

Элемент И-НЕ 11 формирует единичный сигнал на своем выходе в том случае, когда в поле логических условий блока 1 (выход 19) присутствует код, отличный от кода, которым помечаются все начальные микрокоманды микропрограммы. Если в качестве такого кода выбран, например, код 10101, то первый, третий и пятый выходы поля 19 подключены к прямым, а второй и четвертый выходы поля 19 - к инверсным входам элемента И-НЕ 11. Контроль попадания устройства в начало микропрограммы по коду операции осуществляется в устройстве в полном соответствии с тем, как это делалось в известном.

Генератор 12 предназначен для выработки импульсов синхронизации,синхронизирующих работу устройства,пер- 20 (седьмая, восьмая и десятая) и для

вый элемент ИЛИ 13 - для формирования сигналов установки триггера 7 в нулевое состояние, второй элемент ИЛИ 14 - для передачи сигнала ошибки на выход устройства, третий эле- 25 мент ИЛИ 15 - для формирования сигнала ошибки при реализации микропрограммы, пер вый элемент И 16 - для управления работой счетчика 9, второй элемент И 17 - для управленияработой ЗО триггера 8.

Контроль правильности реализации микропрограмм в предлагаемом устройстве осуществляется следующим образом.

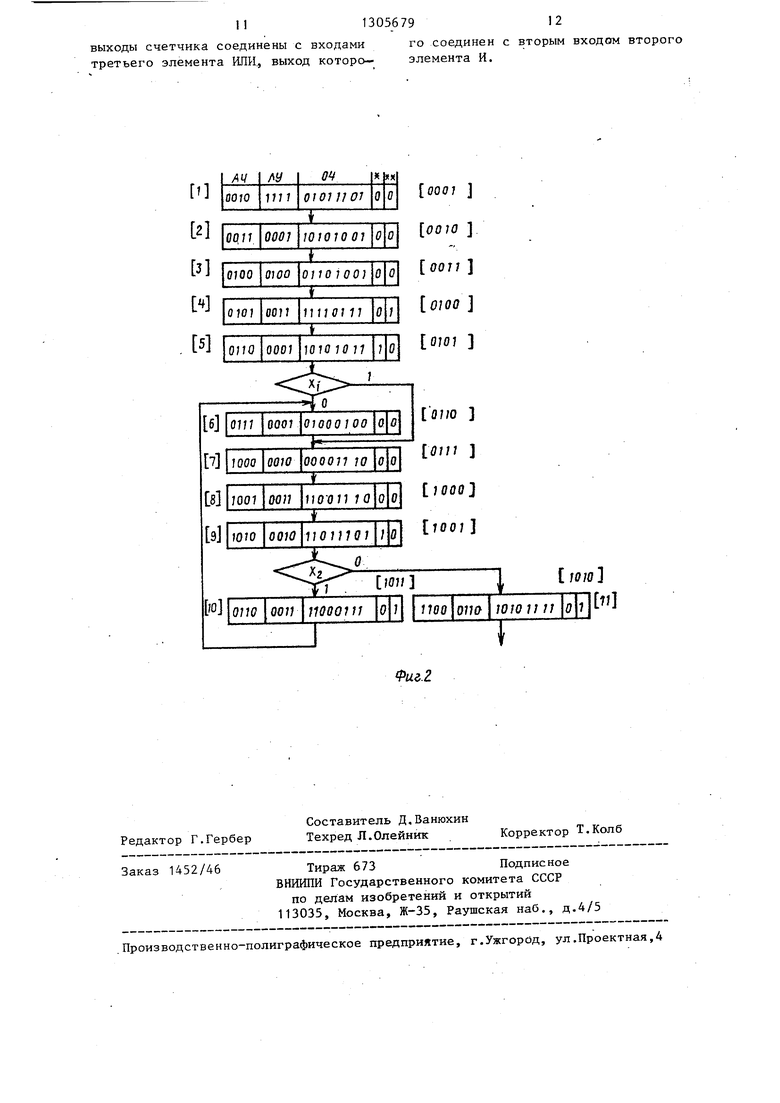

Реализуемые микропрограммы хранятся в блоке 1. Один из фрагментов реализуемых микропрограмм представлен на фиг.2.

Синхронизацию устройства осуществляет генератор 12.

По коду операции,, поступающему на вход 29 устройства, происходит считывание кода первой микрокоманды из с блока 1. Код 01011101 микроопераций, например для микропрограммы,представленной на фиг.2, поступает на информационный вход рех истра 2, куда он записывается по соответствующему им- jg пульсу синхронизации. В поле логических условий первой микрокоманды записан контрольный код 1111,.который поступает на вход элемента И-НЕ 11. Если значение контрольного кода не соответствует требуемому, то триггер 6 установлен в единичное состояние и работа устройства блокирована Если контрольный код соответствует

35

40

микрокоманд третьего контрольного участка (седьмая, восьмая и одиннад цатая микрокоманды) в качестве конт рольного разряда выступают второй и третий и второй, третий и шестой ра ряды мнкрооперационных частей этих микрокоманд.

В мультиплексоре 5 происходит оп ределение значения проверяемого раз ряда поля микроопераций. Определени значения проверяемого разряда осуще ствляется путем анализа поступивших на вход мультиплексора 5 кода номер проверяемого разряда,кода микроопераций и управляющего сигнала с выхо да 22 блока 1. Функционирование мул |Типлексора 5 может быть описано лог ческой функцией

2,

ы

i

где

х - конъюнк55

F - число контролируемых разр дов микрооперационной час ти микрокоманды;

ft. и, 5. и,.

ция значений разрядов кода, определяющего номер кон ролируемого разряда операционной части микрокоманды;

управляющий сигнал на вход мультиплексора; значение i-ro разряда операционной части микрокоман ды.

Как следует из анализа этого выра жения, единичньй сигнал на выходе мультиплексора 5 будет в случае едиto г. требуемому значению, то работа устройства продлена. Немодифнцируемые разряды 001 кода 0010 адреса поступают на вход коммутатора 10. В мультиплексоре 4 модификация младшего разряда О кода 0010 адреса не осуществляется и в блок 1 поступает код 0010.адреса очередной микрокоманды. В поле логических условий оставагихся микрокоманд за исключением микрокоманд ветвления записаны коды проверяемых микроопераций. Для микрокоманд первого линейного участка (вто- рая-четвертая микрокоманды) в качестве контролируемых операций выступают первый, четвертый и третий разряды микрооперационных частей этих микрокоманд.

Для микрокоманд второго участка

микрокоманд третьего контрольного участка (седьмая, восьмая и одиннадцатая микрокоманды) в качестве контрольного разряда выступают второй и третий и второй, третий и шестой разряды мнкрооперационных частей этих микрокоманд.

В мультиплексоре 5 происходит определение значения проверяемого разряда поля микроопераций. Определение значения проверяемого разряда осуществляется путем анализа поступивших на вход мультиплексора 5 кода номера. проверяемого разряда,кода микроопераций и управляющего сигнала с выхода 22 блока 1. Функционирование муль- |Типлексора 5 может быть описано логической функцией

40

2,

ы

i

сg

где

х - конъюнк5

F - число контролируемых разрядов микрооперационной части микрокоманды;

ft. и, 5. и,.

ция значений разрядов кода, определяющего номер контролируемого разряда операционной части микрокоманды;

управляющий сигнал на входе мультиплексора; значение i-ro разряда операционной части микрокоманды.

to г. Как следует из анализа этого выражения, единичньй сигнал на выходе мультиплексора 5 будет в случае еди5 1305679 ничного значения контролируемого разряда операционной части микрокоманды при со 0. Во всех остальных случаях Z О,

При единичном значении контроли- руемого разряда микрооперационнсзй части микрокоманды происходит увеличение на единицу сЬдержимого счетчика 9. Счетчик 9 настроен на некоторый модуль (имеет коэффициент пере- счета), равный числу единичных контролируемых разрядов микрооперационных частей микрокоманд на контролируемом участке. При реализации микрокоманды вхождения в дики или кон- трольной микрокоманды значения сигнала на выходе 23 блока 1 равно единице. Б случае микропрограммы, изображенной на фиг.2, в качестве контрольных микрокоманд выступают четвертая, десятая и одиннадцатая микрокоманды. Если содержимое счетчика 9 равно нулю, то это говорит о правильном функционировании устройства на контролируемом участке микропро- граммы. Если содержимое счетчика 9 равно нулю, то работа устройства продолжена. Далее при реализации мирокоманды ветвления значение сигнал на выходе 22 блока 1 равно единице. В поле логических условий записан код 0001 номера проверяемого логического условия. На вход 23 устройств поступает значение проверяемого логического условия. В мультиплексоре 4 в зависимости от значений логических условий происходит модификация значения младшего разряда кода адреса.

Особенностью модификаций младшег разряда кода адреса является то, чт модификация адреса не происходит пр нулевом коде номеров логических условий и при коде, которым отмечены все начальные микрокоманды микропрограммы. Поэтому логическая функция, реализуемая мультиплексором 4, имеет вид

де

)(к

а„ - младший разряд

1

/5,, X

XjX.j.

.X,

(модифицируемый) кода адоеса;

-значения логических условий;

-конъюнкция значений разрядов ну.левого кода ло

5 5

/JH

х..

гических условий;

конъюнкция значений разрядов кодов, которым отмечены начальные микрокоманды; конъюнкция значений разрядов кода логических условий.

Из приведенной формулы следует, что при нулевом коде логических условий или при коде, которым отмечены начальные микрокоманды Z о

Во всех остальных случаях происходит модификация разряда а таким обесли на вход муль7

1

разом,что

типлексора поступает j-й код логи0 ческих условий. Так, например, в случае проверки логического условия с номером 0001 при Х 1 осуществлена модификация младшего разряда адре- . са а путем изменения его значения с О на 1.

Аналогично выполнена модификация адреса при выполнении второй микрокоманды ветвления с кодом логических условий 0010. В этом случае при Х2

0 1 (младший разряд а адреса модифицирован путем изменения его значения с О на 1. При Х2 О модификация не производится).

Для микропрограммы, изображенной

5 на фиг.2, в качестве модуляпересчета выбрано число три. При правильном функционировании устройства при выполнении контрольных микрокоманд (четвертой, десятой .или одиннадца0 той) значение счетчика 9 должно быть равно нулю. Невыполнение этого условия свидетельствует о возникновении отказа в работе устройства.

Микропрограммное устройство уп5 равления с контролем работает следующим образом.

В исходном состоянии все элементы памяти находятся в нулевом состоянии (цепи установки в нуль элементов

0 памяти на фиг.1 условно не показаны). Триггер регистра 2, которому соответствует выход 24.1 конца команды выхода регистра, находится в единичном состоянии (цепи его установки в еди55 ничное состояние, на фиг.1 условно не

показаны). 1.I

Работа устройства начинается с поступления на вход 25 устройства сигнала Пуск, по которому устанавливается в единичное состояние триггер 7, который разрешает работу генератора 12. По первому тактовому импуль- су с выхода 27 генератора в регистр 3 заносится код операции с входа 29 устройства. Этот код записывается в регистр 3 через коммутатор 10, на управляющий вход которого поступает единичный сигнал с выхода 24.1 ре- гистра 2. По тактовому импульсу с выхода 26 генератора 12 в регистр 2 записывается часть первой микрокоманды микропрограммы (операционная часть

По заднему фронту импульса синхрони- (5 Тогда работа мультиплексора 4 блокируется, а мультиплексор 5 определяет

зации на выходе 24.1 единичный сигнал исчезает и в триггер 6 записывается единичньм или нулевой сигнал. Единичньм сигнал формируется элементом И-НЕ 11 в том случае, если в поле логических условий первой микрокоманды (на выходе 19 блока 1) формируется код отличных от требуемого, соответствующего начальной микрокоманде микропрограммы. Тогда единичный сигнал с единичного выхода триггера 6 поступает через элемент ИЛИ 14 на вход 20 отказа устройства и через элемент ШШ 13 на R-вход триггера 7. В результате этого на выходе 30 устройства формируется сигнал отказа. Триггер 7 устанавливается в нулевое состояние и блокирует работу генератора 12.

значение контролируемого разряда. При его единичном значении на выходе мультиплексора 5 сформирован единич20 ный сигнал, который поступает на первый вход элемента И 16.По импульсу синхронизации с выхода 26 генератора 12 содержимое счетчика 9,становится равным единице.. При существовании

25 нулевых сигналов на выходах 22 и 23 блока 1 работа устройства продолжается по описанному выше алгоритму.

30

При реализации последней микрокоманды контролируемого участка или микрокоманды вхождения в цикл сигнал на выходе 23 блока 1 равен единице. Этот сигнал поступает на соответствующий вход элемента И 17. На другой В противном случае нулевое состоя- , вход элемента И 17 поступает сигнал ние триггера 6 не меняется и в рб- с выхода элемента ИЛИ 15. Этот сиг- гистр 3 по заднему фронту импульса нал единице, если содержимое синхронизации с выхода 27 генератора 12 записывается код адреса второй микрокоманды микропрограммы. Этот ад- Q чае, если на выходе элемента ИЛИ 15 рес поступает в регистр 3 с выхода присутствует единичный сигнал, что 20 (немодифицируемая часть) и с выхода 21 (модифицируемая часть) на коммутатор 10, на управляющий вход которого поступает нулевой сигнал с выхода 24,1 выхода регистра 2. При этом младший модифицируемый адресный разряд проходит на выход мультиплексора 4 и далее в регистр 3 адреса без изменения. С выхода регистра 3 адреса код адреса второй микрокоманды поступает на вход блока 1, и работа устройства продолжается следующим образом. Код операционной части микрокоманды поступает с выхода 18 бло- 5 если сигнал на выходе элемента ИЛИ 15 ка 1 на информационный вход регистра равен нулю, элемент И 17 закрыт и 2, куда и записывается по заднему работа устройства продолжается без фронту импульса синхронизации с вы- изменений по описанному выше апго- хода 26 генератора 12 и на вход муль- 1М1тму,

счетчика 9 отлично от нуля, и равен нулю в противном случае. В том слуговорит о возникновении отказа при реализации контролируемого участка микропрограммы, на выходе элемента

И 17 сформирован единичный сигнал, который поступает на информационный вход триггера 8. По импульсу синхронизации с выхода 27 генератора 12 триггер 8.установлен в единичное стояние, в результате чего на выходе 30 устройства сформирован единичный сигнал отказа,а триггер 7 установлен в нулевое состояние. Работа устройства заблокирована. Б том случае.

8

типлексора 5. Код номера проверяемого разряда операционной части микрокоманды поступает на входы мультиплексоров 4 и 5 и на вход элемента И-НЕ 11. Значение метки на выходе 22 блока 1 равно нулю, если вторая микрокоманда не является микрокомандой ветвления. Значение метки на выходе 23 блока 1 равно нулю, если вторая микрокоманда не является микрокомандой вхождения в цикл или конечной микрокомандой контролируемого участка. Предположим, что сигналы на выходах 22 и 23 блока 1 равны нулю.

значение контролируемого разряда. При его единичном значении на выходе мультиплексора 5 сформирован единичный сигнал, который поступает на первый вход элемента И 16.По импульсу синхронизации с выхода 26 генератора 12 содержимое счетчика 9,становится равным единице.. При существовании

нулевых сигналов на выходах 22 и 23 блока 1 работа устройства продолжается по описанному выше алгоритму.

30

, Q 5

При реализации последней микрокоманды контролируемого участка или микрокоманды вхождения в цикл сигнал на выходе 23 блока 1 равен единице. Этот сигнал поступает на соответствующий вход элемента И 17. На другой вход элемента И 17 поступает сигнал с выхода элемента ИЛИ 15. Этот сиг- нал единице, если содержимое чае, если на выходе элемента ИЛИ 15 присутствует единичный сигнал, что если сигнал на выходе элемента ИЛИ 15 равен нулю, элемент И 17 закрыт и работа устройства продолжается без изменений по описанному выше апго- 1М1тму,

счетчика 9 отлично от нуля, и равен нулю в противном случае. В том слуПри реализации последней микрокоманды контролируемого участка или микрокоманды вхождения в цикл сигнал на выходе 23 блока 1 равен единице. Этот сигнал поступает на соответствующий вход элемента И 17. На другой , вход элемента И 17 поступает сигнал с выхода элемента ИЛИ 15. Этот сиг- нал единице, если содержимое Q чае, если на выходе элемента ИЛИ 15 присутствует единичный сигнал, что 5 если сигнал на выходе элемента ИЛИ 15 равен нулю, элемент И 17 закрыт и работа устройства продолжается без изменений по описанному выше апго- 1М1тму,

говорит о возникновении отказа при реализации контролируемого участка микропрограммы, на выходе элемента

И 17 сформирован единичный сигнал, который поступает на информационный вход триггера 8. По импульсу синхронизации с выхода 27 генератора 12 триггер 8.установлен в единичное соQ стояние, в результате чего на выходе 30 устройства сформирован единичный сигнал отказа,а триггер 7 установлен в нулевое состояние. Работа устройства заблокирована. Б том случае.

9 13

В микрокомандах ветвления в поле логических условий записаны коды номеров проверяемых логических условий. Сигнал на выходе 22 блока 1 равен единице. Работа мультиплексора 5 в этом случае блокируется, а мультиплексора 4 разрешается. Мультиплексор 4 осуществляет модификацию младшего разряда кода адреса микрокоманды перехода в соответствии с реализуемой им логической функцией.

При считьшании последней микрокоманды реализуемой микропрограммы алгоритм работы устройства полностью аналогичен описанному алгоритму начальной фазы функционирования. После считывания в регистр 2 микроопераций кода конца работы устройства единичным сигналом с выхода 24.2 регистра 2 триггер 7 установлен в нулевое состояние и нулевым сигналом с единичного выхода блокирует работу генератора 12 и всего устройства в целом.

ормула изобретения 25

45

Микропрограммное устройство управления с контролем, содержащее блок памяти микрокоманд, регистр микроопераций, регистр адреса, первьй мультиплексор,коммутатор адреса,первый ивторой триггеры, элемент И-НЕ, генератор тактовых импульсов и пер- йый элемент ИЛИ, причем выход поля микроопераций блока памяти микрокоманд соединен с информационным входом регистра микроопераций, выход которого является выходом микроопераций устройства, выход признака конца работы регистра микроопераций соединен с первым входом первого элемента ИЛИ,а выход признака конца команды регистра микроопераций соединен с управляющим входом коммутатора адреса и входом синхронизации первого триггера, вход пуска устройства подключен к S-входу второго триггера, выход первого элемента ИЛИ соединен с R-входом второго триггера, единичньй выход которого соединен 50 счетчика, второй выход генератора

с входом пуска генератора тактовых импульсов, первьй выход генератора тактовых импульсов соединен с входом синхронизации регистра микроопераций, а второй выход генератора тактовых импульсов соединен с входом синхронизации регистра адреса, выходы поля логических условий блока памяти микрокоманд соединены с группой уп10

5

0

0

5

равляющих входов первого мультиплексора и входами элемента И-НЕ, вход кода значений логических условий устройства соединён с информационным входом первого муль- тигшексора,вход кода операции устройства подключен к первому информационному входу коммутатора адреса, выход поля модифицируемого разряда адреса блока памяти микрокоманд соединен с первым,управляющим входом первого мультиплексора, выход которого и выход поля немодифицируемых разрядов адреса блока памяти микрокоманд соединены с вторым информационным входом коммутатора адреса, выход которого соединен с информационным входом регистра адреса, выход регистра адреса соединен с адресным входом блока памяти микрокоманд, выход элемента И-НЕ соединен с информационным входом первого триггера, отличающееся тем, что, с целью повышения достоверности функционирования устройства, оно содержит второй мультиплексор, счетчик, третий триггер, первый и второй элементы И и второй и третий элементы ИЛИ,причем выход поля микроопераций блока памяти микрокоманд соединен с первым информационным входом второго мультиплексора, выход поля логических условий блока памяти микрокоманд соединен с вторым информационным входом второго мультиплексора, выход поля первой метки блока памяти микрокоманд соединен с управляющим входом второ го мультиплексора,и вторым управляющим входом первого мультиплексора, выход второго мультиплексора соединен с первым входом первого элемента И, выход поля второй метки блока пам яти микрокоманд соединен с первым входом второго элемента И, выход которого соеди- 5. нен с информационным входом третьего триггера, первый выход генератора тактовых импульсов соединен с вторым входом первого элемента И, выход которого соединен с счетным входом

5

0

тактовых импульсов соединен с входом синхронизации третьего триггера, единичный выход которого соединен с первым входом второго элемента ИЛИ,еди- ничньй выход первого триггера соединен с вторым входом второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента ИЛИ, и. является выходом отказа устройства.

выходы счетчика соединены с входами го соединен с вторым входом второго третьего элемента ИЛИ., выход которо- элемента И.

Редактор Г.Гербер

Составитель Д.Ванюхин

Техред Л.Олейник Корректор Т.Колб

Заказ 1452/46

Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1180888A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1365082A1 |

| Программируемый контроллер | 1990 |

|

SU1714599A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Микропрограммный модуль | 1986 |

|

SU1427366A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1376084A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в ЭВМ и вычислительных системах с микропрограм- MHbiM принципом управления. Изобретение позволяет повысить достоверность функционирования микропрограммных устройств управления с контролем за счет увеличения оперативности и полноты контроля путем проверки по модулю последовательностей микрокоманд микропрограммы на основе мультиплексирования их микрооперационных частей. . Устройство содержит блок памяти микрокоманд 1, регистры микроопераций 2 и адреса 3, мультиплексоры 4 и 5, счетчик 9, коммутатор адреса 10, генератор 12 тактовых импульсов, триггеры 6-8, элементы ИЛИ 13 - 15, элементы И 16 и 17, элемент И-НЕ 11, поле 18 микроопераций, поле 19 логических условий, поле 20 немодифицируемых разрядов адреса, поле 21 модифицируемого разряда адреса, поля первой 22 и второй 23 меток блока памяти микрокоманд 1. 2 ил. 3 (Я со ел Oi со

| Авторское свидетельство СССР № 849894, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-23—Публикация

1986-01-29—Подача