его элемента И соединен со счетным входом счетчика, инверсные выходы которого соединены с входами четвертого элемента И, выходы пятого и шестого элементов И соединены соответствен но с первым и вторым входами блока анализа, первый выход которого является выходом ошибки рабочего канала устройства, отличающееся тем, что, с целью повышения достоверности функционирования, в устройство дополнительно введены буферный регистр, коммутатор, первая и вторая схемы сравнения, мультиплексор, триггер хранения логического условия, сумматор по модулю два, первый и второй одновибраторы, второй элемент ИЛИ причем вход пуска устройства соединен с первым.входом второго элемента ИЛИ, выход которого через первый одновибратор соединен с первьм входом первого элемента ИЛИ, выход четвертого элемента И через второй одновибратор соединен с вторым входом первого элемента ИЛИ, выходы кода логических условий и микроопераций регистра рабочих микрокоманд соединены соответственно с первым и вторым информационными входами коммутатора, первый и второй выходы которого соединены соответственно с первым и вторь1М входами первой схемы сравнения, выход первой схемы сравнения соединен с третьим входом блока анализа, второй и третий выходы которого соединены с выходами ошибок контрольного канала и ошибки средств контроля устройства соответственно, выход микроопераций регистра контрольных микрокоманд соединен с третьим информационнь1м (ВХОДОМ коммутатора и первым входом второй схемы сравнения, выход которой соединен с вторым входом пятого элемента И, выход второго блока элементов И соединен с четвертым информационным входом коммутатора, выход первой метки регистра контрольных микрокоманд соединен с первым управляющим входом коммутатора, первым входом шестого элемента И, входом синхронизации буферного регистра и вторым входом первого блока элементов И, выход которого соединен с информационным входом счетчика, выход второй метки регистра контрольных

0625

микрокоманд соединен с вторым управляющим входом коммутатора, вторыми входами пятого элемента И и второго элемента ИЛИ и с входом синхронизации триггера хранения логического условия, единичный выход которого соединен с первым входом сумматора по модулю два, выход требуемого значения логического условия регистра контрольных микрокоманд соединен с вторым входом сумматора rto модулю два, выход которого соединен с вторым входом шестого элемента И, выход кода логических условий регистра контрольных микрокоманд и вход логических условий устройства соединены

соответственно с управляющем и информационным выходом мультиплексора, выход которого соединен с информационным входом триггера хранения логического условия, выход адреса регистра контрольных микрокоманд соединен с информационным входом буферного регистра, выход которого соединен с вторьм входом второй схемы сравнения.

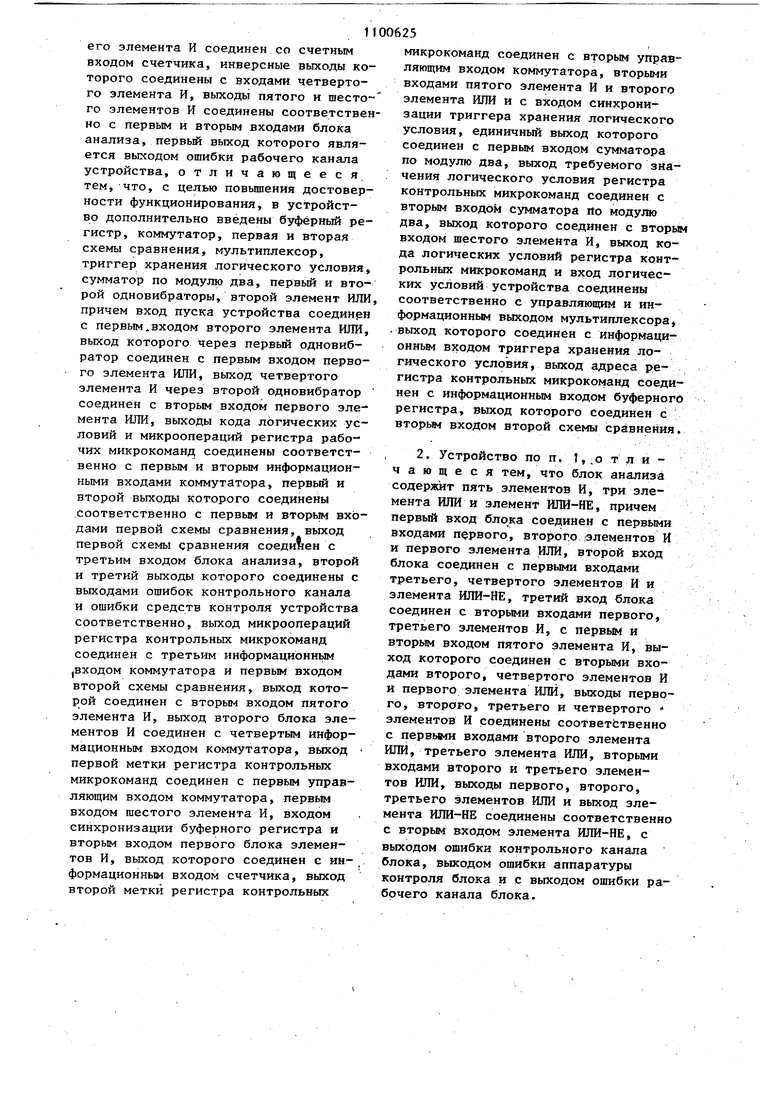

, 2. Устройство по п. 1,.о т л и ч а ю щ е с я тем, что блок анализа содержит пять элементов И, три элемента ИЛИ и элемент ИЛИ-НЕ, причем первьА вход блока соединен с первыми входами первого, второго элементов И и первого элемента ИЛИ, второй вход блока соединен с первыми входами третьего, четвертого элементов И и элемента ИЛИ-НЕ, третий вхоД блока соединен с вторыми входами первого, третьего элементов И, с первым и вторым входом пятого элемента И, выход которого соединен с вторыми входами второго, четвертого элементов И и первого элемента ИЛИ, выходы первого, второго, третьего и четвертого элементов И соединены соответственно с первьии входами второго элемента ИЛИ, третьего элемента ИЛИ, вторыми входами второго и третьего элементов ИЛИ, выходы первого, второго, третьего элементов ИЛИ и выход элемента ИЛИ-НЕ соединены соответственно с вторым входом элемента ИЛИ-НЕ, с выходом ошибки контрольного канала блока, выходом ошибки аппаратуры контроля блока и с выходом ошибки рабочего канала блока.

Изобретение относится к автоматике и вычислительной технике и может быть использов;но при построении самопроверяемых микропрограммных управляющих устройств л высокой достоверностью функционирования.

Известно микропрох раммное устрой- . ство управления с самоконтролем, содержащее регистр команд, регистр адресов микрокоманд, дешифра:тор адресов

микрокоманд, счетчик микрошагов, блок памяти микрокоманд, блок памяти контрольных микрокоманд, регистр контрольных микрокоманд, блок формирования ошибки, блок разрешения контроля tl3. Недостатком .данного устройства являются низкие функциональные возможности, обусловленные невозможностью идентификации сбоя между ветвлением и линией последовательностью микрокоманд, возможностью использования микрокоманд с одной и той же операци онной частью в качестве первой микро команды только в одной линейной последовательности г требованием, чтобы логические условия не входили в распределение сдвигов ни одной микрокоманды линейной последовательности, кроме первой. наиболее близким по технической сущности к изобретению является самоконтролируемое микропрограммное устройство управления, содержащее регистр адреса контрольных микрокоманд, дешифратор (формирователь) адреса контрольных микрокоманд, первый чётвертый элементы И, элвмент ИЛИ, элемент НЕ, формирователь адреса мик рокоманд и последовательно соединенные блок памяти контрольных микрокоманд , первый выход которого подключен к первому входу блока формирован ошибки (схемы анализа), которого является выходом устройства, второй вход подключен к выходу блока разрешения контроля, первый вход которого дешифратор микрошагов подключен к выходу счетчика микрошагов, второй вход блока разрешения контроля (группа элементов).йодключе к первому входу устройства и через последовательно включенные регистр; команд, регистр адресов микрокоманд, дешифратор адресов микрокоманд, блок памяти микрокоманд ко входу регис ра микрокоманд, второй выход которого подключен к третьему входу блока формирования ошибки, первый вход фор

мирователя адреса микрокоманд соединен с первым выходом регистра микрокоманд, третий выход которого соединен с вторьм входом формирователя адреса микрокоманд, выход которого соединен с вторым входом регистра адреса микрокоманд, третий вход формирователя адреса микрокоманд соединен с вторым входом устройства и

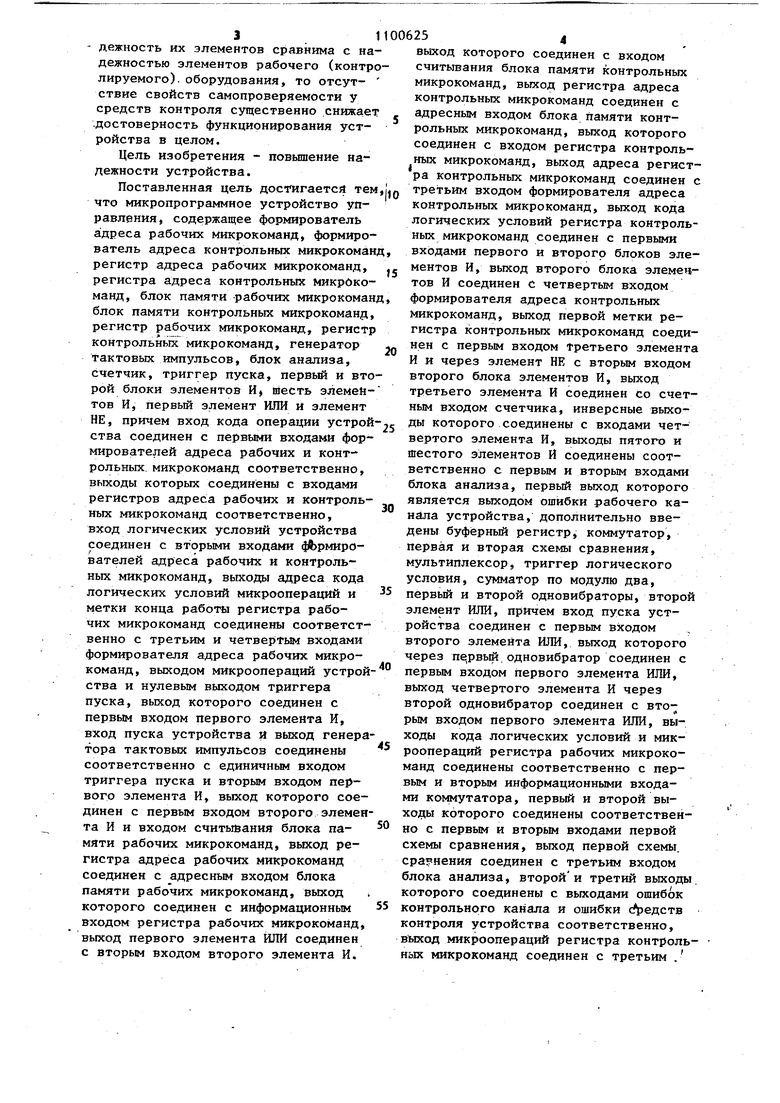

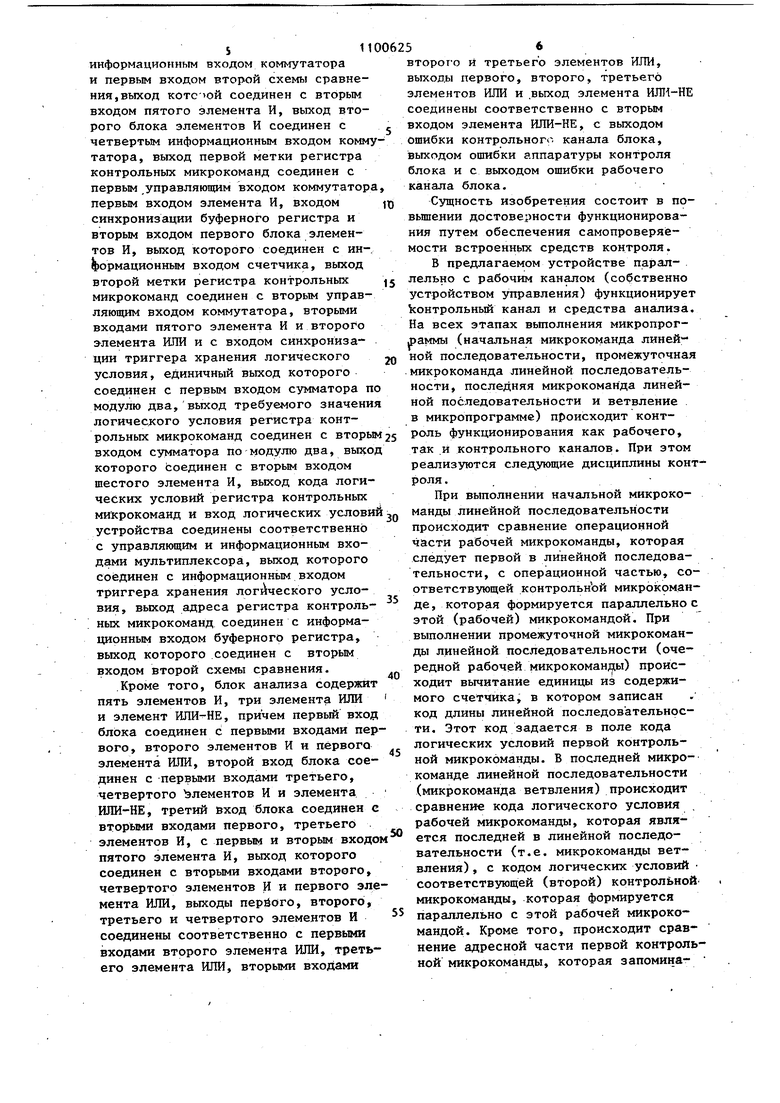

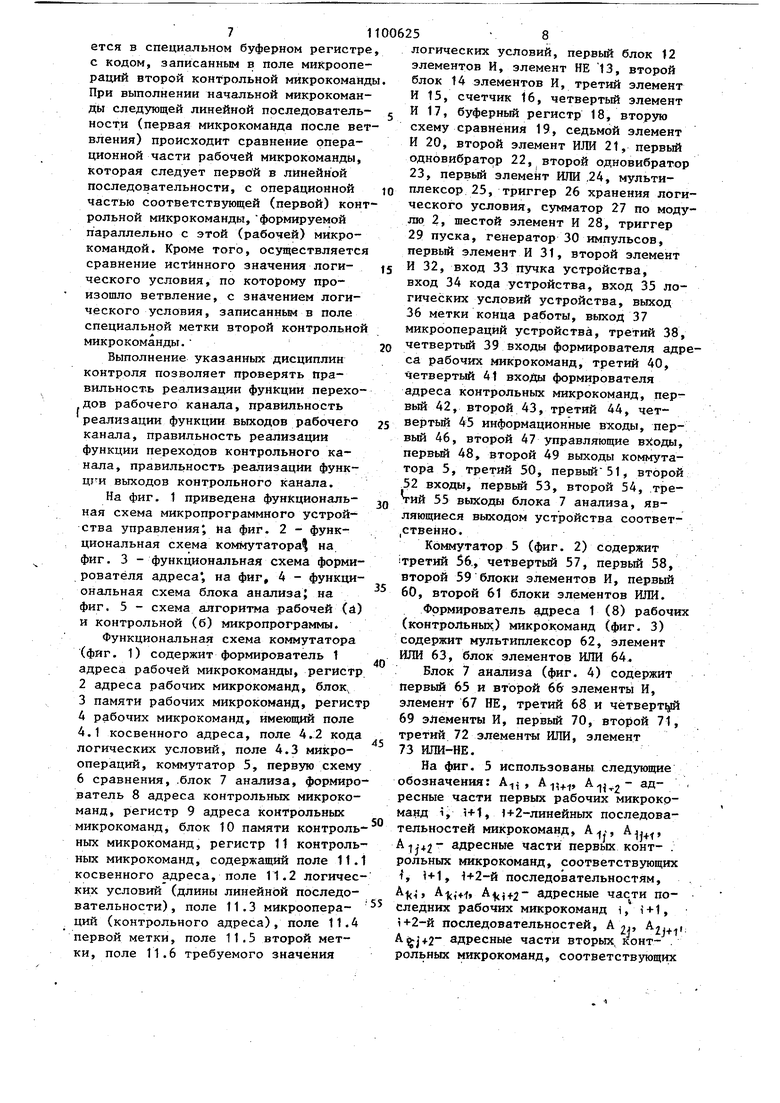

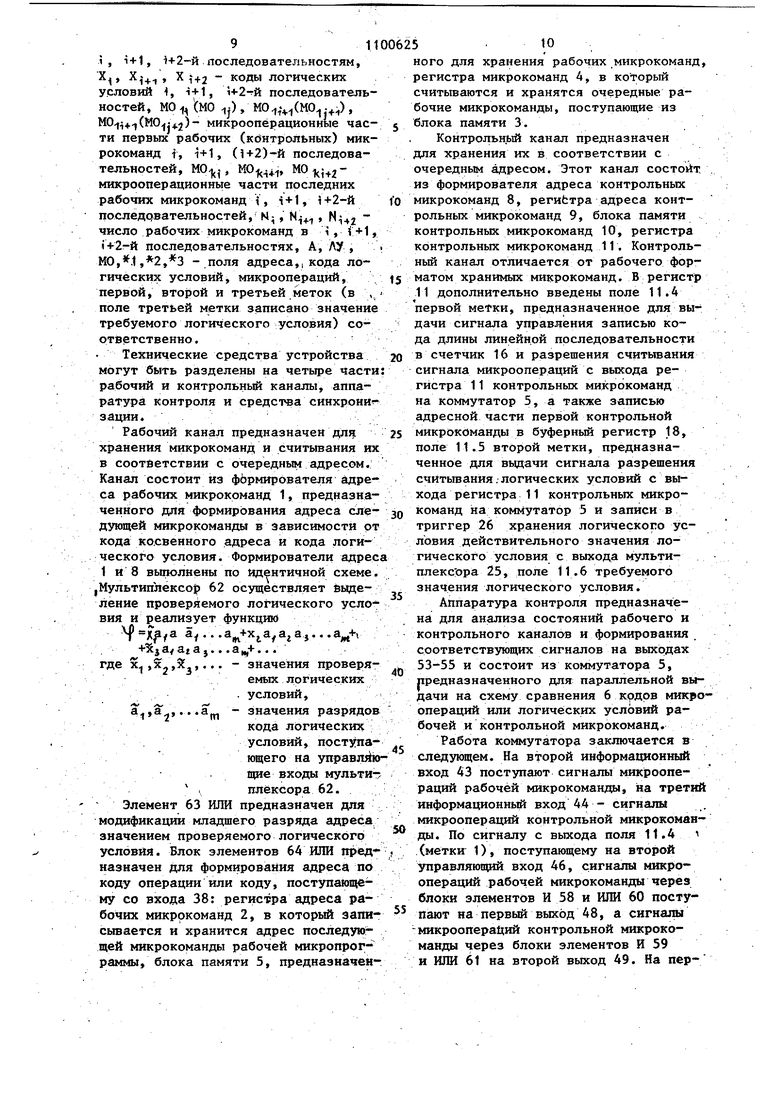

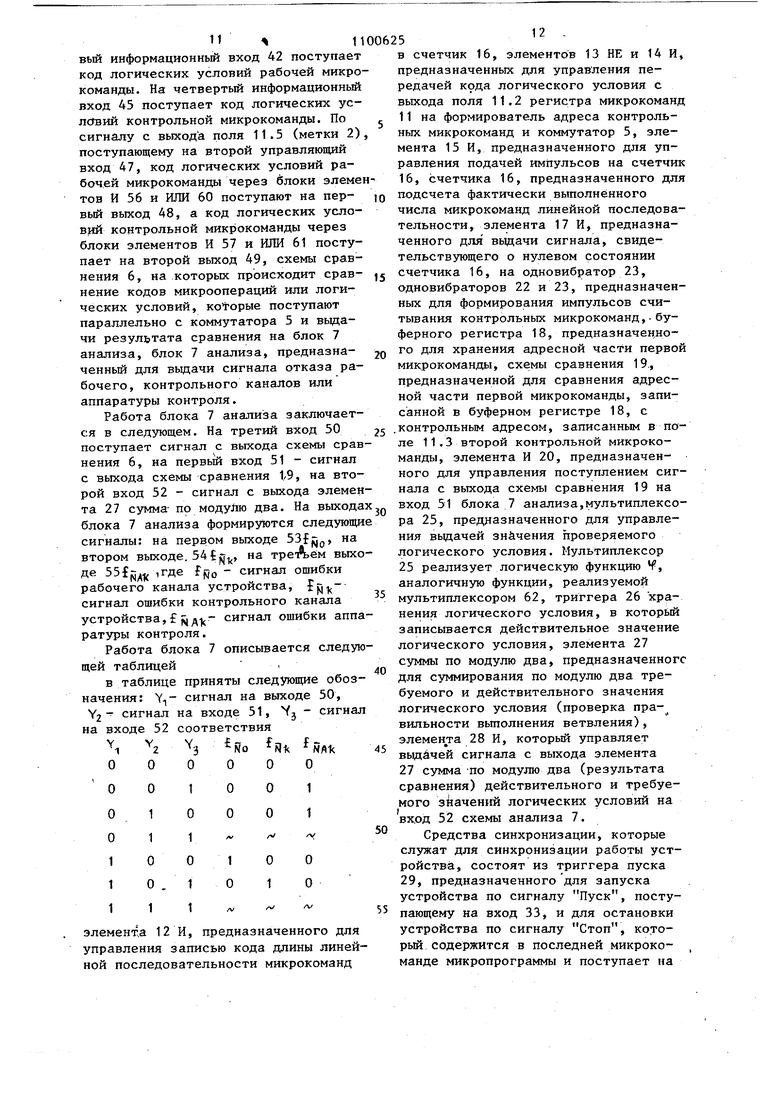

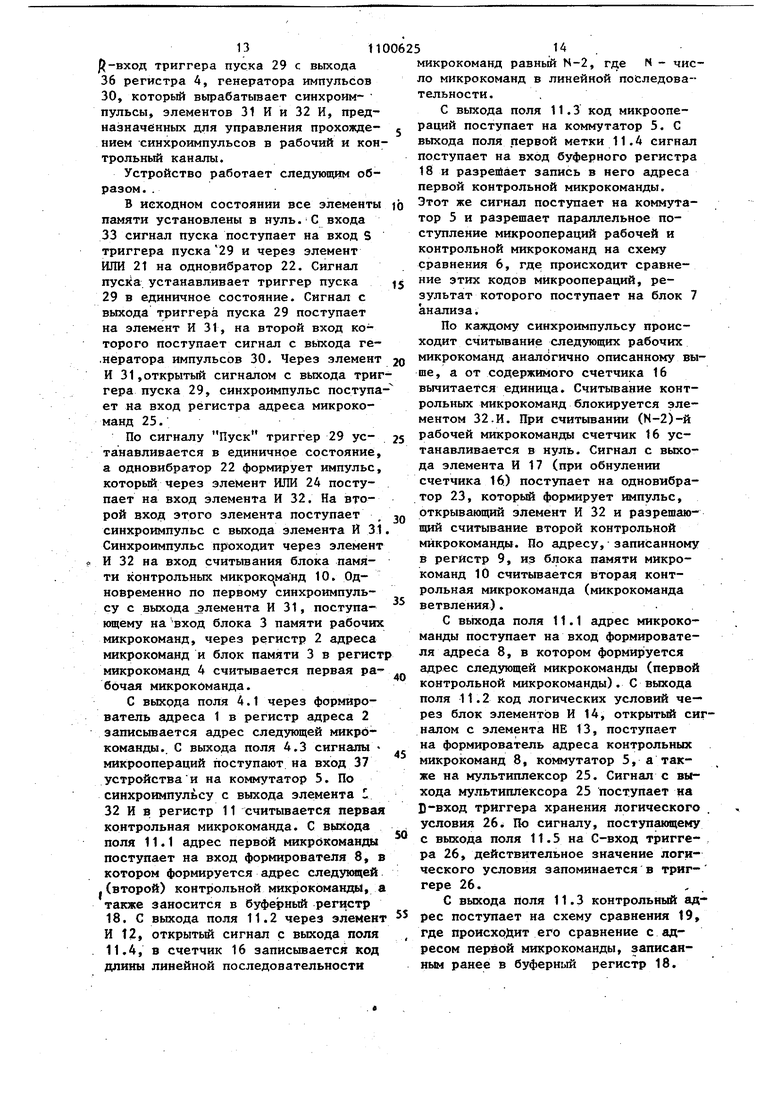

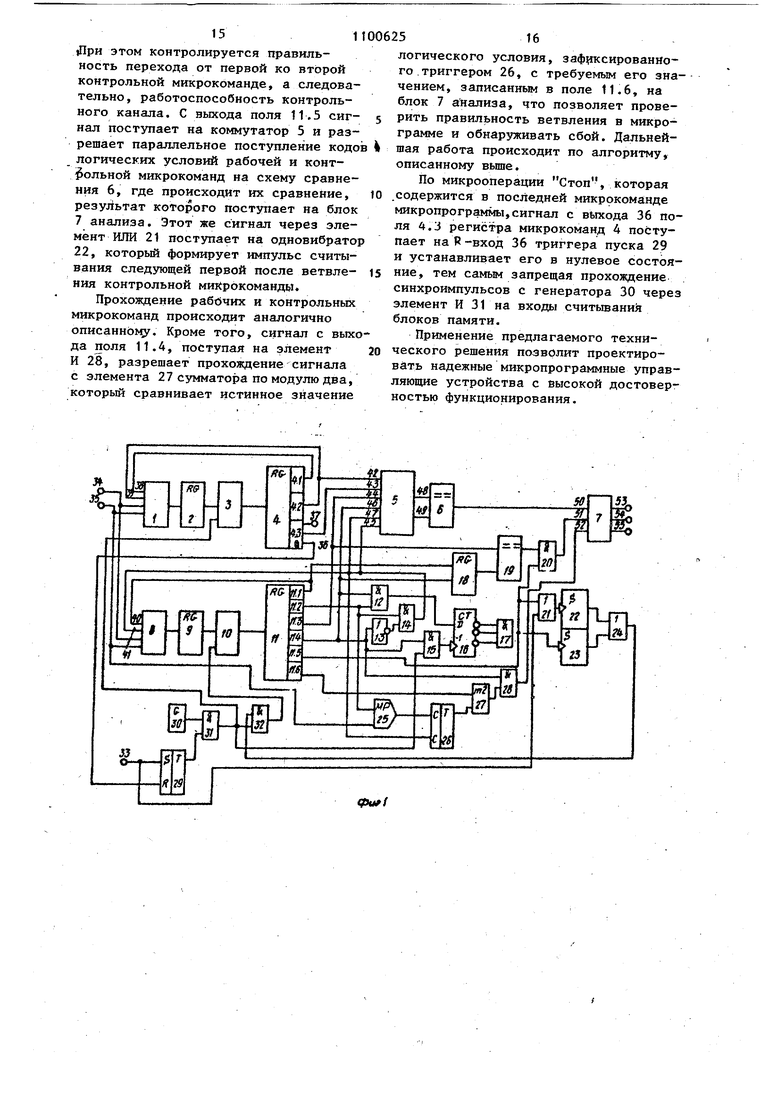

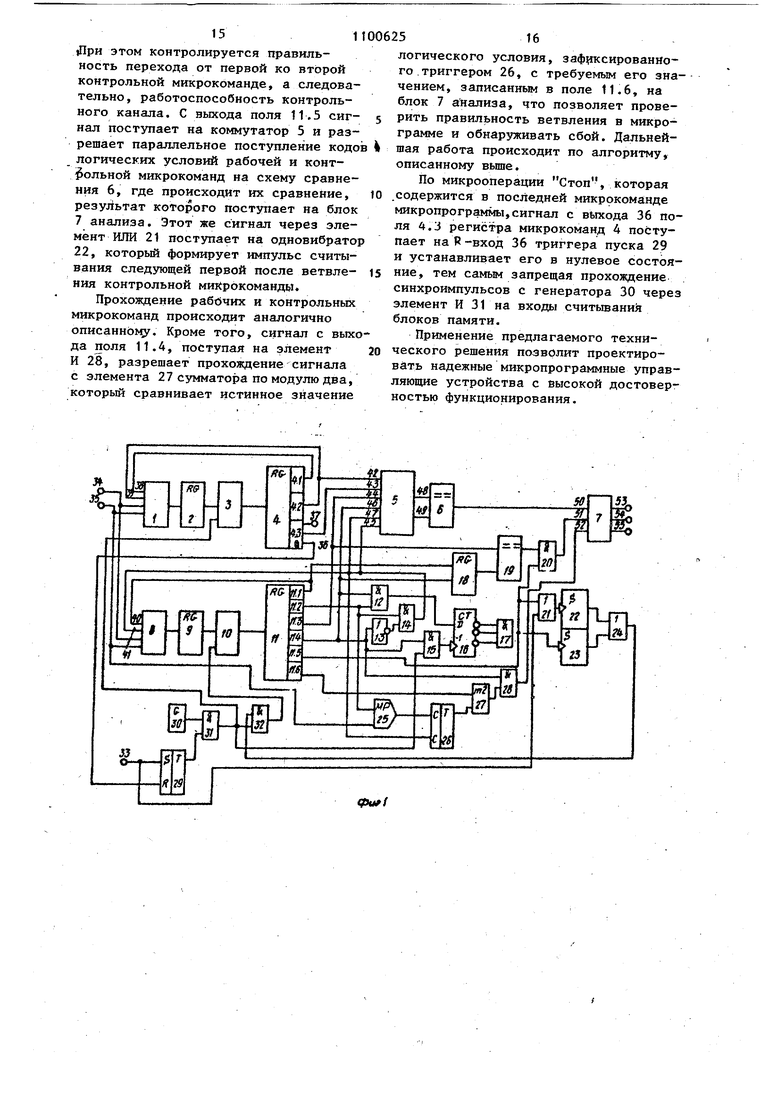

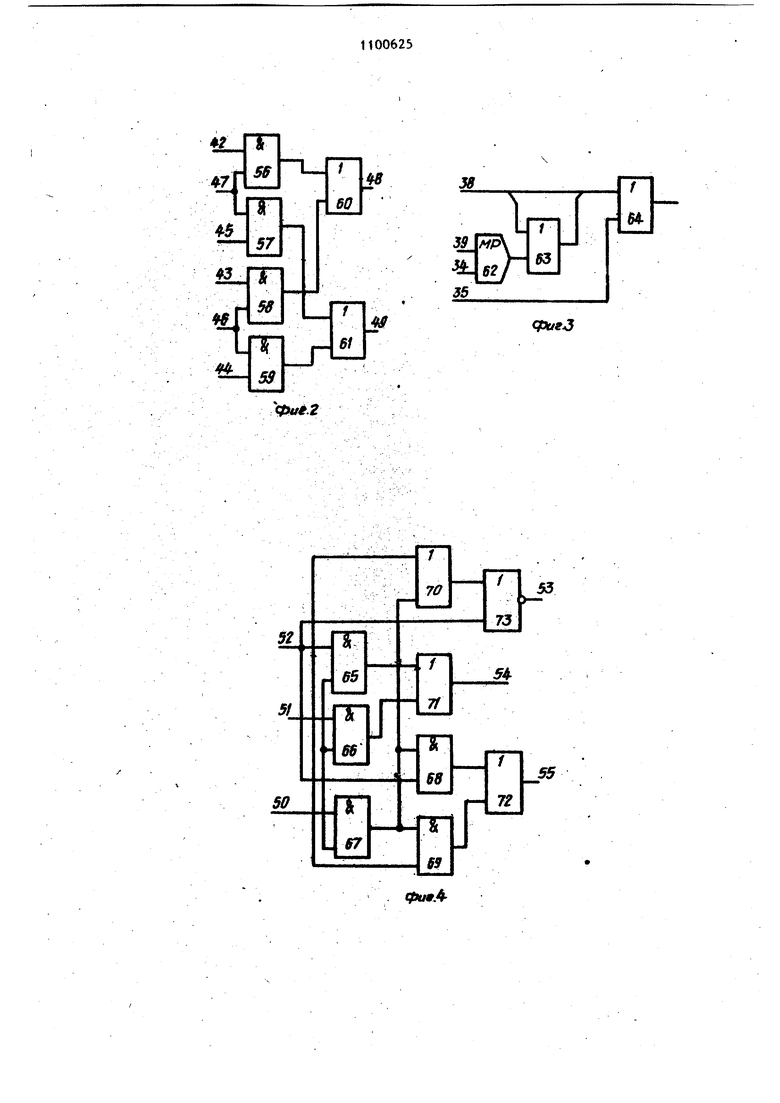

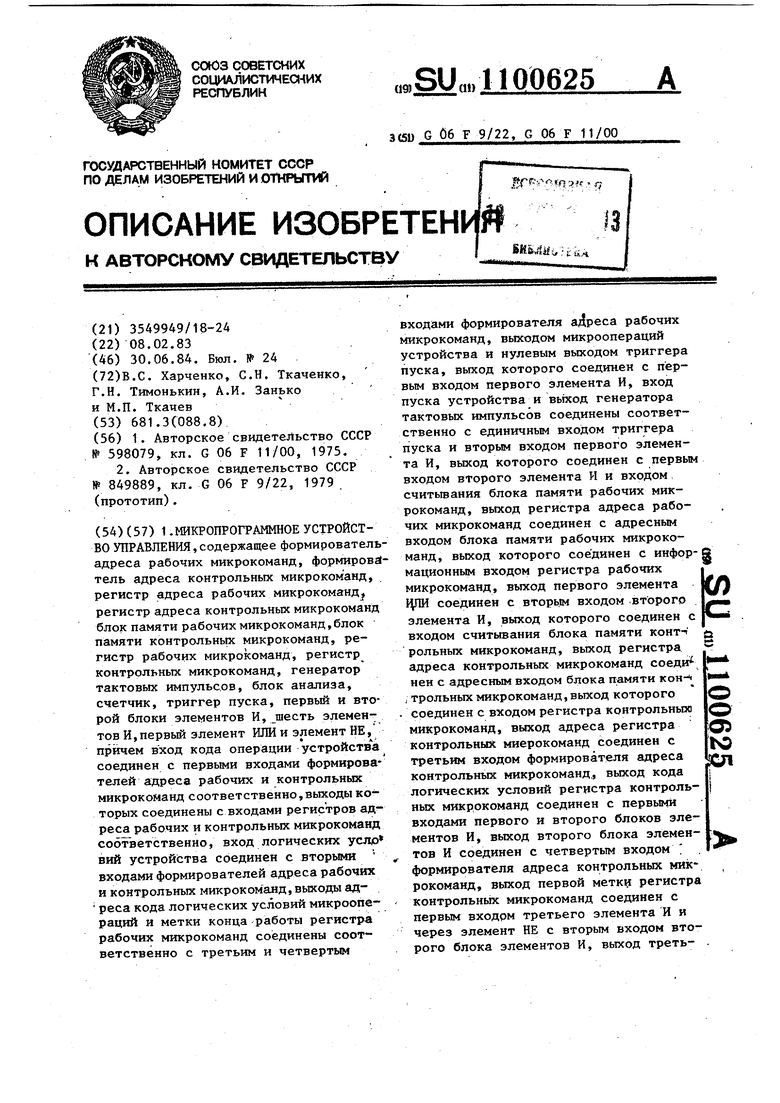

контрольных микрокоманд, второй вход которого подключен ко второму выходу регистра контрольных микрокоманд, четвертый выход которого через элепервым входом формирователя адреса мент .НЕ подключен ко входу первого элемента И, управляемого третьим входом устройства, и к .первому входу второго элемента И, второй вход которого подключен к трет: ему выходу регистра контрольных микрокрманд и Первому входу третьего элемента И управляемого четвертым выходом ре гистра контрольных микрокоманд, выход третьего элемента И подключен к первому входу счетчика микрошагов, а выход второго элемента И подключен к третьему входу формирователя адреса контрольных, микрокоманд,, выход ko,торого подключен ко второму входу регистра адреса контрольных микрокоманд, первый вход которого подключен ко второму выходу регистра команд, а выход - к первому входу-дешифратора адреса контрольных микрокоманд, а второй вход подключен к выходу элемента ИЙИ, первый вход которого подк.шочен к выходу первого элемента И, а второй вход подключен к выходу четвертого элемента И, первый вход которого соединен с выходом дешифратора микрошагов, а второй вход подключен ко второму входу дешифратора адреса микрокоманд, третьему входу устройства, второму входу счетчика микрошагов и второму входу первого элемента И и третьему входу блока разрешения контроля С23. . Недостатком указанного устройства является низкая достоверность функционирования и, как следствие, низкая надежность, поскольку средства контроля в нем не являют ;я самопроверяёмыми, а их отказ или идентифицируется как отказ контролируемого микропрограммного устройства или приводит к тому, что действительный отказ проверяемой части не обнаруживается. Так как объем средств контроля в прототипе составляет 20-25% я на- дежность их элементов сравнима с на дежностью элементов рабочего (контр лируемого), оборудования, то отсутствие свойств самопроверяемости у средств контроля существенно снижае .достоверность функционирования устройства в целом. Цель изобретения - повьшение надежности устройства. Поставленная цель достигается тем что микропрограммное устройство управления, содержащее формирователь адреса рабочих микрокоманд, формиро ватель адреса контрольных микрокоман регистр адреса рабочих микрокоманд, регистра адреса контрольных микрокоманд, блок памяти рабочих микрокоман блок памяти контрольных микрокоманд регистр рабочих микрокоманд, регистр контрольных микрокоманд, генератор тактовых импульсов, блок анализа, счетчик, триггер пуска, первый и вто рой блоки элементов И шесть элемейтов И, первый элемент ИЛИ и элемент НЕ, причем вход кода операции устрой ства соединен с первыми входами формирователей адреса рабочих и конт рольных, микрокоманд соответственно, выходы которых соединены с входами регистров адреса рабочих и контрольных микрокоманд соответственно, вход логических условий устройства соединен с вторыми входами с|й)рмирователей адреса рабочих и контрольных микрокоманд, выходы адреса кода логических условий микроопераций и метки конца работы регистра рабочих микрокоманд соединены соответственно с третьим и четвертым входами формирователя адреса рабочих микрокоманд, выходом микроопераций устрой ства и нулевым выходом триггера пуска, выход которого соединен с первым входом первого элемента И, вход пуска устройства и выход генера тора тактовых импульсов соединены соответственно с единичным входом триггера пуска и вторым входом первого элемента И, выход которого соединен с первым входом второго элемен та И и входом считывания блока памяти рабочих микрокоманд, выход регистра адреса рабочих микрокоманд соединен с адресным входом блока памяти рабочих микрокоманд, выход которого соединен с информационным входом регистра рабочих микрокоманд, выход первого элемента ИЛИ соединен с вторым входом второго элемента И. выход которого соединен с входом считывания блока памяти контрольных микрокоманд, выход регистра адреса контрольных микрокоманд соединен с адресным входом блока памяти контрольных микрокоманд, выход которого соединен с входом регистра контрольных микрокоманд, выход адреса регистра контрольных микрокоманд соединен с третьим входом формирователя адреса контрольных микрокоманд, выход кода логических условий регистра контрольных микрокоманд соединен с первыми входами первого и второго блоков элементов И, выход второго блока элементов И соединен с четвертым входом формирователя адреса контрольных микрокоманд, выход первой метки регистра контрольных микрокоманд соединен с первым входом третьего элемента И и через элемент НЕ с вторым входом второго блока элементов И, выход третьего элемента И соединен со счетным входом счетчика, инверсные выходы которого соединены с входами четвертого элемента И, выходы пятого и шестого элементов И соединены соответственно с первым и вторым входами блока анализа, первый выход которого является выходом ошибки рабочего канала устройства, дополнительно введены буферный регистр, коммутатор, первая и вторая схемы сравнения, мультиплексор, триггер логического условия, сумматор по модулю два, первый и второй одновибраторы, второй элемент ИЖ, причем вход пуска устройства соединен с первым входом второго элемента ИЛИ, выход которого через первый одновибратор соединен с первым входом первого элемента ИЛИ, выход четвертого элемента И через второй одновибратор соединен с вторым входом первого элемента РШИ, выходы кода логических условий и микроопераций регистра рабочих микрокоманд соединены соответственно с первым и вторым информационными входами коммутатора, первый и второй выходы которого соединены соответственно с первым и вторым входами первой схемы сравнения, выход первой схемы, сравнения соединен с третьим входом блока анализа, второйи третий выходы, которого соединены с выходами ошибок контрольного канала и ошибки с)едств контроля устройства соответственно, выход микроопераций регистра контрольных микрокоманд соединен с третьим . информационным входом коммутатора и первым входом второй схемы сравнения, выход коте ой соединен с вторым входом пятого элемента И, выход второго блока элементов И соединен с четвертым информационным входом комм татора, выход первой метки регистра контрольных микрокоманд соединен с первым управляющим входом коммутатор первым входом элемента И, входом синхронизации буферного регистра и вторым входом первого блока элементов И, выход которого соединен с информационным входом счетчика, выход второй метки регистра контрольных микрокоманд соединен с вторым управ ляющим входом коммутатора, вторыми входами пятого элемента И и второго э лемента ИЛИ и с входом синхронизации триггера хранения логического условия, единичный выход которого соединен с первым входом сумматора п модулю два, выход требуемого значени логического условия регистра контрольных микрокоманд соединен с вторы входом сумматора по модулю два, выхо которого Соединен с вторым входом шестого элемента И, выход кода логических условий регистра контрольных микрокоманд и вход логических услови устройства соединены соответственно с управляющим и информационным входами мультиплексора, выход которого соединен с информационным входом триггера хранения логического условия, выход адреса регистра контрольных микрокоманд соединен с информационным входом буферного регистра, выход которого соединен с вторым входом второй схемы сравнения. Кроме того, блок анализа содержит пять элементов И, три элемента ИЛИ и элемент , причем первый вход блока соединен с первыми входами пер вого, второго элементов И и первого элемента ИЖ, второй вход блока соединен с первыми входами третьего, четвертого Элементов И и элемента ШШ-НЕ, третий вход блока соединен с вторыми входами первого, третьего элементов И, с первым и вторым входо пятого элемента И, выход которого соединен с вторыми входами второго, четвертого элементов И и первого эл мента ИЛИ, выходы перйого, второго, третьего и четвертого элементов И соединены соответственно с первыми входами второго элемента ИЛИ, треть его элемента ИЛИ, вторыми входами второго и третьего элементов ИЛИ, выходы первого, второго, третьего элементов ИЛИ и .выход элемента ИЛИ-НЕ соединены соответственно с вторым входом элемента ШШ-НЕ, с выходом ощибки контрольного канала блока, выходом ошибки аппаратуры контроля блока и с выходом ощибки рабочего канала блока. Сущность изобретения состоит в повьшении достоверности функционирования путем обеспечения самопроверяёмости встроенньт средств контроля. В предлагаемом устройстве парал- . лельно с рабочим каналом (собственно устройством зтфавления) функционирует koHTponbHbrii канал и средства анализа. На всех этапах вьтолнения микропрогламмы (начальная микрокоманда линейной последовательности, промежуточная микрокоманда линейной последовательности, последняя микрокоманда линейной последовательности и ветвление в микропрограмме) происходит контроль функционирования как рабочего, так и контрольного каналов. При этом реализуются следующие дисциплины контроля.При выполнении начальной микрокоманды линейной последовательности происходит сравнение операционной части рабочей микрокоманды, которая следует первой в линейной последовательности, с операционной частью, соответствующей контрольнЪй микрокрманде, которая формируется параллельное этой (рабочей) микрокомандой. При выполнении промежуточной микрокоманды линейной последовательности (очередной рабочей микрокоманды) происходит вычитание единицы из содержимого счетчика, в котором записан код длины линейной последовательности. Этот код задается в поле кода логических условий первой контрольной микрокоманды. В последней микрокоманде линейной последовательности (микрокоманда ветвления) происходит сравнение кода логического условия рабочей микрокоманды, которая является последней в линейной последовательности (т.е. микрокоманды ветвления) , с кодом логических условий соответствующей (второй) контрольной микрокоманды, которая формируется параллельно с этой рабочей микрокомандой. Кроме того, происходит сравнение адресной части первой контрольной микрокоманды, которая запомина- ется в специальном буферном регистре с кодом, записанным в поле микроопераций второй контрольной микрокоманд При выполнении начальной микрокоманды следующей линейной последовательмости (первая микрокоманда после вет вления) происходит сравнение операционной части рабочей микрокоманды, которая следует первой в линейной последовательности, с операционной частью соответствующей (первой) конт рольной микрокоманды,формируемой параллельно с этой (рабочей) микрокомандой. Кроме того, осуществляется сравнение истинного значения логического условия, по которому произошло ветвление, с значением логического условия, записанным в поле специальной метки второй контрольной микрокоманды. Выполнение указанных дисциплин контроля позволяет проверять правильность реализации функции переходов рабочего канала, правильность реализации функции выходов рабочего канала, правильность реализации функции переходов контрольного канала, правильность реализации функции выходов контрольного канала. На фиг. 1 приведена функциональная схема микропрограммного устройства управления; ha фиг. 2 - функциональная схема коммутатора на фиг. 3 - функциональная схема формирователя адреса, на фиг, 4 - функциональная схема блока анализа; на фиг. 5 - схема алгоритма рабочей (а) и контрольной (б) микропрограммы. Функциональная схема коммутатора (фиг. 1) содержит формирователь 1 адреса рабочей микрокоманды, регистр 2адреса рабочих микрокоманд, блок 3памяти рабочих микрокоманд, регист 4рабочих микрокоманд, имеющий поле 4.1 косвенного адреса, поле 4.2 кода логических условий, поле 4.3 микроопераций, коммутатор 5, первую схему 6 сравнения, .блок 7 анализа, формиро ватель 8 адреса контрольных микрокоманд, регистр 9 адреса контрольных микрокоманд, блок 10 памяти контроль ных микрокоманд, регистр 11 контроль ных микрокоманд, содержащий поле 11. косвенного адреса, поле 11.2 логичес ких условий (длины линейной последовательности) , поле 11.3 микроопераций (контрольного адреса), поле 11.4 первой метки, поле 11.5 второй метки, поле 11.6 требуемого значения логических условий, первый блок 12 элементов И, элемент НЕ 13, второй блок 14 элементов И, третий элемент И 15, счетчик 16, четвертый элемент И 17, буферный регистр 18, вторую схему сравнения 19, седьмой элемент И 20, второй элемент ИЖ 21, первый одновибратор 22, второй одновибратор 23, первый элемент ИЛИ ,24, мультиплексор 25, триггер 26 хранения логического условия, сумматор 27 по модулю 2, шестой элемент И 28, триггер 29 пуска, генератор 30 импульсов, первый элемент И 31, второй элемент И 32, вход 33 пучка устройства, вход 34 кода устройства, вход 35 логических условий устройства, выход 36 метки конца работы, выход 37 микроопераций устройства, третий 38, четвертый 39 входы формирователя адреса рабочих микрокоманд, третий 40, четвертый 41 вхоДы формирователя адреса контрольных микрокоманд, первый 42, второй 43, третий 44, четвертый 45 информационные входы, первый 46, второй 47 управляющие вХоды, первый 48, второй 49 выходы коммутатора 5, третий 50, первый 51, второй 52 входы, первый 53, второй 54, третий 55 выходы блока 7 анализа, являющиеся выходом устройства соответ,ствеНно. Коммутатор 5 (фиг. 2) Содержит третий 56., четвертый 57, первый 58, второй 59 блоки элементов И, первый 60, второй 61 блоки элементов ИЛИ. Формирователь адреса 1 (8) рабочих (контрольных) микрокоманд (фиг. 3) содержит мультиплексор 62, элемент ИЛИ 63, блок элементов ИЛИ 64. Блок 7 анализа (фиг. 4) содержит первый 65 и второй 66 элементы И, элемент 67 НЕ, третий 68 и четверть й 69 элементы И, первый 70, второй 71, третий 72 элементы ИЛИ, элемент 73 ШЖ-НЕ. На фиг. 5 использованы следующие обозначения: А 1U1 Ц-г2 ресные части первых рабочих микрокоманд ij HI, И-2-линейных последовательностей микрокоманд, А.,, A.|.j, А адресные части первых конт- . рольных микрокоманд, соответствующих i, HI, Н2-Й последовательностям, A.j, А,, A.1f.2 адресные части последних рабочих микрокоманд i, i+1, i+2-й последовательностей, А 2л 1 адресные части вторых, конт- . рольных микрокоманд, соответствзпощих л, i+1, Н2-Й последовательностям, Х|, Х|ц. , X ,-+2 коды логических условий 1, 1+1, 1-«-2-й последовательностей . МО 1 (МО -tj) , МО i,4i(MO .,) , MO-,4+(.2)- микроопёрационные части первых рабочих (контрольных) микрокоманд г, 1+1, (1+2)-и последовательностей, МО микрооперационные части последних рабочих микрокоманд I, i+1, i+2-й последрвательностей, N, N. , N,42 число рабочих микрокоманд в , f+1, i+2-й последовательностях. А, ЛУ , М0,.1,2,3 - поля адреса,, кода логических условий, микроопераций, первой, второй и третьей меток (в , поле третьей метки записано значение требуемого логического условия) сорт1ветственно. Технические средства устройства могут быть разделены на четыре части рабочий и контрольньй каналы, аппаратура контроля и средс-геа синхрони зации. Рабочий канал предназначен для хранения микрокоманд и считывания их в соответствии с очередным адресом. Канал состоит из фбрмироватеяя адреса рабочих микрокоманд 1, предназначенного для формирования адреса следующей микрокоманды в зависимости от кода косвенного адреса и кода логического условия. Формирователи адрес 1 и 8 выполнены по идентичной схеме. ,Мультиплексо р 62 осуществляет выделение проверяемого логического условия и реализует функцию Х, V t /aeaj. +3сJ а at а J... а +.. значения проверяi 23емых логических условий, значения разрядов кода логических условий, поступающего на управлйю щие входы мульти . плёксора 62. Элемент 63 ИЛИ предназначен для модификации младшего разряда адреса значением проверяемого логического условия. Блок элементов 64 ИЛИ предназначен для формирования адреса по коду операции или коду, поступающему со входа 38: регистра адреса рабочих микрокоманд 2, в который записьгаается и хранится адрес последующей микрокоманды рабочей микропрог- раммы, блока памяти 5, предназначеяного для хранения рабочих микрокоманд, регистра микрокоманд 4, в который считываются и хранятся очередные рабочие микрокоманды, поступающие из блока памяти 3. Контрольньй канал предназначен для хранения юс в соответствии с очередным адресом. Этот канал состоит, из формирователя адреса контрольных микрокоманд 8, региЬтра адреса контрольных микрокоманд 9, блока памяти контрольных микрокоманд 10, регистра контрольных микрокоманд 11. Контрольный канал отличается от рабочего форматом хранимых микрокоманд, В регистр 11 дополнительно введены поле 11.4 первой метки, предназначенное для выдачи сигнала управления записью кода длины линейной последовательности в счетчик 16 и разрешения считьтания сигнала микроопераций с выхода регистра 11 контрольных микрокоманд на коммутатор 5, а также записью адресной части первой контрольной микрокоманды в буферный регистр 18, поле 11.5 второй метки, предназначенное для выдачи сигнала разрешения счйтьшания.логических условий с выхода регистра 11 контрольных микрокоманд на коммутатор 5 и записи в триггер 26 хранения логического условия действительного значения логического условия с выхода мульти- . плексора 25, поле 11.6 требуемого значения логического условия. Аппаратура контроля преднааначёна для анализа состояний рабочего и контрольного каналов и формирования . соответствующих сигналов на выходах 53-55 и Состоит из коммутатора 5, предназначенного для параллельной выдачи на схему сравнения 6 кодов микроопераций или логических условий рабочей и контрольной микрокоманд. Работа коммутатора заключается в следующем. На второй информационный вход 43 поступают сигналы микроопераций рабочей микрокоманды, на третий информационнь 1 вход 44 - сигналы микроопераций контрольной микрокоманды. По сигналу с выхода поля 11.4 i (метки 1), поступающему на второй управляющий вход 46, сигналы микроопераций рабочей микрокоманды через блоки злементов И 58 и ИЛИ 60 поступают на первый выход 48, а сигналы микроопераций контрольной микрокоманды через блоки элементов И 59 и ИЛИ 61 на второй выход 49. На перВЫЙ информационньй вход 42 поступает код логических условий рабочей микро команды. На четвертый информационный вход 45 поступает код логических услс вий контрольной микрокоманды. По сигналу с выхода поля 11.5 (метки 2) поступающему на второй управляющий вход 47, код логических условий рабочей микрокоманды через блоки элеме тов И 56 и ИЛИ 60 поступают на первый выход 48, а код логических условий контрольной микрокоманды через блоки элементов И 57 и ИЖ 61 поступает на второй выход 49, схемы сравнения 6, на которых происходит сравнение кодов микроопераций или логических условий, когорые поступают параллельно с коммутатора 5 и выдачи результата сравнения на блок 7 анализа, блок 7 анализа, предназначенный для вьздачи сигнала отказа рабочего, контрольного каналов или аппаратуры контроля. Работа блока 7 анализа заключается в следующем. На третий вход 50 поступает сигнал с выхода схемы срав нения 6, на первь1й вход 51 - сигнал с выхода схемы сравнения 1/9, на второй вход 52 - сигнал с выхода элемен та 27 сумма- по модулю два. На выхода блока 7 анализа формируются следующи сигналы: на первом выходе , на втором выходе. 54 {п, на треА ём выхо де 55fjqд 1где fjQo - сигнал ошибки рабочего канала устройства, Й1 сигнал ошибки контрольного канала устройства, сигнал ошибки аппа ратуры контроля. Работа блока 7 описывается следую щей таблицей . в таблице приняты следующие обозначения: сигнал на выходе 50, 2 сигнал на входе 51, на входе 52 соответствия 2 -j -Hi мл1( О элемент.а 12 И, предназначенного для управления записью кода длины линейной последовательности микрокоманд в счетчик 16, элементов 13 НЕ и 14 И, предназначенных для управления передачей К9да логического условия с выхода поля 11.2 регистра микрокоманд 11 на формирователь адреса контрольных микрокоманд и коммутатор 5, элемента 15 И, предназначенного для управления подачей импульсов на счетчик 16, счетчика 16, предназначенного для подсчета фактически выполненного числа микрокоманд линейной последовательности, элемента 17 И, предназначенного для вьщачи сигнала, свидетельствующего о нулевом состоянии счетчика 16, на одновибратор 23, одновибраторов 22 и 23, предназначенных для формирования импульсов считывания контрольных микрокоманд, буферного регистра 18, предназначендого для хранения адресной части первой микрокоманды, схемы сравнения 19., предназначенной для сравнения адресной части первой микрокоманды, записанной в буферном регистре 18, с контрольным адресом, записанным в поле 11.3 второй контрольной микрокоманды, элемента И 20, предназначенного для управления поступлением сигнала с выхода схемы сравнения 19 на вход 51 блока 7 анализа,мультиплексора 25, предназначенного для управления вьщачей значения проверяемого логического условия. Мультиплексор 25 реализует логическую функцию , аналогичную функции, реализуемой мультиплексором 62, триггера 26 хранения логического условия, в которьй записывается действительное значение логического условия, элемента 27 суммы по модулю два, предназначенного для суммирования по модулю два требуемого и действительного значения логического условия (проверка пра- вильности вьтолнения ветвления), элемента 28 И, который управляет вьщйчей сигнала с выхода элемента 27 сумма -по модулю два (результата сравнения) действительного и требуемого значений логических условий на вход 52 схемы анализа 7. Средства синхронизации, которые служат для синхронизации работы устройства, состоят из триггера пуска 29, предназначенного для запуска устройства по сигналу Пуск, поступающему на вход 33, и для остановки устройства по сигналу Стоп, который содержится в последней микрокоманде микропрограммы и поступает на Р-ВХОД триггера пуска 29 с выхода 36 регистра 4, генератора импульсов 30, который вьфабатывает синхроимпульсы, элементов 31 И и 32 И, предназначенных для управления прохождением синхроимпульсов в рабочий и кон трольный каналы. Устройство работает следующим образом. . В исходном состоянии все элементы памяти установлены в нуль. С входа 33 сигнал пуска поступает на вход S триггера пуска29 и через элемент ШШ 21 на одновибратор 22. Сигнал пуска устанавливает триггер пуска 29 в единичное состояние. Сигнал с выхода триггера пуска 29 поступает на элемент И 31, на второй вход которого поступает сигнал с вь1хода ге.нератора импульсов 30. Через элемент И 31,открытый сигналом с выхода три гера пуска 29, синхроимпульс поступа ет на вход регистра адреса микрокоманд 25. По сигналу Пуск триггер 29 устанавливается в единичное состояние а одновибратор 22 формирует импульс который через элемент ИЛИ 24 поступает на вход элемента И 32. На второй вход этого элемента поступает синхроимпульс с выхода элемента И 31 Синхроимпульс проходит через элемент И 32 на вход считывания блока памяти контрольных микроко манд 10, Одновременно по первому синхроимпульсу с выхода элемента И 31, поступающему на вход блока 3 памяти рабочих микрокоманд, через регистр 2 адреса микрокоманд и блок памяти 3 в регист микрокоманд 4 считывается первая ра бочая микрокоманда. С выхода поля 4.1 через формирователь адреса 1 в регистр адреса 2 записывается адрес следующей микрокоманды.. С выхода поля 4.3 сигналы микроопераций поступают на вход 37 устройстваи на коммутатор 5. По синхроимпульсу с выхода элемента S 32 И в регистр 11 считывается перва контрольная микрокоманда. С выхода поля 11.1 адрес первой микрокоманды поступает на вход формирователя 8, котором формируется адрес следующей (второй) контрольной микрокоманды, также заносится в буферньтй регистр 18. С выхода поля 11.2 через элемен И 12, открытый сигнал с выхода поля 11.4, в счетчик 16 записывается код длины линейной последовательности микрокоманд равный N-2, где N - число микрокоманд в линейной последовательности. С выхода поля 11.3 код микроопераций поступает на коммутатор 5. С выхода поля первой метки 11.4 сигнал поступает на вход буферного регистра 18 и разрешает запись в него адреса первой контрольной микрокоманды. Этот же сигнал поступает на коммутатор 5 и разрешает параллельное поступление микроопераций рабочей и контрольной микрокоманд на схему сравнения 6, где происходит сравнение этих кодов микроопераций, результат которого поступает на блок 7 анализа. По каждому синхроимпульсу происходит считывание следующих рабочих микрокоманд аналогично описанному выше, а от содержимого счетчика 16 вычитается единица. Считывание контрольных микрокоманд блокируется элементом 32.И. При считывании (М-2)-й рабочей микрокоманды счетчик 16 устанавливается в нуль. Сигнал с вькода элемента И 17 (при обнулении счетчика 16) поступает на одновибратор 23, который формирует импульс, открывающий элемент И 32 и разрешающий считывание второй контрольной микрокоманды. По адресу, записанному в регистр 9, из блока памяти микрокоманд 10 считьшается вторая контрольная микрокоманда (микрокоманда ветвления).. С выхода поля 11.1 адрес микрокоманды поступает на вход формирователя адреса 8, в котором формир уется адрес следующей микрокоманды (первой контрольной микрокоманды). С выхода поля 11.2 код логических условий через блок элементов И 14, открытый сигналом с элемента НЕ 13, поступает на формирователь адреса контрольных микрокоманд 8, коммутатор 5, а также на мультиплексор 25. Сигнал с выхода мультиплексора 25 поступает на D-ВХОД триггера хранения логического условия 26 По сигналу, поступающему с выхода поля 11.5 на С-вход триггера 26, действительное значение логического условия запоминается в триггере 26., С выхода поля 11.3 контрольный адрес поступает на схему сравнения 19, где происходит его сравнение с адресом первой микрокоманды, записанным ранее в буферный регистр 18.

«При этом контролируется правильность перехода от первой ко второй контрольной микрокоманде, а следовательно, работоспособность контрольного канала. С выхода поля 11.5 сигнал поступает на коммутатор 5 и разрешает параллельное поступление кодо логических условий рабочей и контрольной микрокоманд на схему сравнения 6, где происходит их сравнение, результат которого поступает на блок 7 анализа. Этот же сигнал через элемент ИЛИ 21 поступает на одновибрато 22, который формирует импульс считывания следзгющей первой после ветвлеНИЛ контрольной микрокоманды.

Прохождение рабочих и контрольных микрокоманд происходит аналогично описанному. Кроме того, сигнал с вых да поля 11.4, поступая на элемент И 28, разрешает прохождение сигнала с элемента 27 суммато1за по модулю два, который сравнивает истинное значение

логического условия, зафцксированйого триггером 26, с требуемым его значением, записанным в поле 11.6, на блок 7 а 1ализа, что позволяет проверить правильность ветвления в микрограмме и обнаруживать сбой. Дальнейшая работа происходит по алгоритму, описанному вьш1е.

По микрооперации Стоп, которая .содержится в последней микрокома;нде микропрограммы,сигнал с выхода 36 поля 4.3 регистра микрокоманд А поступает на R-вход 36 триггера пуска 29 и устанавливает его в нулевое состояние, тем самым запрещая прохождение синхроимпульсов с генератора 30 через элемент И 31 на входы считьгоания блоков памяти.

Применение предлагаемого технического решения позволит проектировать надежные микропрограммные управляющие устройства с высокой достоверностью функционирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1166110A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1180888A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1020825A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Параллельное микропрограммное устройство управления | 1983 |

|

SU1109750A1 |

1.МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ,содержащее формировательадреса рабочих микрокоманд, формирователь адреса контрольных микрокоманд, регистр адреса рабочих микрокоманд регистр адреса контрольных микрокоманд блок памяти рабочих микрокоманд, блок памяти контрольньпс микрокоманд, регистр рабочих микрокоманд, регистр контрольных микрокоманд, генератор тактовых импульсов, блок анализа, счетчик, триггер пуска, первый и второй блоки элементов И,шесть элементов И, первый элемент ИЛИ и элемент НЕ, причем вход кода операции устройства соединен с первыми входами формирователей адреса рабочих и контрольных микрокоманд соответственно,выходы которых соединены с входами регистров адреса рабочих и контрольных микрокоманд соответственно, вход логических уело ВИЙ устройства соединен с вторыми , входами формирователей адреса рабочих и контрольных микрокоманд, выходы ад реса кода логических условий микроопераций и метки конца работы регистра рабочих микрокоманд соединены соответственно с третьим и четвертым входами формирователя аДреса рабочих микрокоманд, выходом микроопераций устройства и нулевым выходом триггера пуска, выход которого соединен с первым входом первого элемента И, вход пуска устройства и вьтход генератора тактовых импульсов соединены соответственно с единичным входом триггера пуска и вторым входом первого элемента И, выход которого соединен с первым входом второго элемента И и входом считьгоания блока памяти рабочих микрокоманд, выход регистра адреса рабочих микрокоманд соединен с адресным входом блока памяти рабочих микрокоманд, выход которого соединен с инфор-8 мационн1Ф1 входом регистра рабочих микрокоманд, выход первого элемента ЦПИ соединен с вторьм входом второго элемента И, выход которого соединен с входом считывания блока памяти конт-i рольных микрокоманд, выход регистра адреса контрольных микрокоманд соединей с адресным входом блока памяти конi трольных микрокоманд, выход которого соединен с входом регистра контрольных Од микрокоманд, выход адреса регистра ьэ контрольных миерокоманд соединен с третьим входом формирователя адреса л контрольных микрокоманд., выход кода логических условий регистра контрольных микрокоманд соединен с первыми входами первого и второго блоков элементов И, выход второго блока элемен тов И соединен с четвертым входом формироват еля адреса контрольных мик рокоманд, выход первой метки регистра контрольных микрокоманд соединен с первым входом третьего элемента И и через элемент НЕ с вторым входом второго блока элементов И, выход треть

фишА АЛУМО

1100625

J

У МО

A

ЛУ

1

Jfy MO

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля блока микропрограммного управления | 1975 |

|

SU598079A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 849889, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-06-30—Публикация

1983-02-08—Подача