Изобретение относится к вычислительной технике, предназначено для генерации и формирования синхросигналов и может быть использовано в ЭВМ, многомашинных комплексах и многопро- цессорных вычислительных системах.

Целью изобретения является расширение функциональных возможностей за счет обеспечения непрерьгоного контроля синхрои тульсов с возможностью ав- томатической коррекции при нарушении сдвигов синхроимпульсов.

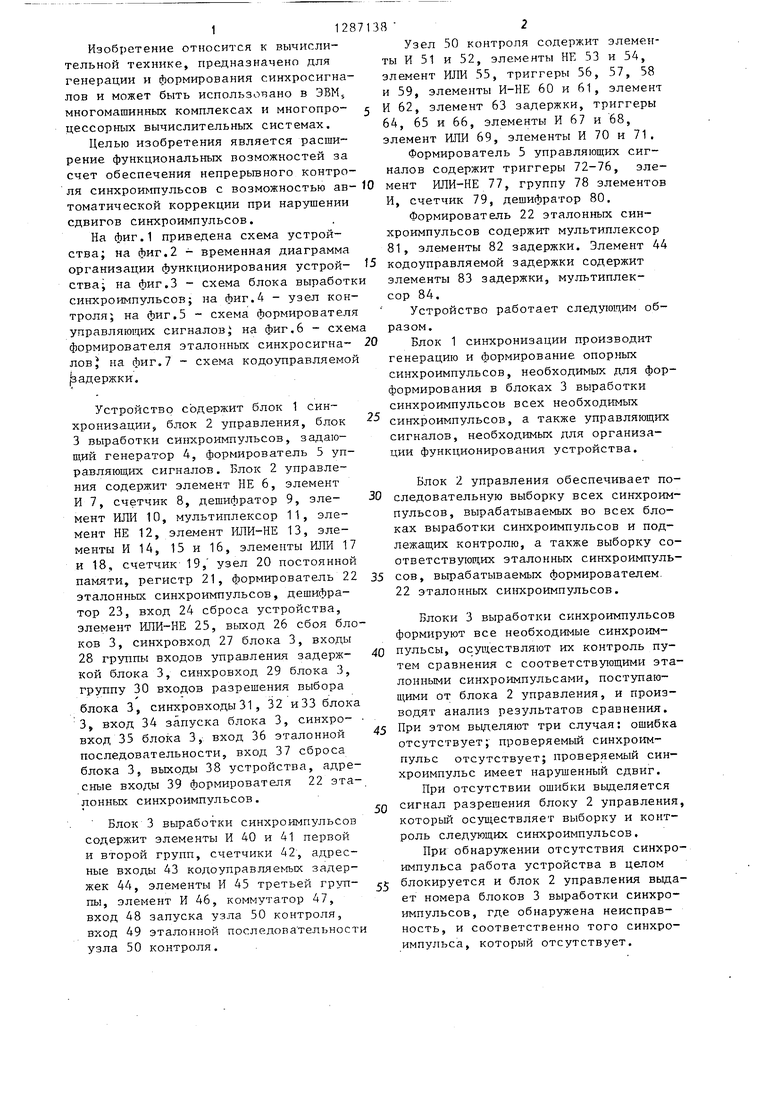

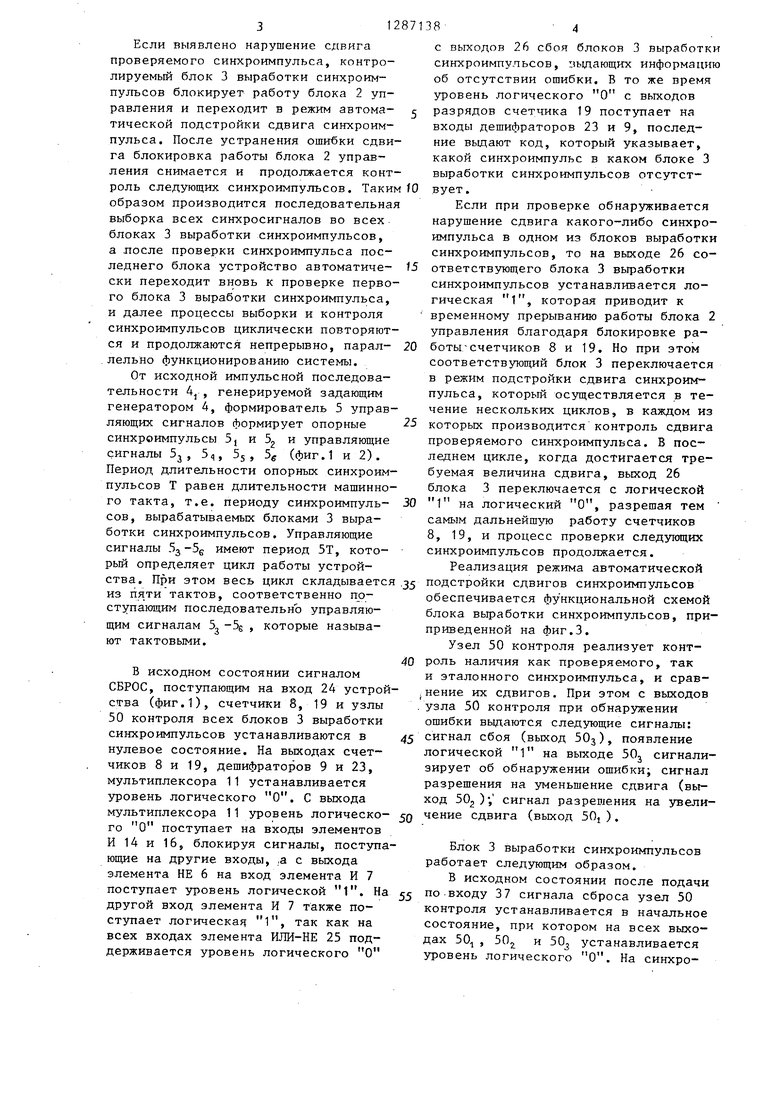

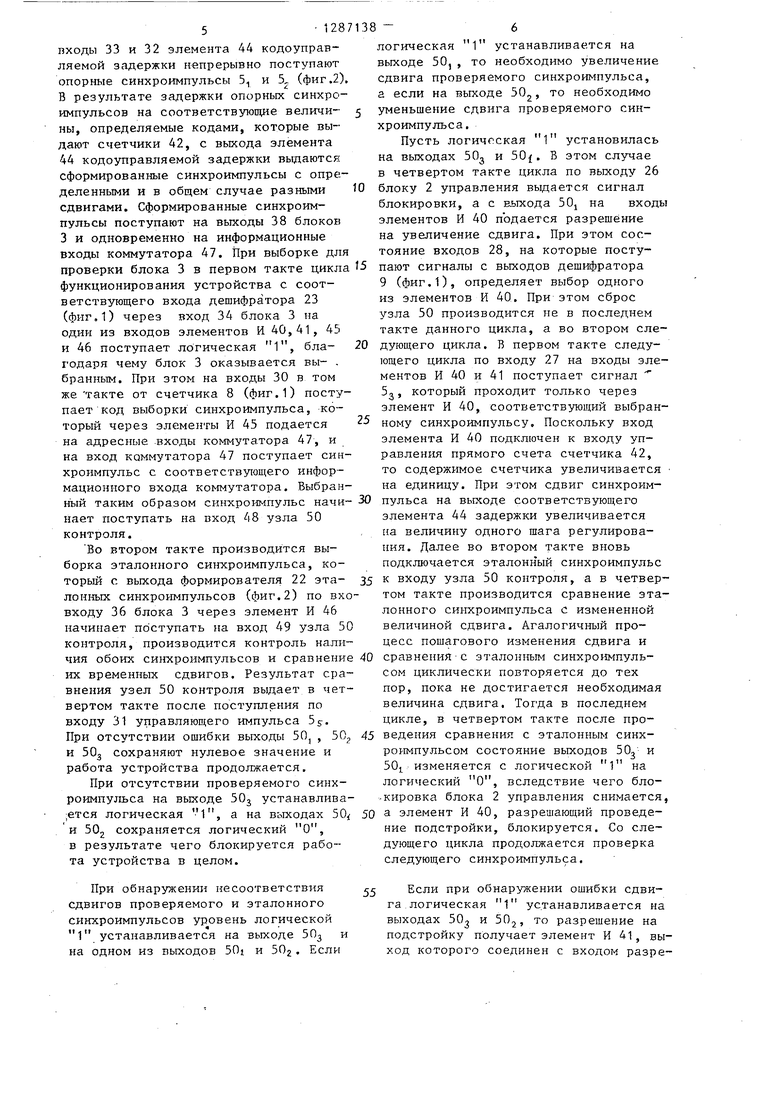

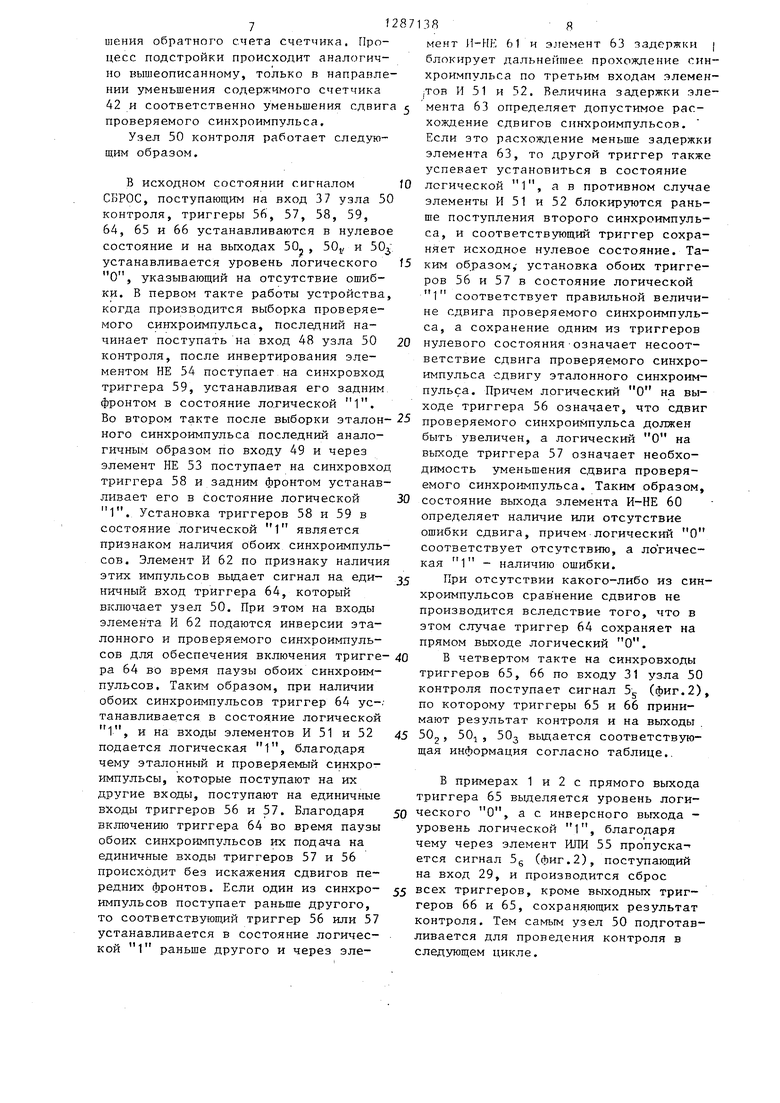

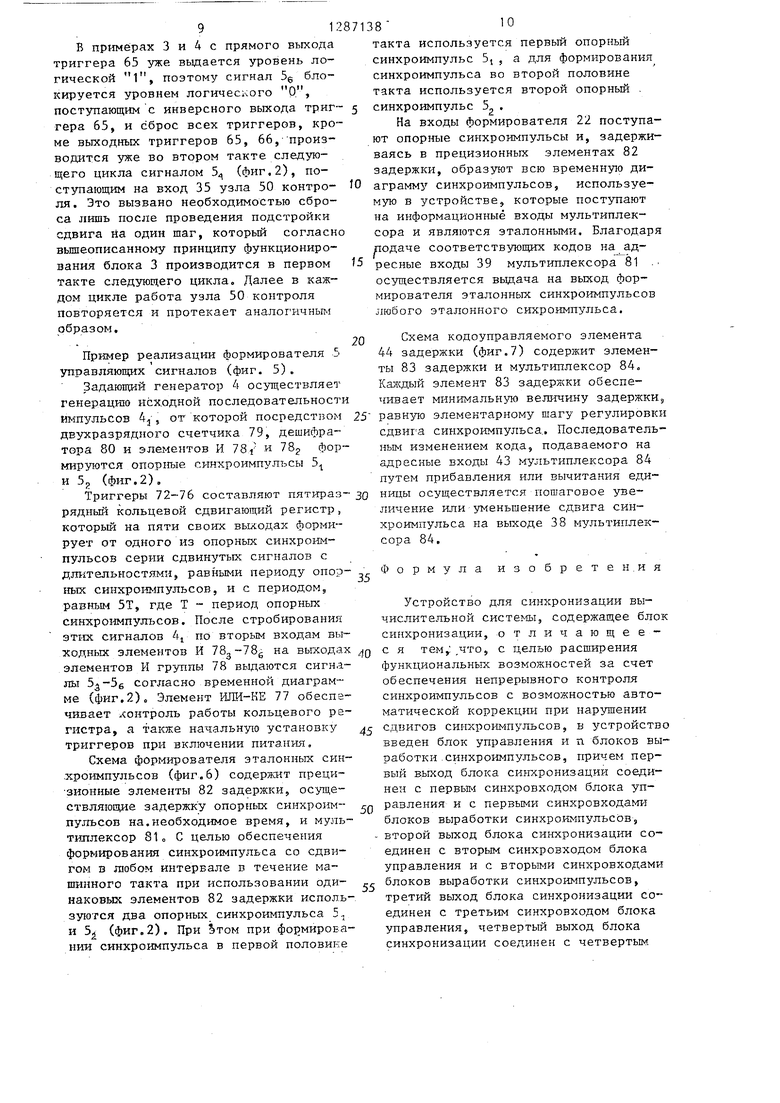

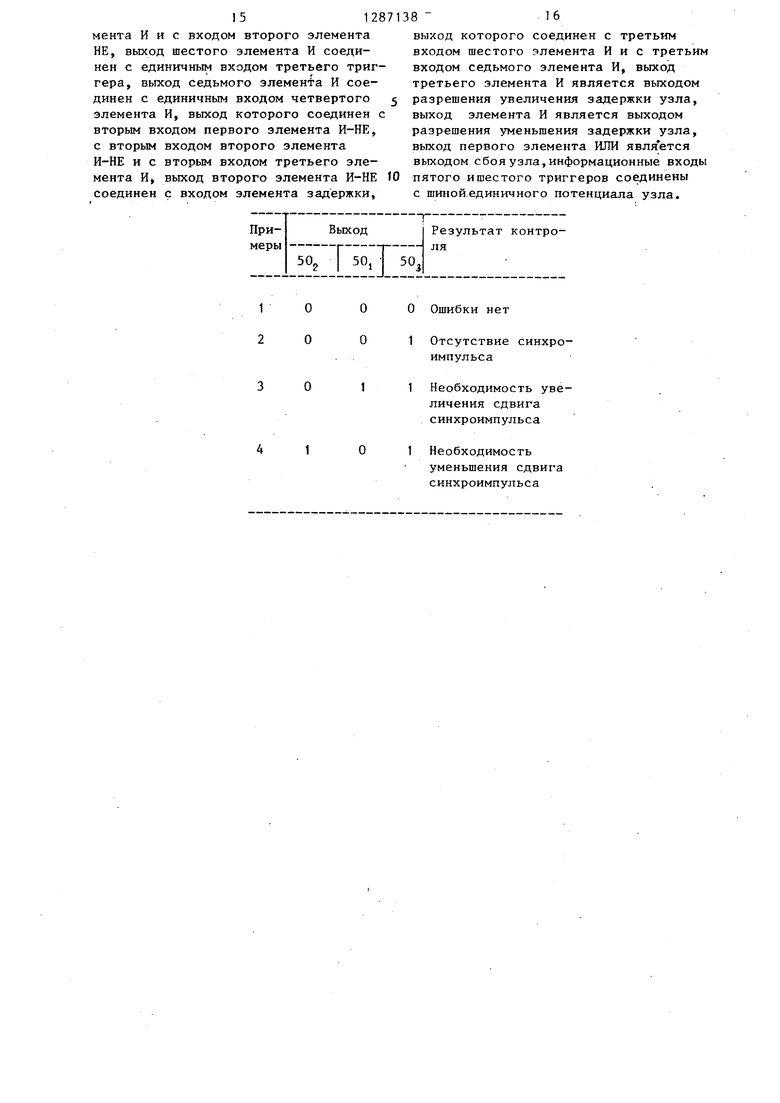

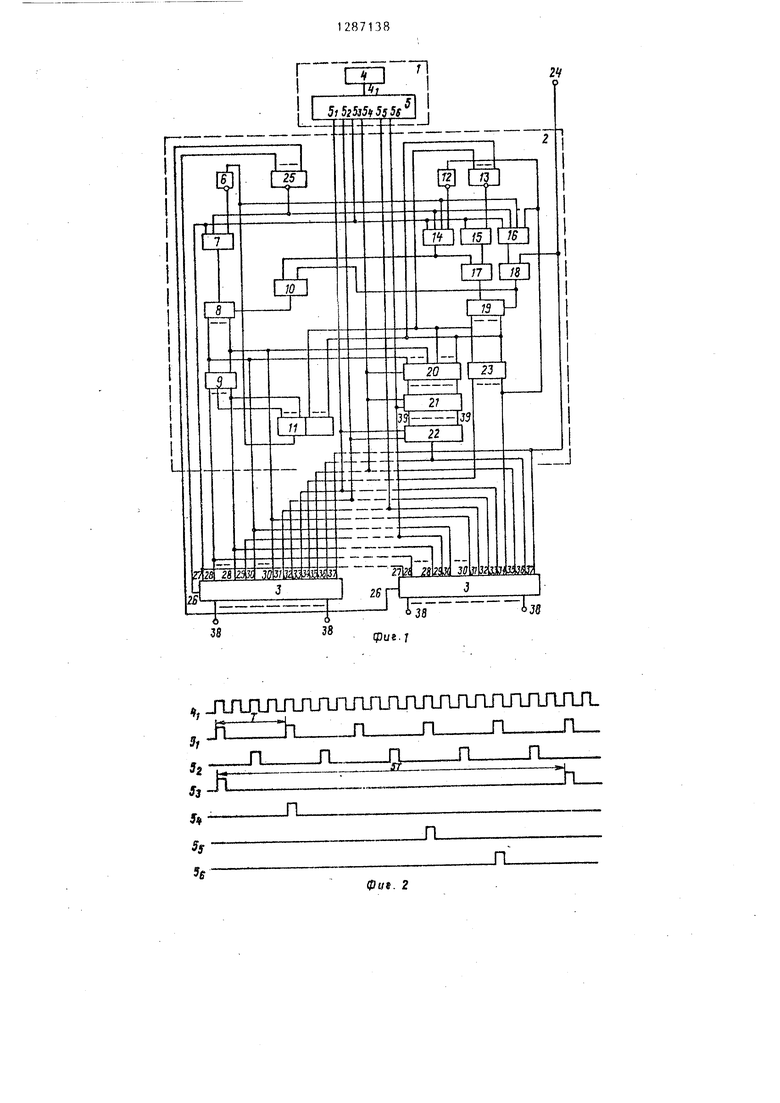

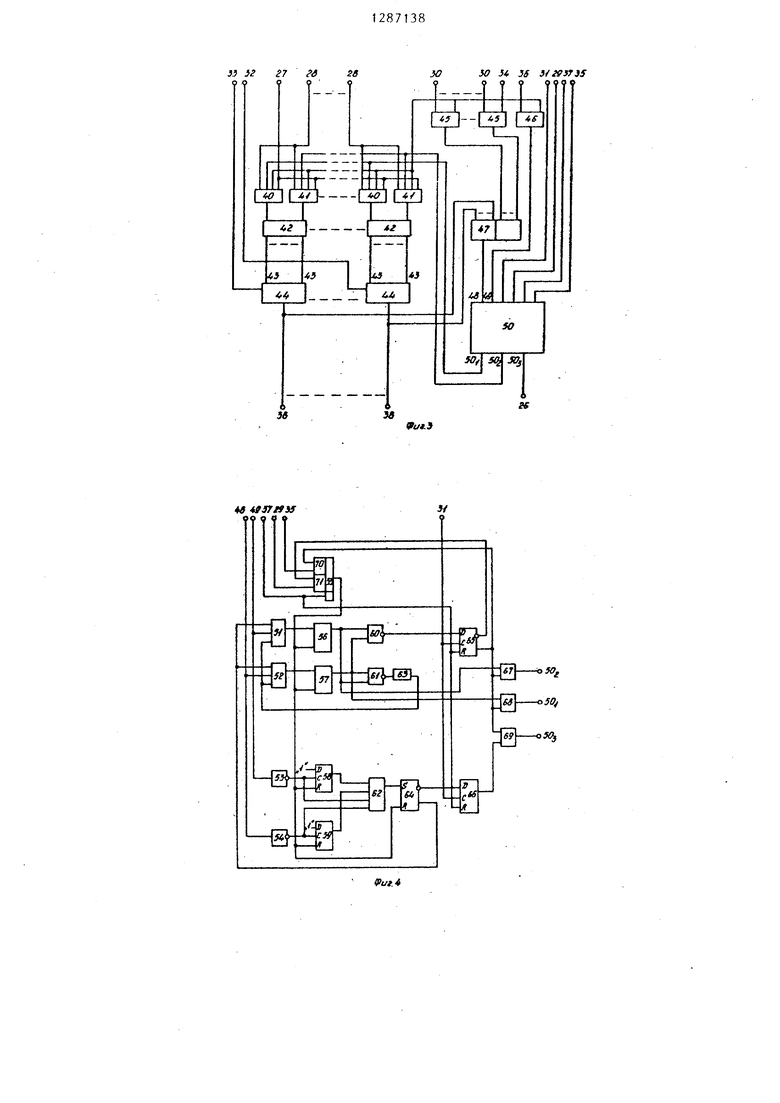

На фиг.1 приведена схема устройства; на фиг.2 - временная диаграмма организации функционирования устрой- ства; на фиг.З - схема блока выработк синхроимпульсов; на фиг.4 - узел контроля; на фиг.З - схема формирователя управляющих сигналовJ на фиг,6 - схем формирователя эталонных синхросигна- лов на фиг.7 - схема кодоуправляемой Задержки.

Устройство содержит блок 1 синхронизации, блок 2 управления, блок 3 выработки стгхроимпульсов, задающий генератор 4, формирователь 5 управляющих сигналов. Блок 2 управления содержит элемент НЕ 6, элемент И 7, счетчик 8, дешифратор 9, элемент ИЛ1 10, мультиплексор 11, элемент НЕ 12, элемент 11ЛИ-НЕ 13, элементы И 14, 15 и 16, элементы ИЛИ 17 и 18, счетчик 19, узел 20 постоянной памяти, регистр 21, формирователь 22 эталонных синхроимпульсов, дешифратор 23, вход 24 сброса устройства, элемент ИЛИ-НЕ 25, выход 26 сбоя блоков 3, синхровход 27 блока 3, входы 28 группы входов управления задержкой блока 3, синхровход 29 блока 3, группу 30 входов разрешения выбора блока 3, синхровходы 31, 32 и 33 блока З, вход 34 запуска блока 3, синхро- вход 35 блока 3, вход 36 эталонной последовательности, вход 37 сброса блока 3, выходы 38 устройства, адресные входы 39 формирователя 22 эталонных синхроимпульсов.

Блок 3 выработки синхроимпульсов содержит элементы И 40 и 41 первой и второй групп, счетчики 42, адресные входы 43 кодоуправляемых задержек 44, элементы И 45 третьей группы, элемент И 46, коммутатор 47, вход 48 запуска узла 50 контроля, вход 49 эталонной последова тельности узла 50 ко.нтроля.

5

5 0

0

5

0

5

0

5

Узел 50 контроля содержит элементы И 51 и 52, элементы НЕ 53 и 54, элемент ИЛИ 55, триггеры 56, 57, 58 и 59, элементы И-НЕ 60 и 61, элемент И 62, элемент 63 задержки, триггеры 64, 65 и 66, элементы И 67 и 68, элемент ИЛИ 69, элементы И 70 и 71.

Формирователь 5 управляющих сигналов содержит триггеры 72-76, элемент ИЛИ-НЕ 77, группу 78 элементов И, счетчик 79, дешифратор 80.

Формирователь 22 эталонных синхроимпульсов содержит мультиплексор 81, элементы 82 задержки. Элемент 44 кодоуправляемой задержки содержит элементы 83 задержки, мультиплексор 84.

Устройство работает следующим образом.

Блок 1 синхронизации производит генерацию и формирование опорных синхроимпульсов, необходимых для фор- формирования в блоках 3 выработки синхроимпульсов всех необходимых синхроимпульсов, а также управляющих сигналов, необходимых для организации функционирования устройства.

Блок 2 управления обеспечивает последовательную выборку всех синхроимпульсов, вырабатываемых во всех блоках выработки синхроимпульсов и подлежащих контролю, а также выборку соответствующих эталонных синхроимпульсов, вырабатываемых формирователем. 22 эталонных синхроимпульсов.

Блоки 3 выработки синхроимпульсов формируют все необходимые синхроимпульсы, осуществляют их контроль путем сравнения с соответствующими эталонными синхроимпульсами, поступаю- от блока 2 управления, и производят анализ результатов сравнения. Нри этом выделяют три случая: ошибка отсутствует; проверяемьй синхроимпульс отсутствует; проверяемый синхроимпульс имеет нарушенный сдвиг.

При отсутствии ошибки вьщеляется сигнал разрешения блоку 2 управления, который осуществляет выборку и контроль следующих синхроимпульсов.

При обнаружении отсутствия синхроимпульса работа устройства в целом блокируется и блок 2 управления выдает номера блоков 3 выработки синхроимпульсов, где обнаружена неисправность, и соответственно того синхроимпульса, который отсутствует.

312

Если выявлено нарушение сдвига проверяемого синхроимпульса, контролируемый блок 3 выработки синхроим- пу/шсов блокирует работу блока 2 управления и переходит в режим автома- тической подстройки сдвига синхроимпульса. После устранения ошибки сдвига блокировка работы блока 2 управления снимается и продолжается контроль следующих синхроимпульсов. Таким образом производится последовательная выборка всех синхросигналов во всех блоках 3 выработки синхроимпульсов, а лосле проверки синхроимпульса последнего блока устройство автоматиче- ски переходит вновь к проверке первого блока 3 выработки синхроимпульса, и далее процессы выборки и контроля синхроимпульсов циклически повторяются и продолжаются непрерывно, парал- лельно функционированию системы.

От исходной импульсной последовательности 4 , генерируемой задающим генератором 4, формирователь 5 управляющих сигналов формирует опорные синхроимпульсы 5j и Sg и управляющие сигналы 5j, 5q, 5;, 5 (фиг.1 и 2). Период длительности опорных синхроимпульсов Т равен длительности машинного такта, т.е. периоду синхроимпуль- сов, вырабатываемых блоками 3 выработки синхроимпульсов. Управляющие сигналы Зз-5е имеют период 5Т, кото- рый определяет цикл работы устройства. При этом весь цикл складывается из пяти тактов, соответственно поступающим последовательно управляющим сигналам 5 -5е , которые называют тактовыми.

В исходном состоянии сигналом

СБРОС, поступающим на вход 24 устройства (фиг.1), счетчики 8, 19 и узлы 50 контроля всех блоков 3 выработки синхроимпульсов устанавливаются в нулевое состояние. На выходах счетчиков 8 и 19, дешифраторов 9 и 23, мультиплексора 11 устанавливается уровень логического О. С выхода мультиплексора 11 уровень логическо- го О поступает на входы элементов И 14 и 16, блокируя сигналы, поступающие на другие входы, л с выхода элемента НЕ 6 на вход элемента И 7 поступает уровень логической 1. На другой вход элемента И 7 также поступает логическа 1, так как на всех входах элемента ИЛИ-НЕ 25 поддерживается уровень логического О

384

с выходов 26 сбоя блоков 3 выработки синхроимпульсов, выдающих информацию об отсутствии ошибки, в то же время уровень логического О с выходов разрядов счетчика 19 поступает на входы дешифраторов 23 и 9, последние вьщают код, который указывает, какой синхроимпульс в каком блоке 3 выработки синхроимпульсов отсутствует.

Если при проверке обнаруживается нарушение сдвига какого-либо синхроимпульса в одном из блоков выработки синхроимпульсов, то на выходе 26 соответствующего блока 3 вьфаботки синхроимпульсов устанавливается логическая 1, которая приводит к временному прерыванию работы блока 2 управления благодаря блокировке работы -счетчиков 8 и 19. Но при этом соответствующий блок 3 переключается в режим подстройки сдвига синхроимпульса, который осуществляется в течение нескольких циклов, в каждом из которых производится контроль сдвига проверяемого синхроимпульса. В последнем цикле, когда достигается требуемая величина сдвига, выход 26 блока 3 переключается с логической 1 на логический О, разрешая тем самым дальнейшую работу счетчиков 8, 19, и процесс проверки следующих синхроимпульсов продолжается.

Реализация режима автоматической подстройки сдвигов синхроимпульсов обеспечивается функциональной схемой блока выработки синхроимпульсов, при- приведенной на фиг.З.

Узел 50 контроля реализует контроль наличия как проверяемого, так и эталонного синхрош-шульса, и срав- .нение их сдвигов. При этом с выходов узла 50 контроля при обнаружении ошибки выдаются следующие сигналы: сигнал сбоя (выход 50з), появление логической 1 на выходе 50з сигнализирует об обнаружении ошибки; сигнал разрешения на уменьшение сдвига (выход 50 ), сигнал разрешения на увеличение сдвига (выход 50i ).

Блок 3 выработки синхроимпульсов работает следующим образом.

В исходном состоянии после подачи по входу 37 сигнала сброса узел 50 контроля устанавливается в начальное состояние, при котором на всех выходах 50 , 502 и 50 устанавливается уровень логического О. На синхропходы 33 и 32 элемента 44 кодоуправ- ляемой задержки непрерывно поступают опорные синхроимпульсы 5, и 5,, (фиг .2). В результате задержки опорных синхроимпульсов на соответствующие величины, определяемые кодами, которые выдают счетчики 42, с выхода элемента 44 кодоуправляемой задержки выдаются сформированные синхроимпульсы с определенными и в общем случае разными сдвигами. Сформированные синхроимпульсы поступают на выходы 38 блоков 3 и одновременно на информационные входы коммутатора 47. При выборке для

10

логическая 1 устанавливается на выходе 50, , то необходимо увеличени сдвига проверяемого синхроимпульса, а если на выходе 50, то необходимо уменьшение сдвига проверяемого синхроимпульса.

Пусть логическая 1 установилас на выходах 50 и 50{. В этом случае в четвертом такте цикла по выходу 2 блоку 2 управления вьщается сигнал блокировки, а с выхода 50j на вхо элементов И 40 подается разрешение на увеличение сдвига. При этом состояние входов 28, на которые поступроверки блока 3 в первом такте цикла 5 пают сигналы с выходов дешифратора

9 (фиг.1), определяет выбор одного из элементов И 40. При этом сброс узла 50 производится не в последнем такте данного цикла, а во втором сл

функционирования устройства с соответствующего входа дешифратора 23 (фиг,1) через вход 34 блока 3 на один из входов элементов И 40,41, 45 и 46 поступает логическая 1, благодаря чему блок 3 оказывается вы- . бранным. При этом на входы 30 в том же такте от счетчика 8 (фиг.1) поступает код выборки синхроимпульса, который через элементы И 45 подается на адресные входы коммутатора 47, и на вход коммутатора 47 поступает синхроимпульс с соответстБЗТощего информационного входа коммутатора. Быбран9 (фиг.1), определяет выбор одного из элементов И 40. При этом сброс узла 50 производится не в последнем такте данного цикла, а во втором сле20 дующего цикла. В первом такте следующего цикла по входу 27 на входы элементов И 40 и 41 поступает сигнал 5, который проходит только через элемент И 40, соответствующий выбран25 ному синхроимпульсу. Поскольку вход элемента И 40 подключен к входу управления прямого счета счетчика 42, то содержимое счетчика увеличивается на единицу. При этом сдвиг синхроимный таким образом синхроимпульс начн- 30 пульса на выходе соответствующего нает поступать на вход 48 узла 50 элемента 44 задержки увеличивается контроля.на величину одного шага регулирова Во втором такте производится вы- иия. Далее во втором такте вновь борка эталонного синхроимпульса, ко- подключается эталонный синхроимпульс торый с выхода формирователя 22 эта- 35 входу узла 50 контроля, а в четвер- лонных синхроимпульсов (фиг.2) по вхо- том такте производится сравнение эта- входу 36 блока 3 через элемент И 46 лонного синхроимпульса с измененной начинает по ступать на вход 49 узла 50 величиной сдвига. Агалогичный про- контроля, производится контроль налн- цесс пошагового изменения сдвига и чия обоих синхроимпульсов и сравнение 40 сравнения-с эталонным синхроимпуль- их временных сдвигов. Результат ера- сом циклически повторяется до тех внения узел 50 контроля выдает в четвертом такте после поступления по входу 31 управляющего импульса 5. При отсутствии ошибки выходы 50, , 50,, и 50 сохраняют нулевое значение и работа устройства продолжается.

При отсутствии проверяемого синхроимпульса на выходе 50 устанавлива- -кировка блока 2 управления снимается, ;ется логическая 1, а на выходах 50 50 а элемент И 40, разрешающий проведе- и 50 сохраняется логический О, в результате чего блокируется работа устройства в целом.

пор, пока не достигается необходимая величина сдвига. Тогда в последнем цикле, в четвертом такте после про- 45 ведения сравнения с эталонным синхроимпульсом состояние выходов 50 и 50 изменяется с логической 1 на логргческий О, вследствие чего блоние подстройки, блокируется. Со следующего цикла продолжается проверка следующего синхроимпульса.

При обнаружении несоответствия сдвигов проверяемого и эталонного синхроимпульсов уровень логической 1 устанавливается на выходе 50 и на одном из выходов 50t и 502. Если

логическая 1 устанавливается на выходе 50, , то необходимо увеличение сдвига проверяемого синхроимпульса, а если на выходе 50, то необходимо уменьшение сдвига проверяемого синхроимпульса.

Пусть логическая 1 установилась на выходах 50 и 50{. В этом случае в четвертом такте цикла по выходу 26 блоку 2 управления вьщается сигнал блокировки, а с выхода 50j на входы элементов И 40 подается разрешение на увеличение сдвига. При этом состояние входов 28, на которые поступают сигналы с выходов дешифратора

9 (фиг.1), определяет выбор одного из элементов И 40. При этом сброс узла 50 производится не в последнем такте данного цикла, а во втором следующего цикла. В первом такте следующего цикла по входу 27 на входы элементов И 40 и 41 поступает сигнал 5, который проходит только через элемент И 40, соответствующий выбранному синхроимпульсу. Поскольку вход элемента И 40 подключен к входу управления прямого счета счетчика 42, то содержимое счетчика увеличивается на единицу. При этом сдвиг синхроимиия. Далее во втором такте вновь подключается эталонный синхроимпульс входу узла 50 контроля, а в четвер- том такте производится сравнение эта- онного синхроимпульса с измененной величиной сдвига. Агалогичный про- цесс пошагового изменения сдвига и сравнения-с эталонным синхроимпуль- сом циклически повторяется до тех

кировка блока 2 управления снимается, а элемент И 40, разрешающий проведе-

пор, пока не достигается необходимая величина сдвига. Тогда в последнем цикле, в четвертом такте после про- ведения сравнения с эталонным синхроимпульсом состояние выходов 50 и 50 изменяется с логической 1 на логргческий О, вследствие чего бло-кировка блока 2 управления снимается, а элемент И 40, разрешающий проведе-

ние подстройки, блокируется. Со следующего цикла продолжается проверка следующего синхроимпульса.

Если при обнаружении ошибки сдвига логическая 1 устанавливается на выходах 50 и 502, то разрешение на подстройку получает элемент И 41, выход которого соединен с входом разре7t

тения обратного счета счетчика. Процесс подстройки происходит аналогично вышеописанному, только в направлении уменьшения содержимого счетчика 42 и соответственно уменьшения сдвиг проверяемого синхроимпульса.

Узел 50 контроля работает следующим образом.

В исходном состоянии сигналом СБРОС, поступающим на вход 37 узла 50 контроля, триггеры 56, 57, 58, 59, 64, 65 и 66 устанавливаются в нулевое состояние и на выходах 50, , 50t/ и 50 устанавливается уровень логического О, указывающий на отсутствие ошибки. В первом такте работы устройства когда производится выборка проверяемого синхроимпульса, последний начинает поступать на вход 48 узла 50 контроля, после инвертирования элементом НЕ 54 поступает на синхровход триггера 59, устанавливая его задним фронтом в состояние логической 1. Во втором такте после выборки эталон- ного синхроимпульса последний аналогичным образом по входу 49 и через элемент НЕ 53 поступает на синхровход триггера 58 и задним фронтом устанавливает его в состояние логической 1. Установка триггеров 58 и 59 в состояние логической 1 является признаком наличия: обоих синхроимпульсов. Элемент И 62 по признаку наличия этих импульсов выдает сигнал на еди- ничный вход триггера 64, который включает узел 50. При этом на входы элемента И 62 подаются инверсии эталонного и проверяемого синхроимпульсов для обеспечения включения тригге- ра 64 во время паузы обоих синхроимпульсов. Таким образом, при наличии обоих синхроимпульсов триггер 64 ус-.- танавливается в состояние логической 1, и на входы элементов И 51 и 52 подается логическая 1, благодаря чему эталонный и проверяемый синхроимпульсы, которые поступают на их другие входы, поступают на единичные входы триггеров 56 и 57. Благодаря включению триггера 64 во время паузы обоих синхроимпульсов их подача на единичные входы триггеров 57 и 56 происходит без искажения сдвигов передних фронтов. Если один из синхро- импульсов поступает раньше другого, то соответствующий триггер 56 или 57 устанавливается в состояние логической 1 раньше другого и через эле1388

мент И-НК 61 и элемент 63 задержки блокирует дальнейшее прохождение синхроимпульса по третьш входам элемен jTOB И 51 и 52, Величина задержки элемента 63 определяет допустимое расхождение сдвигов синхроимпульсов. Если это расхождение меньше задержки элемента 63, то другой триггер также успевает установиться в состояние логической 1, а в противном случае элементы И 51 и 52 блокируются раньше поступления второго синхроимпульса, и соответствующий триггер сохраняет исходное нулевое состояние. Таким образом,- установка обоих триггеров 56 и 57 в состояние логической 1 соответствует правильной величине сдвига проверяемого синхроимпульса, а сохранение одним из триггеров нулевого состояния-означает несоответствие сдвига проверяемого синхроимпульса сдвигу эталонного синхроимпульса. Причем логический О на выходе триггера 56 означает, что сдвиг проверяемого синхроимпульса должен быть увеличен, а логический О на выходе триггера 57 означает необходимость уменьшения сдвига проверяемого синхроимпульса. Таким образом, состояние выхода элемента И-НЕ 60 определяет наличие или отсутствие ошибки сдвига, причем логический О соответствует отсутствию, а ло гичес- кая 1 - наличию ошибки.

При отсутствии какого-либо из синхроимпульсов срав нение сдвигов не производится вследствие того, что в этом случае триггер 64 сохраняет на прямом выходе логический О.

В четвертом такте на синхровходы триггеров 65, 66 по входу 31 узла 50 контроля поступает сигнал 5 (фиг.2) по которому триггеры 65 и 66 принимают результат контроля и на выходы 50, 50 , 50 выдается соответств-ую- щая информация согласно таблице.,

В примерах 1 и 2 с прямого выхода триггера 65 выделяется уровень логического О, а с инверсного выхода - уровень логической 1, благодаря чему через элемент ИЛИ 55 пропуска-- ется сигнал 5g (фиг.2), поступающий на вход 29, и производится сброс всех триггеров, кроме выходных триггеров 66 и 65, сохраняющих результат контроля. Тем самым узел 50 подготавливается для проведения контроля в следующем цикле.

В примерах 3 триггера 65 уже

и 4 с прямого выхода вьщается уровень логической 1, поэтому сигнал 5 блокируется уровнем логического О, поступающим с инверсного выхода триггера 65, и сброс всех триггеров, кроме выходных триггеров 65, 66,производится уже во втором такте следующего цикла сигналом 5 (фиг,2), поступающим на вход 35 узла 50 контроля. Это вызвано необходимостью сброса лишь после проведения подстройки сдвига на один шаг, который согласно вьшеописанному принципу функционирования блока 3 производится в первом такте следующего цикла. Далее в каждом цикле работа узла 50 контроля повторяется и протекает аналогичньм образом.

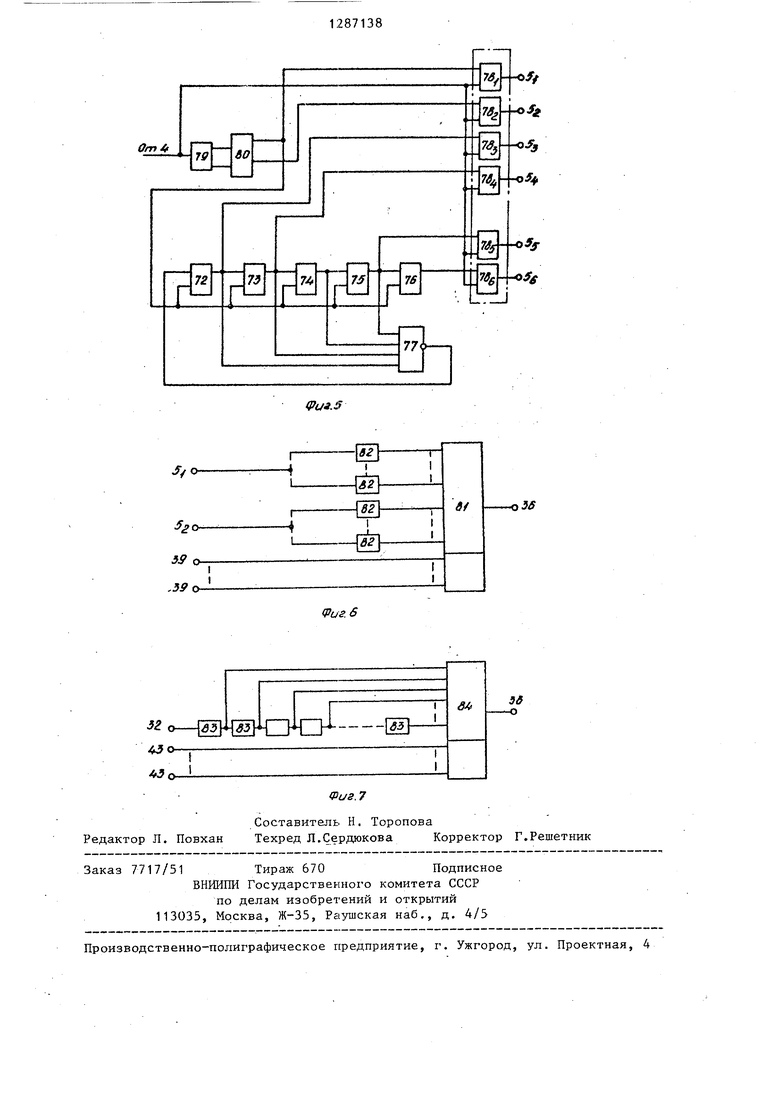

Пример реализации формирователя 5 управляющих сигналов (фиг. 5).

Задающий генератор 4 осуществляет генерацию исходной последовательност

импульсов 4,, от которой посредством 25 разнято элементарному шагу регз лировки

двухразрядного счетчика 79, дешифратора 80 и элементов И 78i и 78 формируются опорные синхроимпульсы 5.

и

5р (фиг.2).

Тригг еры 72-76 составляют пятиразрядный кольцевой сдвигающий регистр, который на пяти своих выходах формирует от одного из опорных синхроимпульсов серии сдвинутых сигналов с длг1тельностями, равными периоду опорных синхроимпульсов, и с периодом, равным 5т, где Т - период опорных синхроимпулг сов. После стробирования ЭТ1-1Х сигналов 4 по вторым входам выходных элементов И 78g-78g на выходах элементов И группы 78 выдаются сигналы согласно временной диаграмме (фиг.2). Элемент РШИ-КЕ 77 обеспечивает контроль работы кольцевого регистра, а также начальную установку триггеров при включении питания.

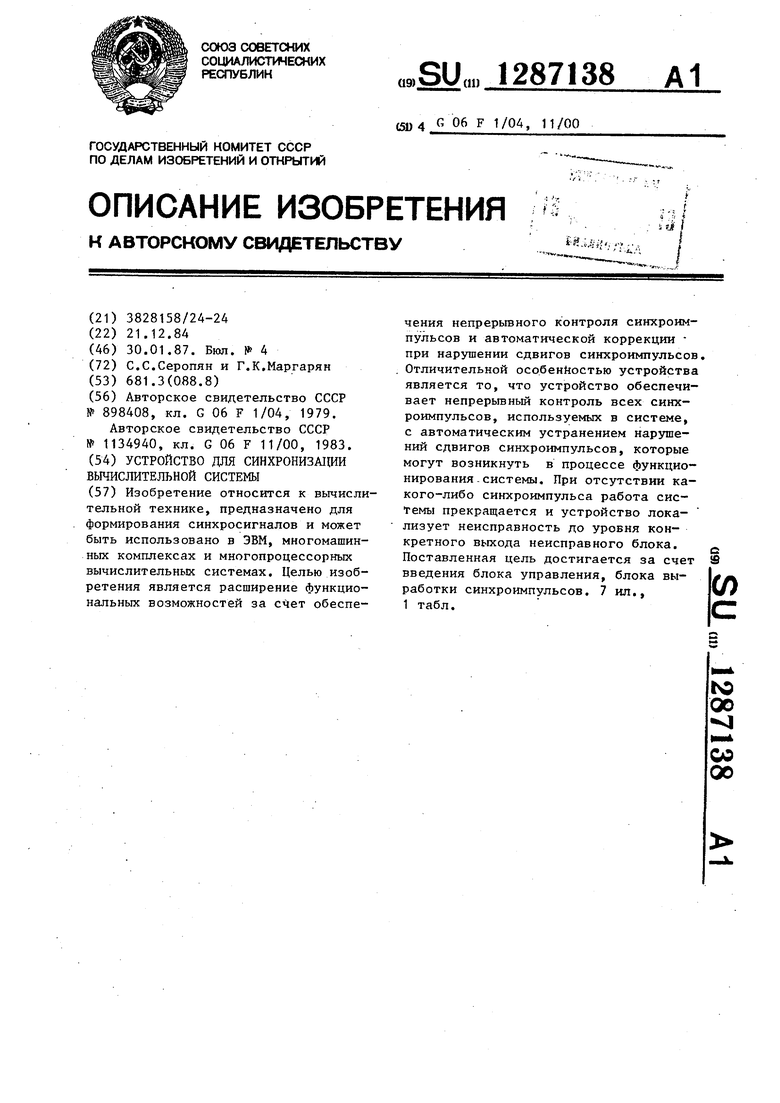

Схема формирователя эталонных синхроимпульсов (фиг.6) содержит преци- зионные элементы 82 задержки, осуществляющие задержку опорных синхроимпульсов на.необходимое время, и муль- Т1тлексор 81„ С целью обеспечения формирования синхроимпульса со сдвигом в любом интервале в течение машинного такта при использовании одинаковых элементов 82 задержки используются два опорных синхроимпульса 5 -, и 5 (фиг.2). При 5том при формировании синхроимпульса в первой половине

такта используется первый опорный синхроимпульс 55 5 а для формирования синхроимпульса во второй половине такта используется второй опорный . синхроимпульс 5 .

На входы формирователя 22 поступают опорные синхроимпульсы и, задерживаясь в прецизионных элементах 82 задержки, образуют всю временную диаграмму синхроимпульсов, используемую в устройстве, которые поступают на информационные входы мультиплексора и являются эталонньми. Благодаря подаче соответствующих кодов на адресные входы 39 мультиплексора 81 . осуществляется вьщача на выход формирователя эталонных синхроимпульсов любого эталонного сихроимпульса.

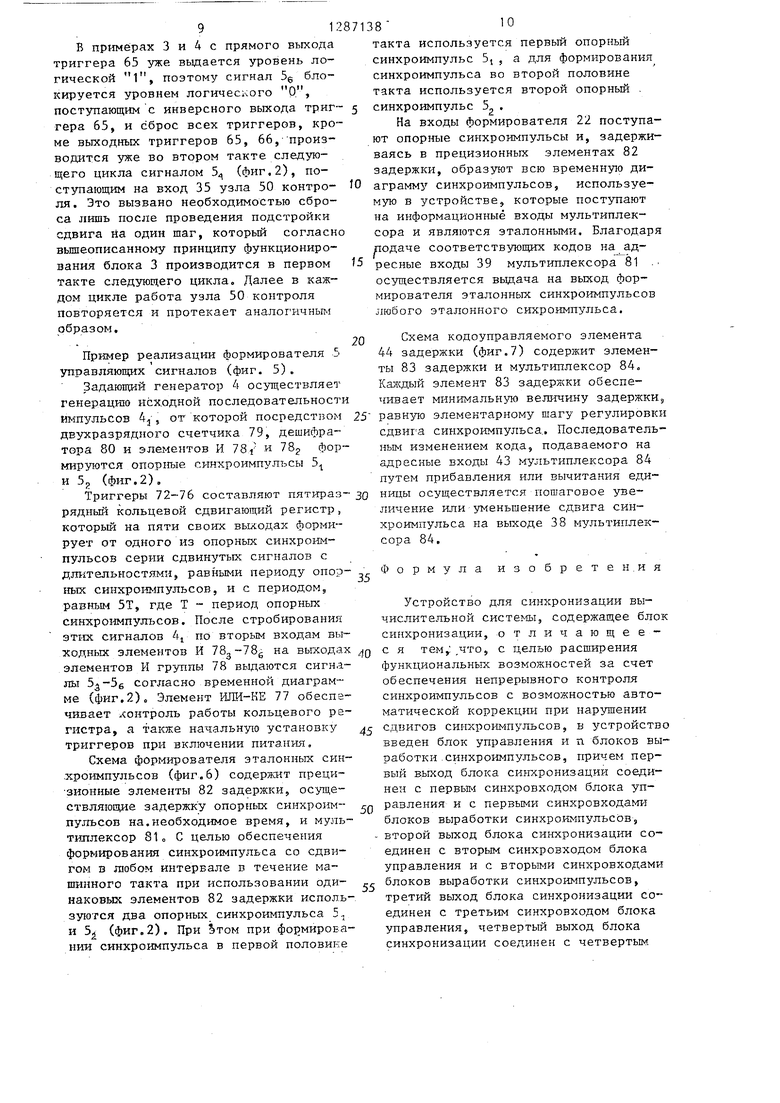

Схема кодоуправляемого элемента 44 задержки (фиг.7) содержит элементы 83 задержки и мультиплексор 84, Калсдый элемент 83 задержки обеспечивает минимальную величину задержки.

сдвига синхроимпульса.. Последователь- иьм изменением кода, подаваемого на адресные входы 43 мультиплексора 84 путем прибавления или вычитания еди- ницы осуществляется пошаговое увеличение или уменьшение сдвига синхроимпульса на выходе 38 мультиплексора 84,

Формула изобрете н.и я

Устройство для синхронизации вычислительной системы, содержащее блок синхронизации, отличающеес я тем,: .что, с целью расширения функциональных возможностей за счет обеспечения непрерывного контроля синхроимпульсов с возможностью автоматической коррекции при нарушении

сдвигов синхроимпульсов, в устройство введен блок управления и п блоков выработки .синхроимпульсов, причем первый выход блока сиьг/:ронизации соединен с первью синхровходом блока управления и с первыми синхровходами блоков выработки синхроимпульсов, второй выход блока синхронизации соединен с вторым синхровходом блока управления и с вторыми синхровходами

блоков выработки синхроимпульсов,

третий выход блока синхронизации соединен с третьим синхровходом блока управления, четвертый выход блока синхронизации соединен с четвертым

1

синхровходом блока управления и с третьими синхровходами блоков вьфа- ботки синхроимпульсов, пятый выход блока синхронизации - с четвертыми синхровходами блоков вьфаботки син- хроимпульсов, шестой выход блока синхронизации - с пятым синхровходом блока управления и с пятыми синхровходами блоков вьфаботки синхроимпульсов, вход сброса устройства сое- динен с входом сброса блока управления и с входом сброса блоков выработки синхроимпульсов, причем блок управления содержит два элемента НЕ, четьфе элемента И, два счетчика, два дешифратора, три элемента ИЛИ, мультиплексор, два элемента ИЛИ-НЕ, узел постоянной памяти, регистр, формирователь эталонных синхроимпульсов, первый синхровход формирователя эта- лонных синхроимпульсов является первым синхровходом блока, второй синхровход которого соединен с вторым синхровходом формирователя эталонных

синхроимпульсов, третий синхровход блока соединен с первыми входами первого, второго, третьего и четвертого элементов И и .с шестыми синхровходами блоков вьфаботки синхроимпульсов.

четвертый синхровход блока соединен с синхровходом регистра и с входом разрешения считывания узла постоянной памяти, пятый синхровход блока соединен с управляющим входом регистра, выходы которого соединены с адресными входами формирователя эталонных синхроимпульсов, выход которого соединен с входом эталонной последовательности блоков вьфаботки синхроимпульсов,.выходы сигналов сбоя которых соединены с входами первого элемента ИЛИ-НЕ блока управления, выход первого элемента ИЛИ-НЕ соединен с вторыми входами первого и второго элементов И, с вторым входом четвертого элемента И, выход которого соединен с первым входом первого, элемента ИЛИ, выход которого соединен с входом сброса .

первого счетчика и с первым входом

второго элемента ИЛИ, второй вход которого соединен с выходом второго элемента И и с первым входом третьего элемента РШИ, второй вход которого соединен с выходом третьего элемента И, вход сброса блока соединен с вторым входом первого элемента ИЛИ, выход второго элемента ИЛИ соединен с входом сброса второго счетчика, вы

10 t5 0

5

0

5

jc

0

0

е

38-12

ходы разрядов которого соединены соответственно с входами первого дешифратора, с первой группой адресных вхо- входов узла постоянной памяти и с группой входов разрешения выбора блоков выработки синхроимпульсов, первый выход первого дешифратора соединен с первым входом группы входов управления задержкой блоков выработки синхроимпульсов, выходы первого дешифратора с второго по (п-1)-й соединены с информационными входами с первого по (п-2)-й первого мультиплексора, п-й выход дешифратора соединен с вторым входом группы входов управления задержкой блоков вьфаботки синхроимпульсов и с (п-1)-м информационным. ,входом первого мультиплексора, выход которого соединен с входом первого элемента НЕ, выход которого соединен с третьим входом первого элемента И, выход которого соединен со счетным входом второго счетчика, выходы с . первого по (п-1)-й второго дешифратора соединены с входом запуска блоков выработки синхроимпульсов соответственно с первого (п-1)-й, п-й выход второго дешифратора соединен с входом запуска п-го блока вьфаботки синхроимпульсов, с третьим входом четвертого элемента И и с входом второго элемента НЕ, выход которого соединен с третьим входом второго элемента И, выход третьего элемента ИЛИ соединен со счетным входом первого счетчика, выходы которого соединены с входами второго дешифратора, второй группой адресных входов узла постоянной памяти, с группой адресных входов первого мультиплексора И с входами второго элемента ИЛИ-НЕ, выход которого соединен с вторым входом третьего элемента И, причем каждьй блок выработки синхроимпульсов содержит три группы элементов И, два счетчика, два элемента кодоуправляемой задержки, элемент И, коммутатор, узел контроля, причем первый синхровход блока соединен с информационным входом первого элемента кодоуправляемой задержки, группа входов управления за- держкой которого соединена с выходами разрядов счетчика, вход разрешения прямого счета которого соединен с

выходом первого элемента И первой группы, первый вход которого соединен с первьм входом второго элемента И первой группы, с первым входом первого элемента И второй группы, с первым входом второго элемента И второй группы и является четвертым синхро- входом блока, первый вход группы входов управления задержкой блока соединен с вторыми входами элементов И первой группы, второй вход группы входов управления задержкой блока соединен с вторыми входами элементов И

второй группы, вход запуска блока со- 10. выходом первого триггера, с первыми единен с первым входом элемента И, с первыми входами элементов И первой, второй и третьей групп, выход разрешения увеличения задержки узла контроля соединен с четвертым входом пер- 15 вого элемента И первой группы и с четвертым входом первого элемента И второй группы, выход разреп1ения уменьшения задержки узла контроля соединен с четвертым входом второго 20 элемента И первой группы и с.четвертьш входом второго элемента И второй группы, ВЫХОД второго элемента И первой группы соединен с входом управ-- лешю обратным счетом первого счет-- чика, выход первого элемента И второй группы соединен с входом управления прямого счета второго счетчи-- ка, вход управления обратным счетом которого соединен с выходом второго элем-гнта И второй группы, выходы разрядов второго счетчика соединены с группой входов управления задержкой второго элемента кодоуправляемой задержки, синхровход которого явля- 35 ется вторым синхровходом блока, тре25

30

входами второго и третьего элементов И и с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго триггера, второй синхровход узла соединен с синхровхо дом первого триггера и с синхровходо второго триггера, вход сброса которо го соединен с входом сброса первого триггера, с первьм входом второго эл мента иЛи и является входом начально установки узла, третий синхровход ко торого соединен с первым входом четвертого элемента И, второй вход кото рого соединен с инверсным выходом первого триггера, информационный вхо которого соединен с выходом первого

элемента И-НЕ, первый вход которого соединен с выходом третьего триггера с первым входом второго элемента И-Н и с вторым входом второго элемента И выход первого элемента И соединен с вторьм входом второго элемента ИЛИ, третий вход которого соединен с выхо дом четвертого элемента И, выход вто рого элемента ИЛИ соединен с нулевым входами третьего, четвертого, пятого и шестого триггеров и с нулевым вхо дом седьмого триггера, единичный вхо которогосоединен с выходом пятого элемента И, первый вход которого со динен с выходом пятого триггера, синхровход которого соединен с выходом первого элемента НЕ и С вторым входом, пятого элемента И, третий вхо которого соединен с выходом шестого триггера, сщжровход которого- соединен с выходом второго элемента НЕ и с четвертым входом пятого элемента И, вход эталонной последовательности узла соединен с входом первого элемента НЕ и с первым входом шестого элемента И, второй вход которого сое динен с первым входом седьмого элемента И и с выходом седьмого триггера, инверсный выход которого соединен с информационным входом вто рого триггера, вход запуска узла сое динен с вторым входом седьмого эле

тий синхровход которого соединен с первым синхровходом узла контроля, второй симхровход которого является четвертым синхровходом блока, пятый синхровход которого соединен с треть синхровходом блока контроля, вход начальной установки которого является входом сброса блока, вход эталонной последовательности которого соединен с вторым входом элемента И, выход которого соединен с входом эталонной последовательности узла контроля, вход запуска которого соединен с вы- ходом коммутатора, информационные вхды которого соединены соответственно с выходами элементов кодоуправляемых задержек и являются группой выходов блока, выход, сбоя, которого соединен с выходом сбоя узла контроля, управляющие входы коммутатора соединены с вьтходами элементов И третьей группы, вторые входы которьгх являются

ветственно входами группы входов разрешения выбора блока, причем узел контроля содержит семь триггеров, элемент ИЛИ, семь элементов И, два элемента И-ИЕ, два элемента НЕ, элемент РШИ. элемент задержки, причем первый синхровход узла соединен с первым входом первого элемента И, второй вход которого соединен с прямым

выходом первого триггера, с первыми

входами второго и третьего элементов И и с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго триггера, второй синхровход узла соединен с синхровходом первого триггера и с синхровходом второго триггера, вход сброса которого соединен с входом сброса первого триггера, с первьм входом второго элемента иЛи и является входом начальной установки узла, третий синхровход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с инверсным выходом первого триггера, информационный вход которого соединен с выходом первого

элемента И-НЕ, первый вход которого соединен с выходом третьего триггера, с первым входом второго элемента И-НЕ и с вторым входом второго элемента И, выход первого элемента И соединен с вторьм входом второго элемента ИЛИ, третий вход которого соединен с выходом четвертого элемента И, выход второго элемента ИЛИ соединен с нулевыми входами третьего, четвертого, пятого и шестого триггеров и с нулевым вхо дом седьмого триггера, единичный вход которогосоединен с выходом пятого элемента И, первый вход которого соединен с выходом пятого триггера, синхровход которого соединен с выходом первого элемента НЕ и С вторым входом, пятого элемента И, третий вход которого соединен с выходом шестого триггера, сщжровход которого- соединен с выходом второго элемента НЕ и с четвертым входом пятого элемента И, вход эталонной последовательности узла соединен с входом первого элемента НЕ и с первым входом шестого элемента И, второй вход которого соединен с первым входом седьмого элемента И и с выходом седьмого триггера, инверсный выход которого соединен с информационным входом второго триггера, вход запуска узла соединен с вторым входом седьмого эле1512871

мента И и с входом второго элемента НЕ, выход шестого элемента И соединен с единичным входом третьего триггера, выход седьмого элемента И соединен с единичным входом четвертого 5 элемента И, выход которого соединен с вторым входом первого элемента И-НЕ, с вторым входом второго элемента И-НЕ и с вторым входом третьего элемента И, выход второго элемента И-НЕ 10 соединен с входом элемента эадержки,

0 О О Ошибки нет

0 01 Отсутствие синхроимпульса

0 11 Необходимость увеличения сдвига синхроимпульса

1 01 Необходимость

уменьшения сдвига синхроимпульса

38

16

выход которого соединен с третьим входом шестого элемента И и с третьим входом седьмого элемента И, выход третьего элемента И является выходом разрешения увеличения эадержки узла, выход элемента И является выходом разрешения уменьшения задержки узла, выход первого элемента ИЛИ явля ется выходом сбоя узла, информационные входы пятого и шеетого триггеров соединены с шиной.единичного потенциала узла.

f Ттп П

38

38

JlJгr JlJlллJlЛJгпJln

h.

ЛП

ЛQ.

п пп

л

k

Se

Jl

24 о

фие.7

П

Q.

Е:

п пп

л

k

JI

П

Фиб. 2

ге

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации вычислительной системы | 1984 |

|

SU1221648A1 |

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU974364A1 |

| Устройство для синхронизации вычислительной системы | 1983 |

|

SU1129597A1 |

| Устройство для контроля цифровых узлов | 1982 |

|

SU1059576A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Устройство для контроля синхронизации | 1983 |

|

SU1200268A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1410037A1 |

| Устройство дефектоскопического контроля планарных структур | 1987 |

|

SU1460610A1 |

| Устройство для поиска перемежающихся неисправностей | 1986 |

|

SU1381511A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

Изобретение относится к вычислительной технике, предназначено для формирования синхросигналов и может быть использовано в ЭВМ, многомашинных комплексах и многопроцессорных вычислительных системах. Целью изобретения является расширение функциональных возможностей за обеспечения непрерьтного контроля синхроимпульсов и автоматической коррекции при нарушении сдвигов синхроимпульсов. Отличительной особенностью устройства является то, что устройство обеспечивает непрерывньй контроль всех синхроимпульсов, используемых в системе, с автоматическим устранением нарушений сдвигов синхроимпульсов, которые могут возникнуть в процессе функционирования-системы. При отсутствии какого-либо синхроимпульса работа системы прекращается и устройство локализует неисправность до уровня конкретного выхода неисправного блока. Поставленная цель достигается за счет введения блока управления, блока выработки синхроимпульсов. 7 ил., 1 табл. (Л с го 00 со 00

4в 4fjr/9

lO

fff,

Omfe

80

7S

7«

..11 М..||... I I IГ

О- ii№rtZWZH-

Фиг.7

Составитель Н. Торопова Редактор Л. Повхан Техред Л.Сердюкова Корректор Г.Решетник

Заказ 7717/51 Тираж 670Подписное

ВНЙИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Рс1ушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

74

--0//

7Л

1--ОЛ

%--o

15

LU

t.b

Щ

Atf

Sd

| Устройство для синхронизации блоков вычислительной системы | 1979 |

|

SU898408A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля блоков синхронизации | 1983 |

|

SU1134940A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-30—Публикация

1984-12-21—Подача