Изобретение относится к вычислитель- эй технике, в частности к.устройствам управления внешней памятью, и может быть использовано для расширения адресного пространства микроЭВМ при адресации па- м|яти данных, носящих произвольно-последовательный характер.

Цель изобретения - повышение быстро- дэйствия устройства.

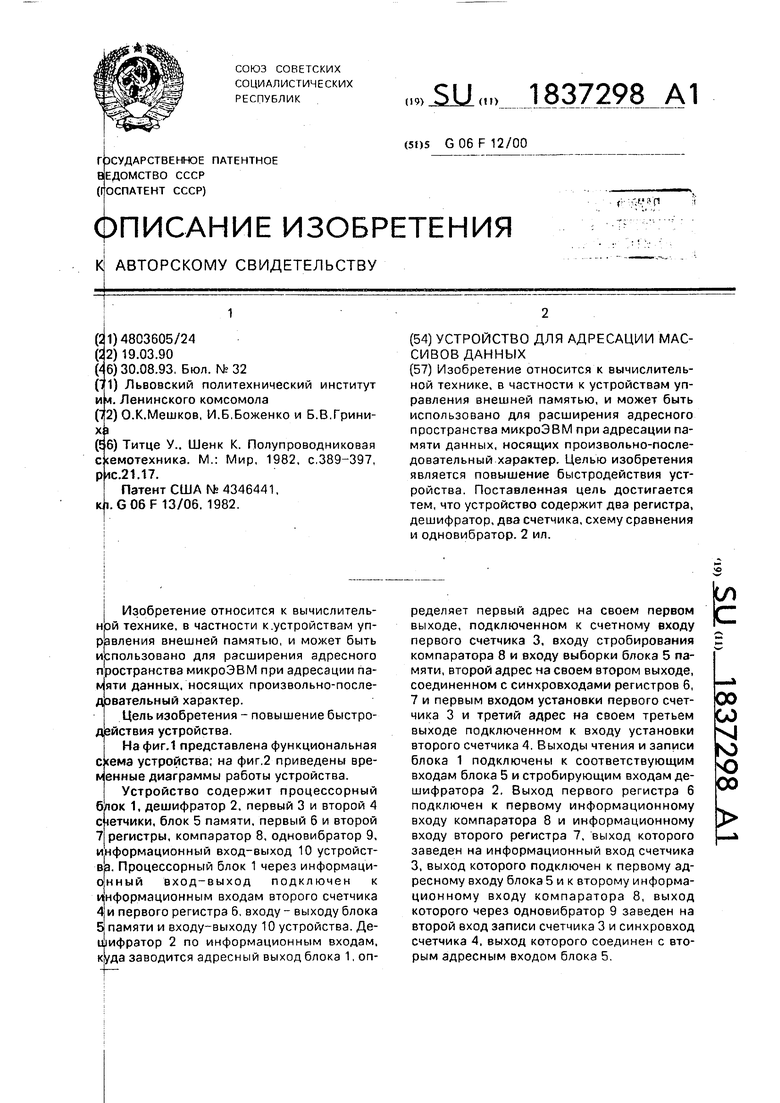

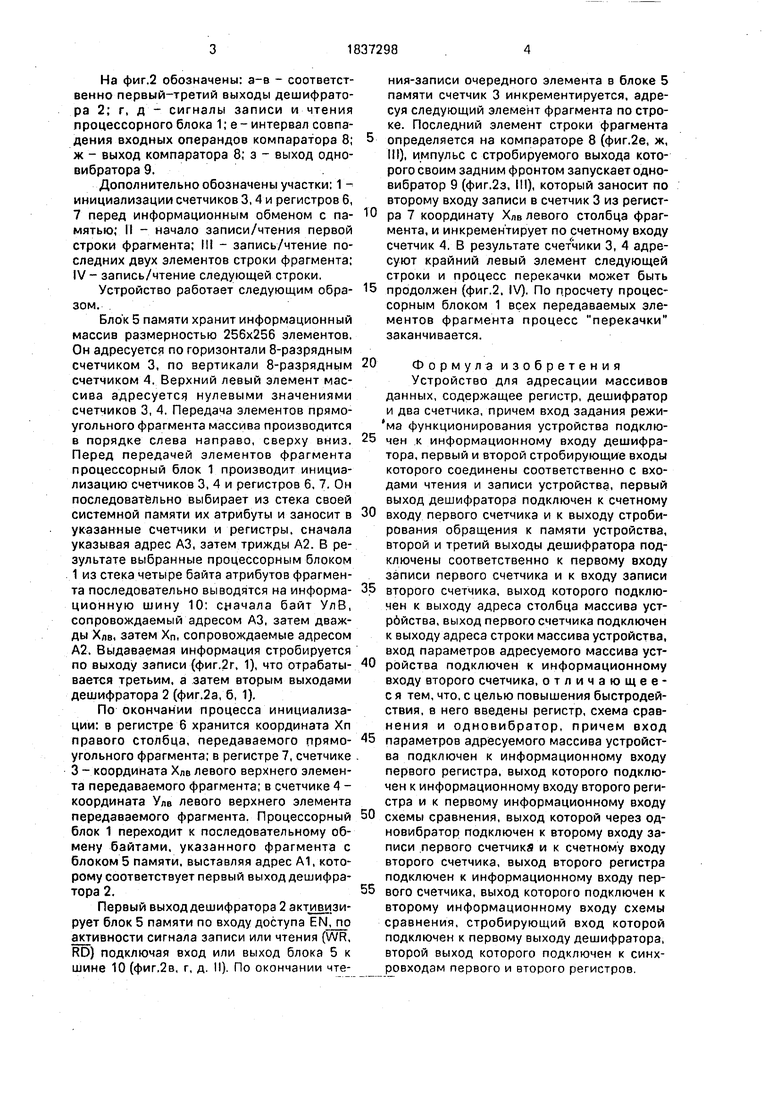

Нафиг.1 представлена функциональная схема устройства; на фиг.2 приведены временные диаграммы работы устройства.

Устройство содержит процессорный блок 1, дешифратор 2. первый 3 и второй 4 счетчики, блок 5 памяти, первый 6 и второй 7 регистры, компаратор 8, одновибратор 9, информационный вход-выход 10 устройства. Процессорный блок 1 через информационный вход-выход подключен к информационным входам второго счетчика

4и первого регистра 6, входу - выходу блока

5памяти и входу-выходу 10 устройства. Дешифратор 2 по информационным входам, куда заводится адресный выход блока 1, определяет первый адрес на своем первом выходе, подключенном к счетному входу первого счетчика 3, входу стробирования компаратора 8 и входу выборки блока 5 памяти, второй адрес на своем втором выходе, соединенном с синхровходами регистров 6, 7 и первым входом установки первого счетчика 3 и третий адрес на своем третьем выходе подключенном к входу установки второго счетчика 4. Выходы чтения и записи блока 1 подключены к соответствующим входам блока 5 и стробирующим входам дешифратора 2. Выход первого регистра 6 подключен к первому информационному входу компаратора 8 и информационному входу второго регистра 7, выход которого заведен на информационный вход счетчика 3, выход которого подключен к первому адресному входу блока 5 и к второму информационному входу компаратора 8, выход которого через одновибратор 9 заведен на второй вход записи счетчика 3 и синхровход счетчика 4, выход которого соединен с вторым адресным входом блока 5.

Ј

00 GJ

|

N3 О С

На фиг.2 обозначены: а-в - соответственно первый-третий выходы дешифратора 2; г, д - сигналы записи и чтения процессорного блока 1; е - интервал совпадения входных операндов компаратора 8; ж - выход компаратора 8; з - выход одно- вибратора 9.

Дополнительно обозначены участки: 1 - инициализации счетчиков 3,4 и регистров 6, 7 перед информационным обменом с памятью; II - начало записи/чтения первой строки фрагмента; III - запись/чтение последних двух элементов строки фрагмента; IV - запись/чтение следующей строки.

Устройство работает следующим образом. .

Блок 5 памяти хранит информационный массив размерностью 256x256 элементов. Он адресуется по горизонтали 8-разрядным счетчиком 3. по вертикали 8-разрядным счетчиком 4. Верхний левый элемент массива адресуется нулевыми значениями счетчиков 3, 4. Передача элементов прямоугольного фрагмента массива производится в порядке слева направо, сверху вниз. Перед передачей элементов фрагмента процессорный блок 1 производит инициализацию счетчиков 3, 4 и регистров 6, 7. Он последовательно выбирает из стека своей системной памяти их атрибуты и заносит в указанные счетчики и регистры, сначала указывая адрес A3, затем трижды А2. В результате выбранные процессорным блоком 1 из стека четыре байта атрибутов фрагмента последовательно выводятся на информационную шину 10: сначала байт УлВ, сопровождаемый адресом A3, затем дважды Хлв, затем Хп, сопровождаемые адресом А2. Выдаваемая информация стробируется по выходу записи (фиг.2г, 1), что отрабатывается третьим, а затем вторым выходами дешифратора 2 (фиг.2а, б, 1).

По окончании процесса инициализации: в регистре 6 хранится координата Хп правого столбца, передаваемого прямоугольного фрагмента; в регистре 7, счетчике 3 - координата Хлв левого верхнего элемента передаваемого фрагмента; в счетчике 4 - координата Улв левого верхнего элемента передаваемого фрагмента. Процессорный блок 1 переходит к последовательному обмену байтами, указанного фрагмента с блоком 5 памяти, выставляя адрес А1, которому соответствует первый выход дешифратора 2.

Первый выход дешифратора 2 активизирует блок 5 памяти по входу доступа EN. по активности сигнала записи или чтения (WR, RD) подключая вход или выход блока 5 к шине 10 (фиг,2в, г, д. II). По окончании чтения-записи очередного элемента в блоке 5 памяти счетчик 3 инкрементируется, адресуя следующий элемент фрагмента по строке. Последний элемент строки фрагмента

определяется на компараторе 8 (фиг.2е, ж, III), импульс с стробируемого выхода которого своим задним фронтом запускает одно- вибратор 9 (фиг.2з, III), который заносит по второму входу записи в счетчик 3 из регистра 7 координату Хлв левого столбца фрагмента, и инкрементирует по счетному входу счетчик 4. В результате счетчики 3, 4 адресуют крайний левый элемент следующей строки и процесс перекачки может быть

продолжен (фиг.2. IV). По просчету процессорным блоком 1 всех передаваемых элементов фрагмента процесс перекачки заканчивается.

Формул а изобретения

Устройство для адресации массивов

данных, содержащее регистр, дешифратор

и два счетчика, причем вход задания режи ма функционирования устройства подключен .к информационному входу дешифратора, первый и второй стробирующие входы которого соединены соответственно с входами чтения и записи устройства, первый выход дешифратора подключен к счетному

входу первого счетчика и к выходу строби- рования обращения к памяти устройства, второй и третий выходы дешифратора подключены соответственно к первому входу записи первого счетчика и к входу записи

второго счетчика, выход которого подключен к выходу адреса столбца массива уст- рбйства, выход первого счетчика подключен к выходу адреса строки массива устройства, вход параметров адресуемого массива устройства подключен к информационному входу второго счетчика, отличающее- с я тем, что, с целью повышения быстродействия, в него введены регистр, схема сравнения и одновибратор, причем вход

параметров адресуемого массива устройства подключен к информационному входу первого регистра, выход которого подключен к информационному входу второго регистра и к первому информационному входу

схемы сравнения, выход которой через одновибратор подключен к второму входу записи первого счетчика и к счетному входу второго счетчика, выход второго регистра подключен к информационному входу первого счетчика, выход которого подключен к второму информационному входу схемы сравнения, стробирующий вход которой подключен к первому выходу дешифратора, второй выход которого подключен к синх- ровходам первого и второго регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля печатных плат | 1986 |

|

SU1472929A1 |

| ЭВМ | 1990 |

|

RU2024928C1 |

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| Формирователь страниц для голографического запоминающего устройства | 1986 |

|

SU1388948A1 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

| Буферное запоминающее устройство с произвольной выборкой двумерного фрагмента | 1986 |

|

SU1444784A1 |

| Устройство для вычисления свертки | 1990 |

|

SU1709342A1 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

Изобретение относится к вычислительной технике, в частности к устройствам управления внешней памятью, и может быть использовано для расширения адресного пространства микроЭВМ при адресации памяти данных, носящих произвольно-последовательный характер. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит два регистра, дешифратор, два счетчика, схему сравнения и одновибратор. 2 ил.

Авторы

Даты

1993-08-30—Публикация

1990-03-19—Подача