при этом группа входов данных регистра соединена с группой входов постоянной памяти, группа адресных входов которой и группа входов данных второго мультиплексора соединены с выходами счетчика, синх- ровходы постоянной памяти, регистра, первого и второго регистров сдвига и вторая группа входов блока управления циклами памяти и счетный вход счетчика соединены с соответствующими выходами генератора импульсов, выход первого регистра адреса соединен с адресным входом первой оперативной памяти, а входы данных первого и второго регистров адреса, вход данных второй оперативной памяти и выход второго буферного регистра соединены с внутренней шиной данных устройства, выходы второго мультиплексора и второго регистра адреса соединены с входом адреса второй оперативной памяти, выход которой соединен с входами данных второго буферного регистра и второго регистра сдвига, выход которого соединен с входом четвертого блока усилителей, синхровходы первого и второго мультиплексоров и первый вход блока управления соединены с четвертым выходом блока управления циклами памяти, первый и второй выходы которого соединены с вторым и третьим входами блока управления, четвертый и пятый выходы которого через пятый блок усилителей соединены с управляющей шиной микроЭВМ, а шестой выход - с четвертым входом блока управления циклами памяти, пятый выход которого соединен с управляющим входом второго регистра сдвига, управляющие и синхровходы первого и второго регистров адреса соединены соответственно с седьмым выходом блока управления и выходом первого блока усилителей, управляющий и синхровход второго буферного регистра соединены соответственно с первым выходом блока управления циклами памяти и третьим выходом блока управления, группа управляющих входов второй оперативной памяти соединена с третьим выходом блока управления циклами памяти, управляющий вход второго мультиплексора соединен с вторым выходом блока управления, четвертый вход блока управления соединен с внутренней шиной данных устройства.

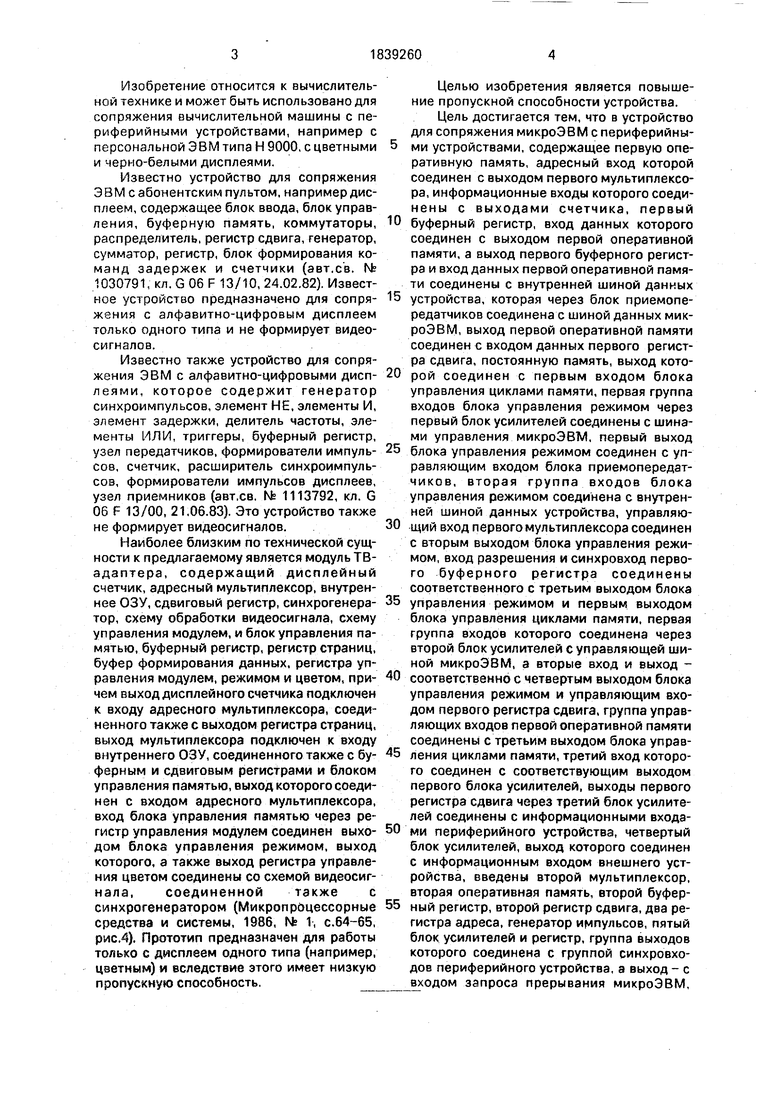

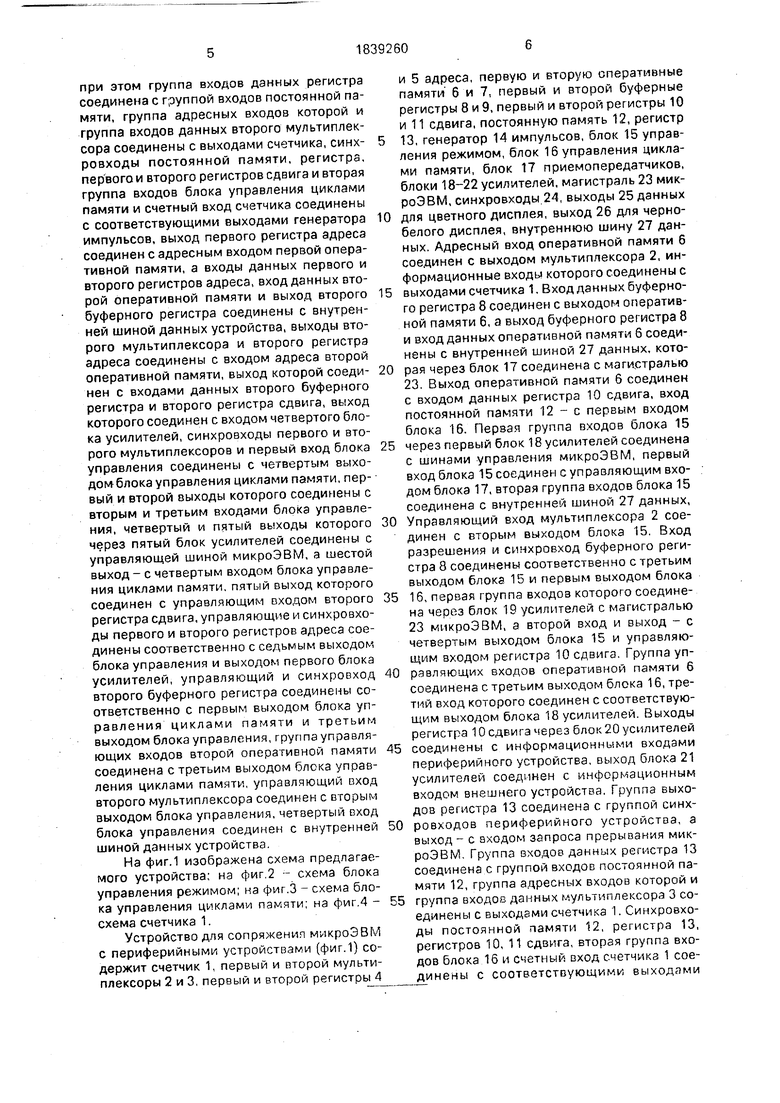

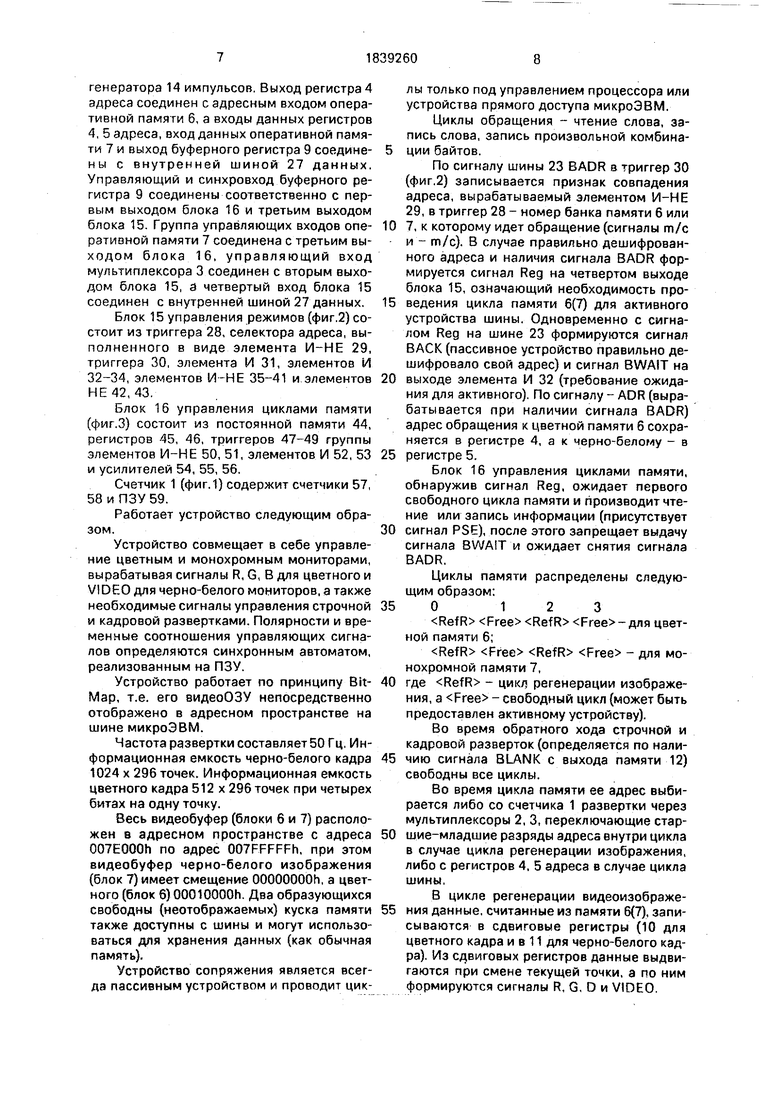

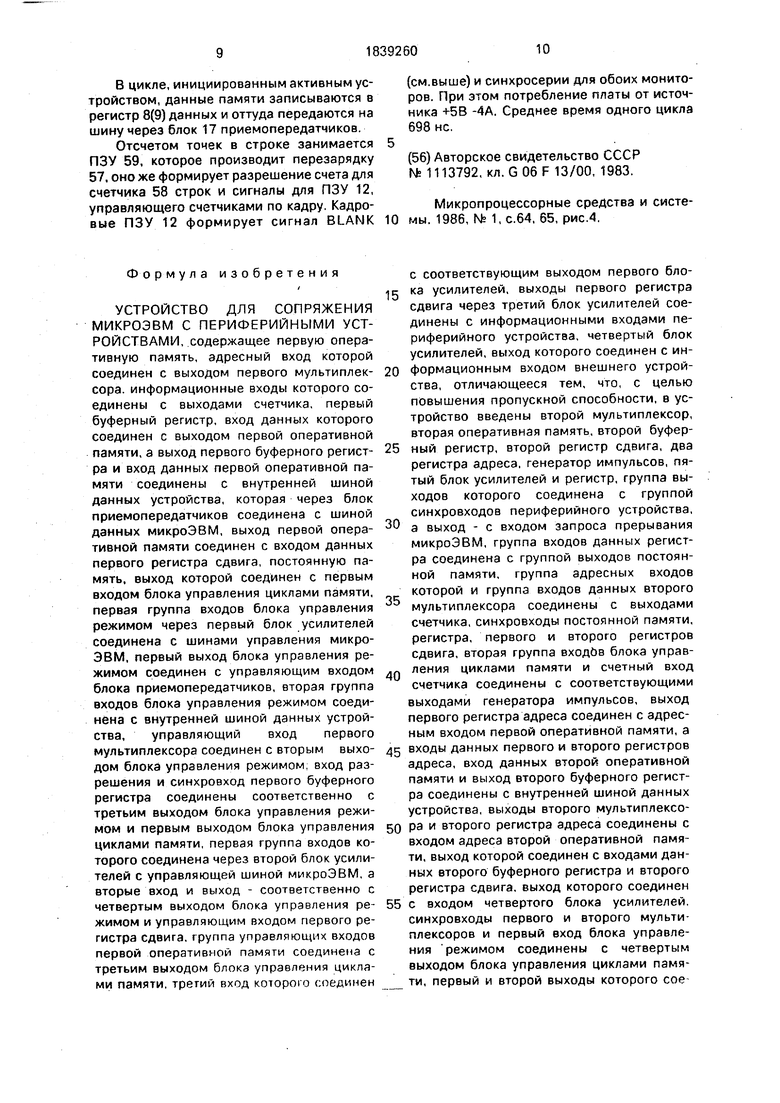

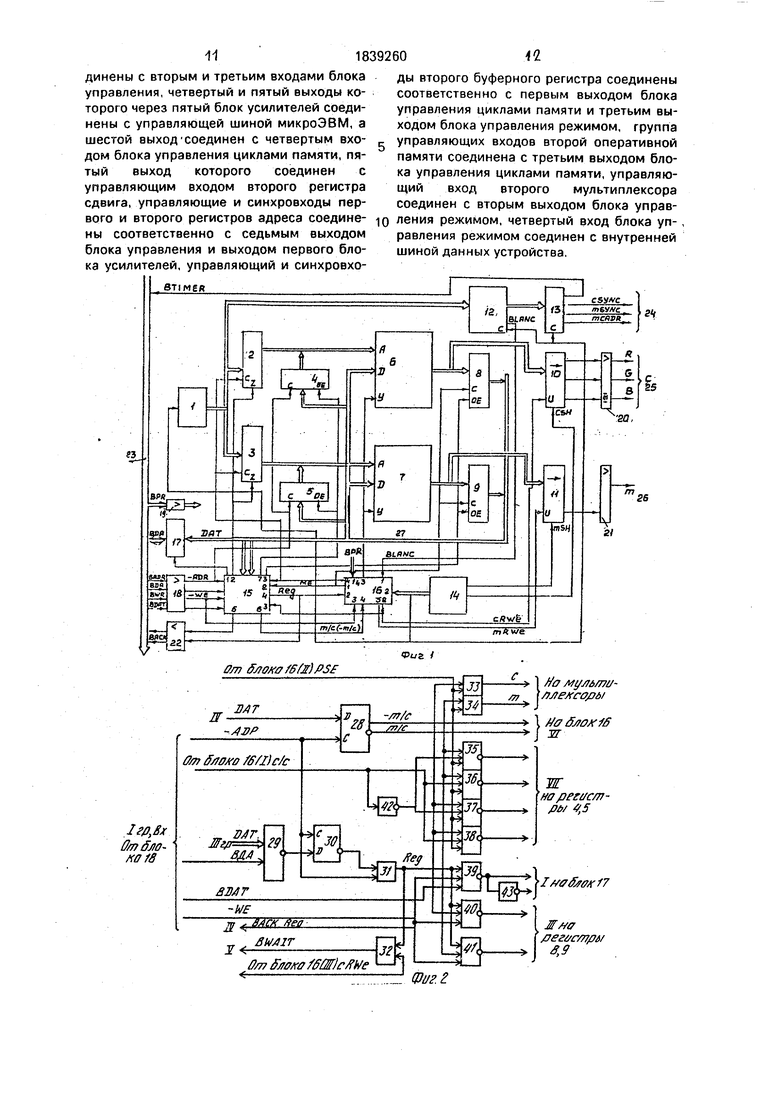

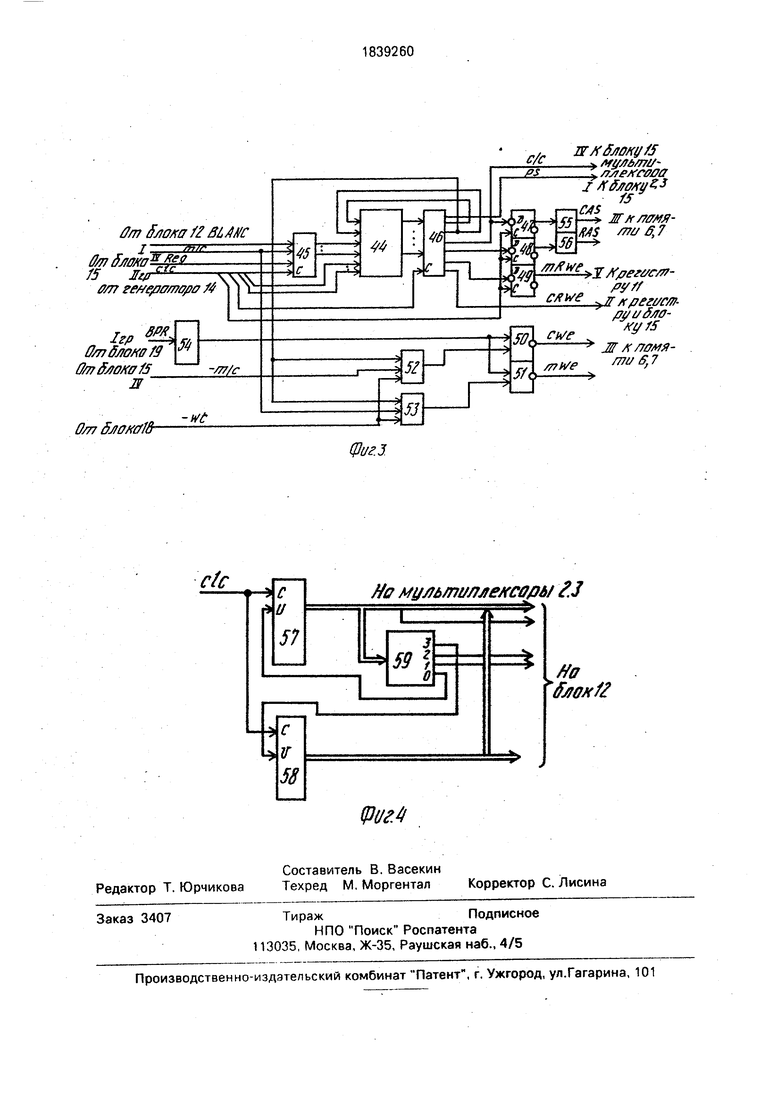

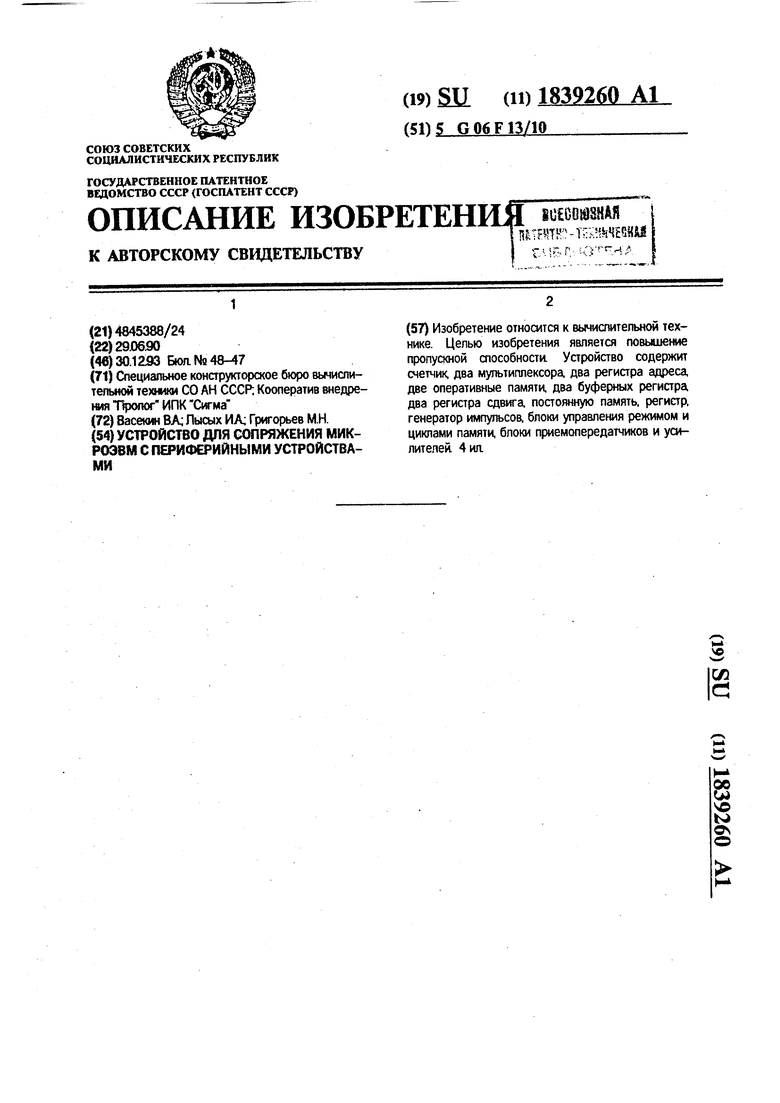

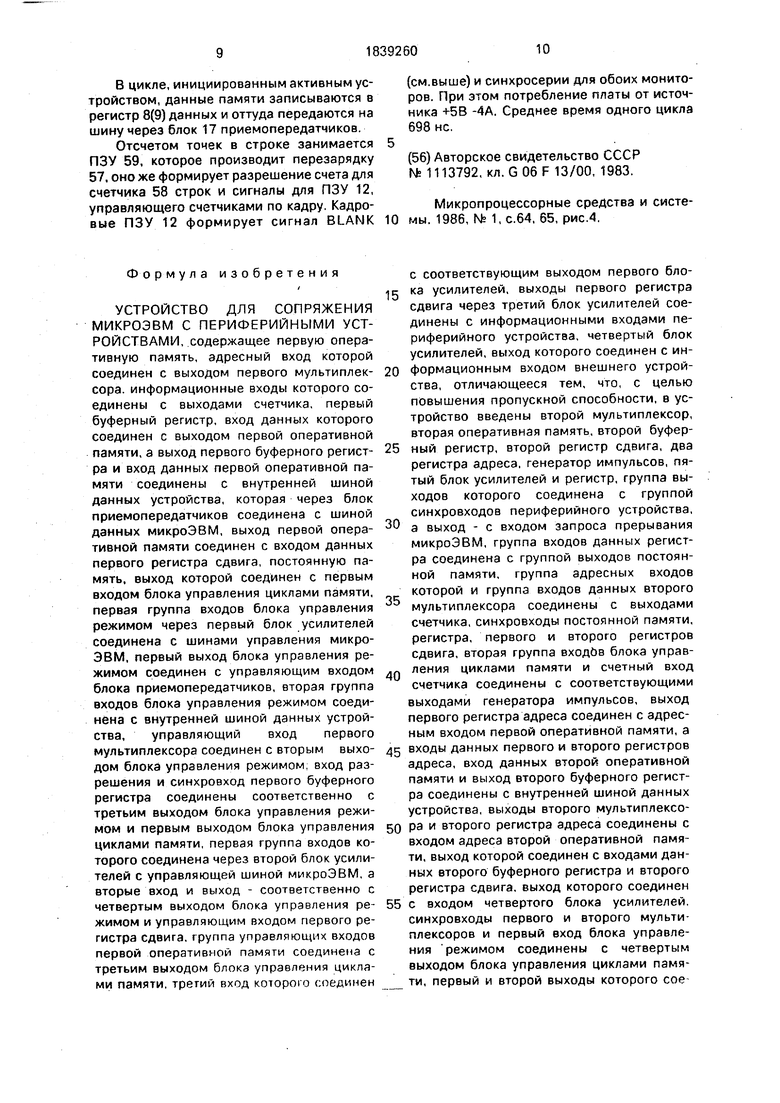

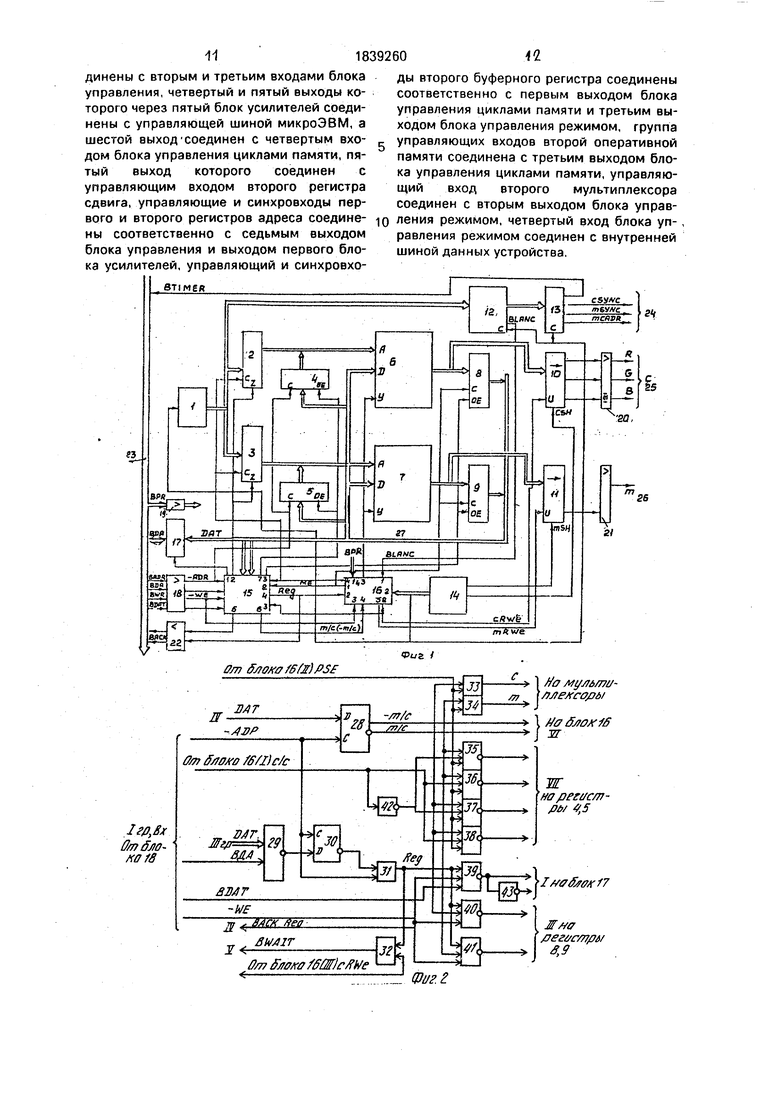

На фиг.1 изображена схема предлагаемого устройства; на фиг.2 - схема блока управления режимом; на фиг.З - схема блока управления циклами памяти; на фиг.4 - схема счетчика 1.

Устройство для сопряжения микроЭВМ с периферийными устройствами (фиг.1) содержит счетчик 1, первый и второй мультиплексоры 2 и 3, первый и второй регистры 4

и 5 адреса, первую и вторую оперативные памяти 6 и 7, первый и второй буферные регистры 8 и 9, первый и второй регистры 10 и 11 сдвига, постоянную память 12, регистр 5 13, генератор 14 импульсов, блок 15 управления режимом, блок 16 управления циклами памяти, блок 17 приемопередатчиков, блоки 18-22 усилителей, магистраль 23 микроЭВМ, синхровходы 24, выходы 25 данных

0 для цветного дисплея, выход 26 для черно- белого дисплея, внутреннюю шину 27 данных. Адресный вход оперативной памяти б соединен с выходом мультиплексора 2, информационные входы которого соединены с

5 выходами счетчика 1, Вход данных буферного регистра 8 соединен с выходом оперативной памяти 6, а выход буферного регистра 8 и вход данных оперативной памяти 6 соединены с внутренней шиной 27 данных, кото0 рая через блок 17 соединена с магистралью 23. Выход оперативной памяти 6 соединен с входом данных регистра 10 сдвига, вход постоянной памяти 12 - с первым входом блока 16. Первая группа входов блока 15

5 через первый блок 18 усилителей соединена с шинами управления микроЭВМ, первый вход блока 15 соединен с управляющим входом блока 17, вторая группа входов блока 15 соединена с внутренней шиной 27 данных,

0 Управляющий вход мультиплексора 2 соединен с вторым выходом блока 15. Вход разрешения и синхровход буферного регистра 8 соединены соответственно с третьим выходом блока 15 и первым выходом блока

5 16, первая группа входов которого соединена через блок 19 усилителей с магистралью 23 микроЭВМ, а второй вход и выход - с четвертым выходом блока 15 и управляющим входом регистра 10 сдвига. Группа уп0 равляющих входов оперативной памяти 6 соединена с третьим выходом блока 16, третий вход которого соединен с соответствующим выходом блока 18 усилителей. Выходы регистра 10 сдвига через блок 20 усилителей

5 соединены с информационными входами периферийного устройства, выход блока 21 усилителей соединен с информационным входом внешнего устройства. Группа выходов регистра 13 соединена с группой синх0 ровходов периферийного устройства, а выход - с входом запроса прерывания микроЭВМ. Группа входов данных регистра 13 соединена с группой входов постоянной памяти 12, группа адресных входов которой и

5 группа входов данных мультиплексора 3 соединены с выходами счетчика 1. Синхровходы постоянной памяти 12, регистра 13, регистров 10, 11 сдвига, вторая группа входов блока 16 и счетный аход счетчика 1 соединены с соответствующими выходами

генератора 14 импульсов. Выход регистра 4 адреса соединен с адресным входом оперативной памяти 6, а входы данных регистров 4, 5 адреса, вход данных оперативной памяти 7 и выход буферного регистра 9 соедине- ны с внутренней шиной 27 данных. Управляющий и синхровход буферного регистра 9 соединены соответственно с первым выходом блока 16 и третьим выходом блока 15. Группа управляющих входов оперативной памяти 7 соединена с третьим вы- ходом блока 16, управляющий вход мультиплексора 3 соединен с вторым выходом блока 15, а четвертый вход блока 15 соединен с внутренней шиной 27 данных.

Блок 15 управления режимов (фиг.2) состоит из триггера 28, селектора адреса, выполненного в виде элемента И-НЕ 29, триггера 30, элемента И 31, элементов И 32-34, элементов И-НЕ 35-41 и элементов НЕ 42, 43.

Блок 16 управления циклами памяти (фиг.З) состоит из постоянной памяти 44, регистров 45, 46, триггеров 47-49 группы элементов И-НЕ 50, 51, элементов И 52, 53 и усилителей 54, 55, 56.

Счетчик 1 (фиг. 1) содержит счетчики 57, 58 и ПЗУ 59.

Работает устройство следующим образом.

Устройство совмещает в себе управление цветным и монохромным мониторами, вырабатывая сигналы R, G, В для цветного и VIDEO для черно-белого мониторов, а также необходимые сигналы управления строчной и кадровой развертками. Полярности и временные соотношения управляющих сигналов определяются синхронным автоматом, реализованным на ПЗУ.

Устройство работает по принципу Bit- Map, т.е. его видеоОЗУ непосредственно отображено в адресном пространстве на шине микроЭВМ.

Частота развертки составляет 50 Гц, Информационная емкость черно-белого кадра 1024 х 296 точек. Информационная емкость цветного кадра 512 х 296 точек при четырех битах на одну точку.

Весь видеобуфер (блоки 6 и 7) расположен а адресном пространстве с адреса 007EOOOh по адрес 007FFFFFh, при этом видеобуфер черно-белого изображения (блок 7) имеет смещение OOOOOOOOh, а цветного (блок 6) ОООЮОООЬ. Два образующихся свободны (неотображаемых) куска памяти также доступны с шины и могут использоваться для хранения данных (как обычная память).

Устройство сопряжения является всегда пассивным устройством и проводит циклы только под управлением процессора или устройства прямого доступа микроЭВМ.

Циклы обращения - чтение слова, запись слова, запись произвольной комбинации байтов.

По сигналу шины 23 BADR з триггер 30 (фиг.2) записывается признак совпадения адреса, вырабатываемый элементом И-НЕ 29, в триггер 28 - номер банка памяти 6 или

0 7, к которому идет обращение (сигналы т/с и - т/с). В случае правильно дешифрованного адреса и наличия сигнала BADR формируется сигнал Reg на четвертом выходе блока 15, означающий необходимость про5 ведения цикла памяти 6(7) для активного устройства шины. Одновременно с сигналом Reg на шине 23 формируются сигнал BACK (пассивное устройство правильно дешифровало свой адрес) и сигнал BWAIT на

0 выходе элемента И 32 (требование ожидания для активного). По сигналу - ADR (вырабатывается при наличии сигнала BADR) адрес обращения к цветной памяти 6 сохраняется в регистре 4, а к черно-белому - в

5 регистре 5.

Блок 16 управления циклами памяти, обнаружив сигнал Reg, ожидает первого свободного цикла памяти и производит чтение или запись информации (присутствует

0 сигнал PSE), после этого запрещает выдачу сигнала BWAIT и ожидает снятия сигнала BADR.

Циклы памяти распределены следующим образом:

5 0123

Ref R Free RefR Free - для цветной памяти 6;

RefR Free RefR Free - для монохромной памяти 7,

0 где RefR - цикл регенерации изображения, a Free - свободный цикл (может быть предоставлен активному устройству).

Во время обратного хода строчной и кадровой разверток (определяется по нали5 чию сигнала BLANK с выхода памяти 12) свободны все циклы.

Во время цикла памяти ее адрес выбирается либо со счетчика 1 развертки через мультиплексоры 2, 3, переключающие стар0 шие-младшие разряды адреса внутри цикла в случае цикла регенерации изображения, либо с регистров 4, 5 адреса в случае цикла шины,

В цикле регенерации видеоизобрзже5 ния данные, считанные из памяти 6(7), записываются в сдвиговые регистры (10 для цветного кадра и в 11 для черно-белого кадра). Из сдвиговых регистров данные выдвигаются при смене текущей точки, а по ним формируются сигналы R, G, D и VIDEO.

В цикле, инициированным активным устройством, данные памяти записываются в регистр 8(9) данных и оттуда передаются на шину через блок 17 приемопередатчиков.

Отсчетом точек в строке занимается ПЗУ 59, которое производит перезарядку 57, оно же формирует разрешение счета для счетчика 58 строк и сигналы для ПЗУ 12, управляющего счетчиками по кадру. Кадровые ПЗУ 12 формирует сигнал BLANK

(см.выше) и синхросерии для обоих мониторов. При этом потребление платы от источника +5В -4А. Среднее время одного цикла 698 не,

(56) Авторское свидетельство СССР № 1113792, кл. G 06 F 13/00, 1983.

Микропроцессорные средства и систе- мы. 1986, N 1. с.64, 65, рис.4.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для отображения графической информации на экране цветного телевизионного индикатора | 1990 |

|

SU1836719A3 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство ввода-вывода с контролем ошибок и индикацией | 1989 |

|

SU1728866A1 |

| Буферное устройство для передачи данных | 1987 |

|

SU1418725A1 |

Формула изобретения

/

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ МИКРОЭВМ С ПЕРИФЕРИЙНЫМИ УСТРОЙСТВАМИ, содержащее первую оперативную память, адресный вход которой соединен с выходом первого мультиплексора, информационные входы которого соединены с выходами счетчика, первый буферный регистр, вход данных которого соединен с выходом первой оперативной памяти, а выход первого буферного регистра и вход данных первой оперативной памяти соединены с внутренней шиной данных устройства, которая через блок приемопередатчиков соединена с шиной данных микроЭВМ, выход первой оперативной памяти соединен с входом данных первого регистра сдвига, постоянную память, выход которой соединен с первым входом блока управления циклами памяти, первая группа входов блока управления режимом через первый блок усилителей соединена с шинами управления микро- ЭВМ, первый выход блока управления режимом соединен с управляющим входом блока приемопередатчиков, вторая группа входов блока управления режимом соединена с внутренней шиной данных устройства, управляющий вход первого мультиплексора соединен с вторым выходом блока управления режимом; вход разрешения и синхровход первого буферного регистра соединены соответственно с третьим выходом блока управления режимом и первым выходом блока управления циклами памяти, первая группа входов которого соединена через второй блок усилителей с управляющей шиной микроЭВМ, а вторые вход и выход - соответственно с четвертым выходом блока управления режимом и управляющим входом первого регистра сдвига, группа управляющих входов первой оперативной памяти соединена с третьим выходом блока управления циклами памяти, третий вход которого соединен

с соответствующим выходом первого блока усилителей, выходы первого регистра сдвига через третий блок усилителей соединены с информационными входами периферийного устройства, четвертый блок усилителей, выход которого соединен с информационным входом внешнего устройства, отличающееся тем, что, с целью повышения пропускной способности, в устройство введены второй мультиплексор, вторая оперативная память, второй буферный регистр, второй регистр сдвига, два регистра адреса, генератор импульсов, пятый блок усилителей и регистр, группа выходов которого соединена с группой синхровходов периферийного устройства,

а выход - с входом запроса прерывания микроЭВМ, группа входов данных регистра соединена с группой выходов постоянной памяти, группа адресных входов которой и группа входов данных второго мультиплексора соединены с выходами счетчика, синхровходы постоянной памяти, регистра, первого и второго регистров сдвига, вторая группа входив блока управ

ления циклами памяти и счетный вход

счетчика соединены с соответствующими выходами генератора импульсов, выход первого регистра адреса соединен с адресным входом первой оперативной памяти, а

входы данных первого и второго регистров адреса, вход данных второй оперативной памяти и выход второго буферного регистра соединены с внутренней шиной данных устройства, выходы второго мультиплексоРа и второго регистра адреса соединены с входом адреса второй оперативной памяти, выход которой соединен с входами данных второго буферного регистра и второго регистра сдвига, выход которого соединен

с входом четвертого блока усилителей, синхровходы первого и второго мультиплексоров и первый вход блока управления режимом соединены с четвертым выходом блока управления циклами памяти, первый и второй выходы которого сое

2г0,Јх fffffSjJOXfffS

Ж

наремс/я- fltr/ 4,5

Z#fffoffXf7

Ж на 0ег#с/ядб/ ,

0/rt S/iOffff fZSUffC I,,,fnec.

/ г /i ff/vfaffmlLjjJL

fc jr.33Ј-.

fS Iw™W 0m geffqaffmepo 4

T.W

Izp О/лдлоко/9

O/nfaoxofS

&

/rrSJtoxfftfr

r/. ДГ/сйгмуЯ

±fЈ Mffff6ff7l/

ллехсяда JXfaowZ fS

cc - жхяамя- Ц-MS /ли 6,7

JO -

tWyXSsewey py/f

c/twe ff- xpett/c/n. ffffi/S/ro- xyfS

-Ы-™ yf5

3U ---- ж /f rtfftf - mu St7

ff /ям %$tu----

фиг.З.

#ff

faoxfl

Авторы

Даты

1993-12-30—Публикация

1990-06-29—Подача