Изобретение относится к вычислительной технике и может быть использовано в аппаратуре передачи, приема и обработки информации.

Целью изобретения является расширение функциональной возможностей путем обеспечения повторной передачи пакета информации и его динамической индикации.

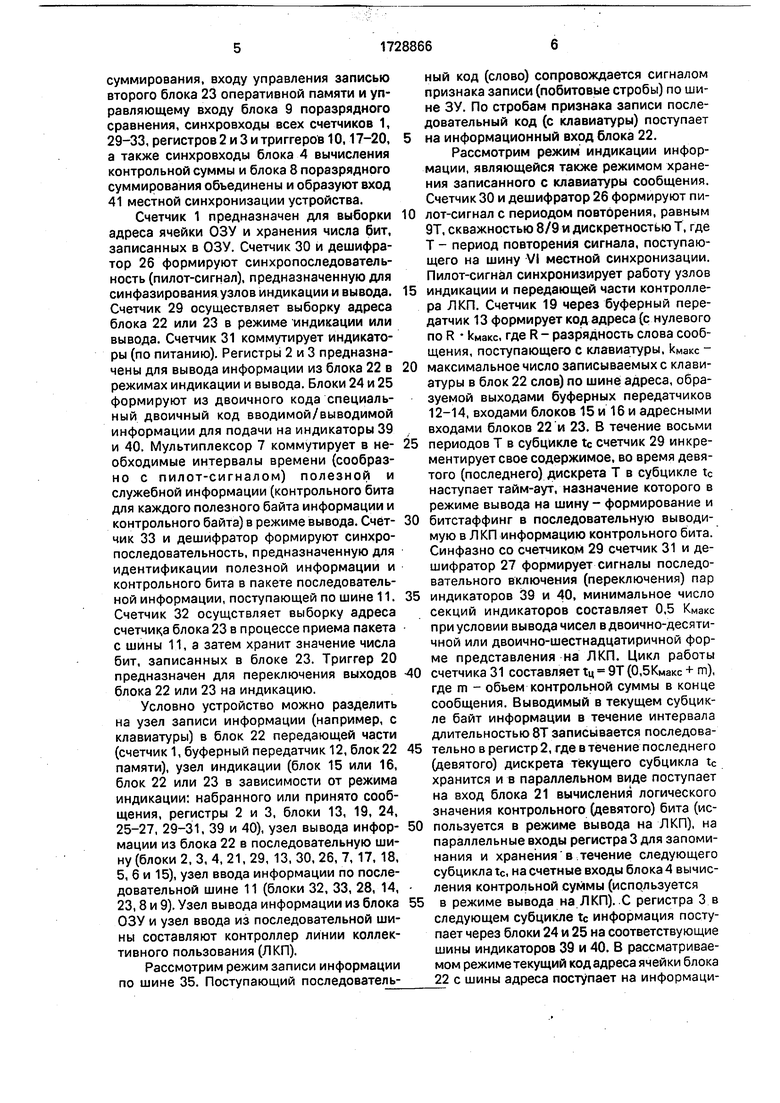

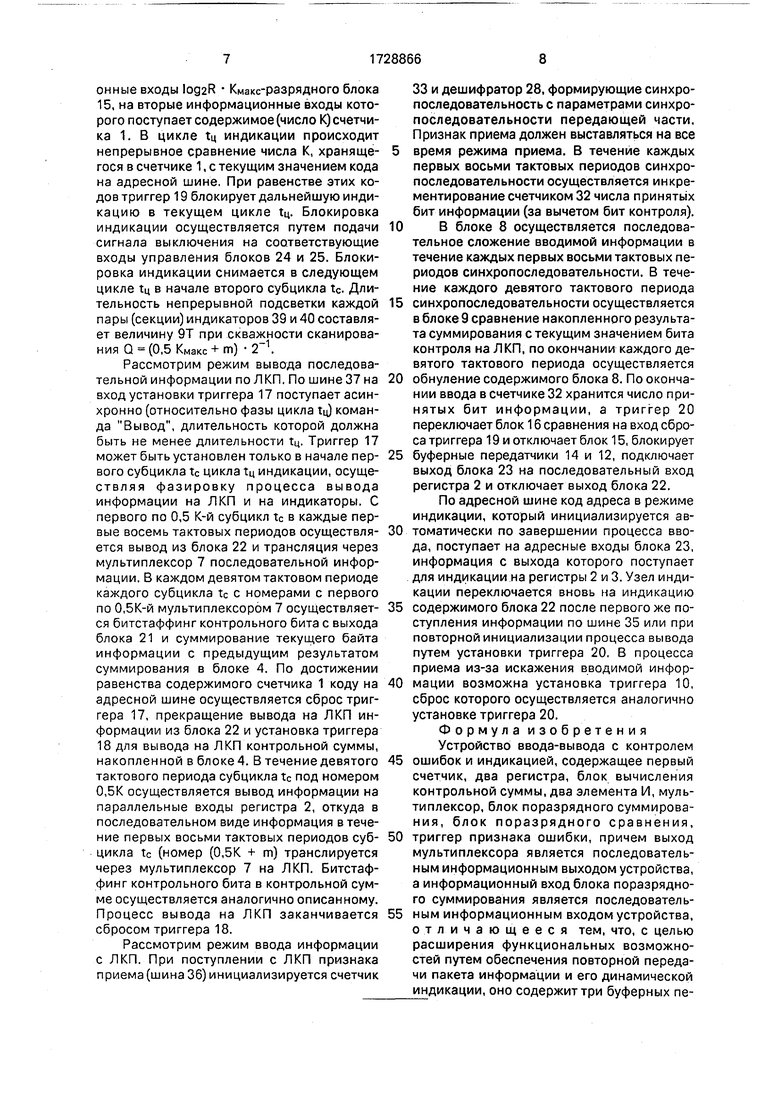

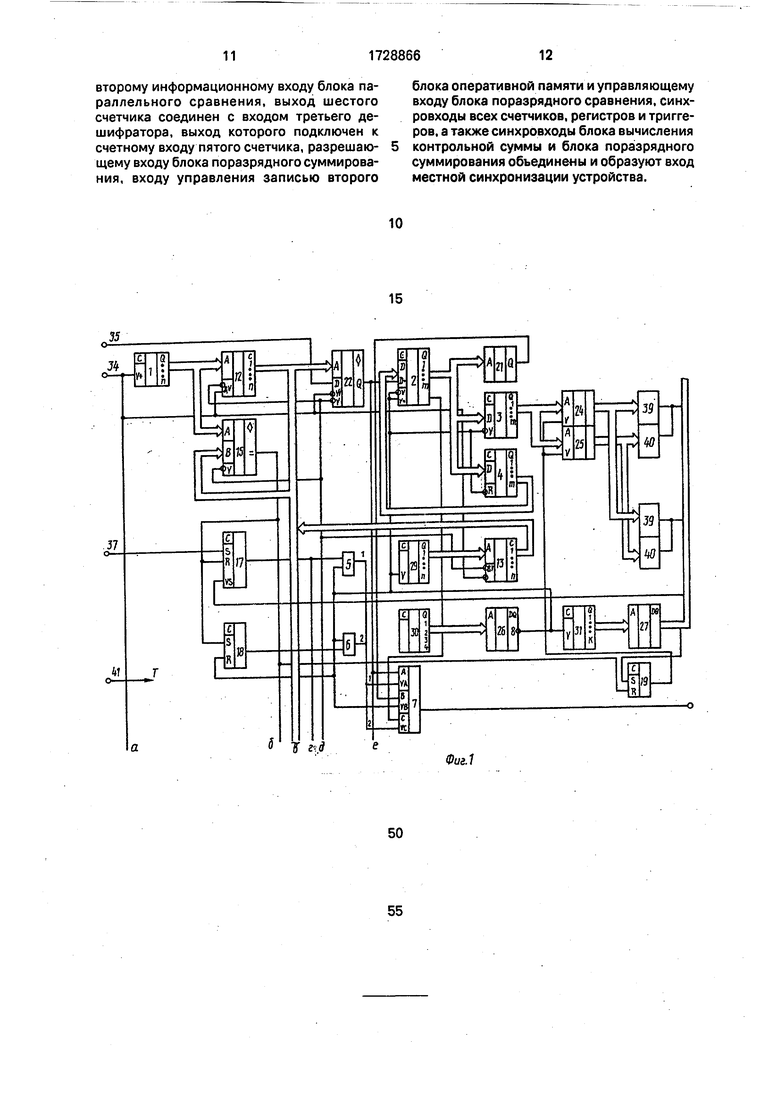

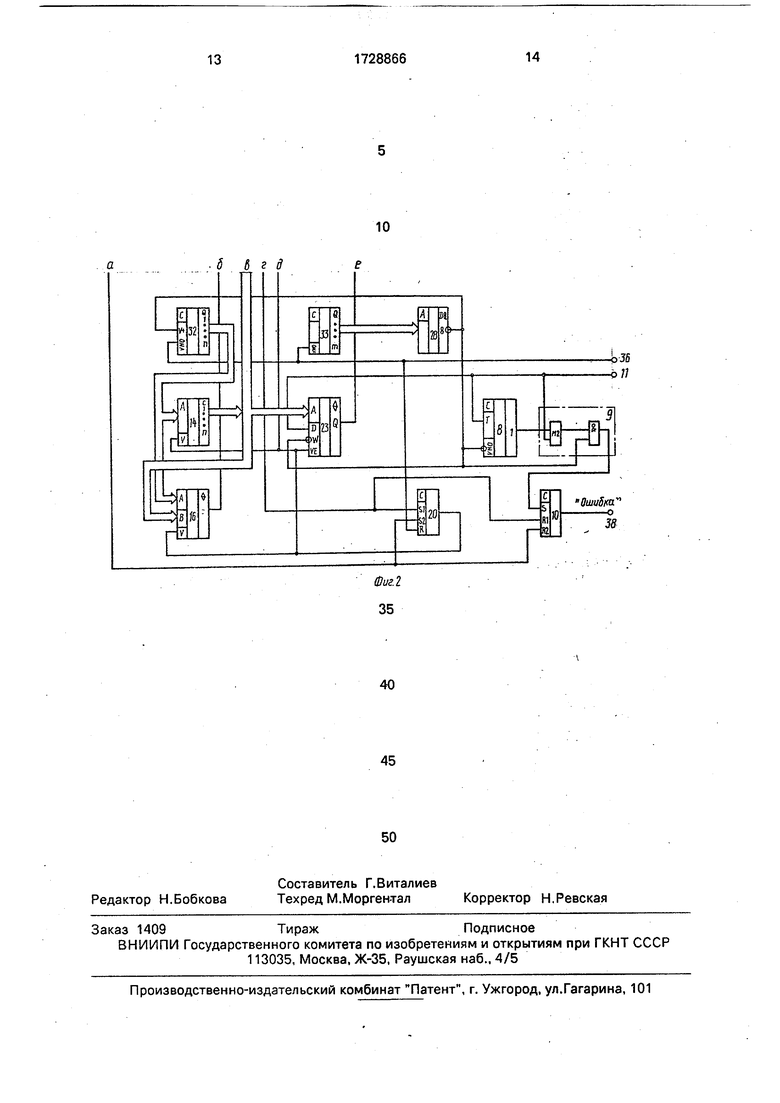

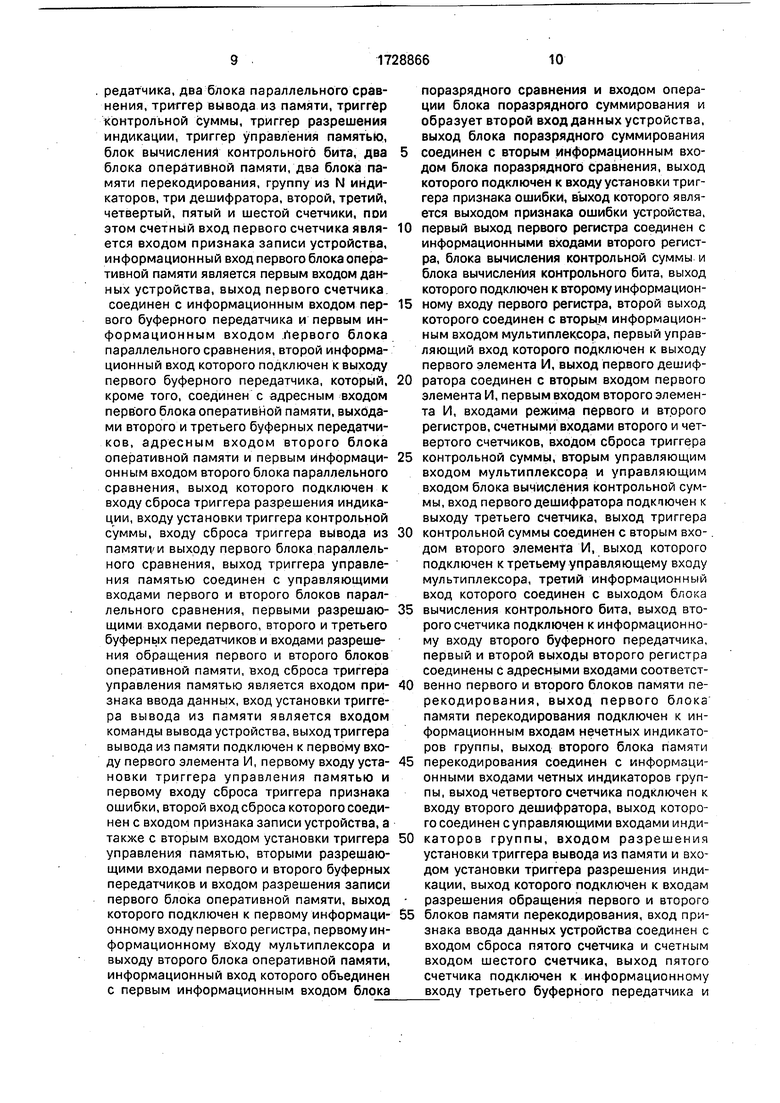

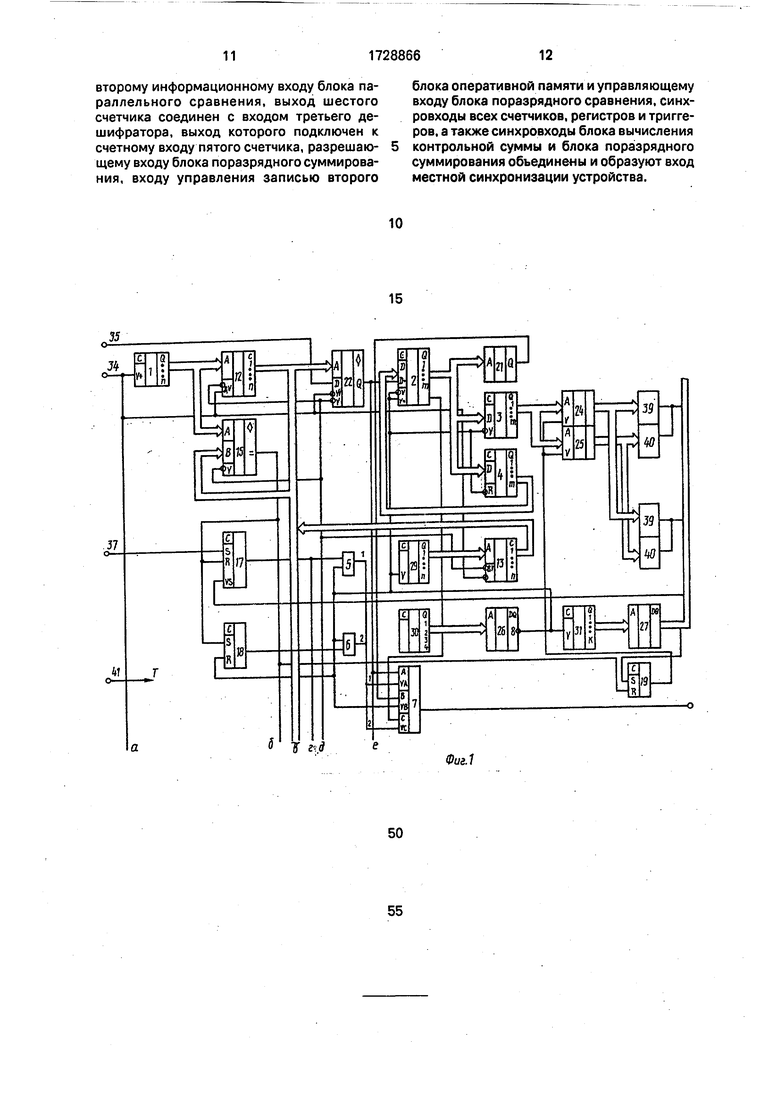

На фиг.1 и 2 изображена электрическая функциональная схема устройства ввода- вывода с контролем ошибок и индикацией.

Устройство содержит первый счётчик 1, два регистра 2 и 3, блок 4 вычисления контрольной суммы, два элемента И 5 и 6, мультиплексор 7, блок 8 поразрядного суммирования, блок 9 поразрядного сравнения, триггер 10 признака ошибки, причем выход

мультиплексора 7 является последовательным информационным выходом устройства, а информационный вход блока 8 поразрядного суммирования является последовательным информационным входом 11 устройства, три буферных передатчика 12- 14, два блока 15 и 16 параллельного сравнения, триггер 17 вывода из памяти, триггер 18 контрольной суммы, триггер 19 разрешения индикации, триггер 20 управления памятью, блок 21 вычисления контрольного бита, два блока 22 и 23 оперативной памяти, два блока 24 и 25 памяти перекодирования, три дешифратора 26-28, второй 29, третий 30, четвертый 31, пятый 32 и шестой 33 счетчики, при этом счетный вход первого счетчика 1 является входом 34 признака записи устройства, информационный вход первого

N| Ю 00 00 О ON

блока 22 оперативной памяти является первым входом 35 данных устройства, выход первого счетчика 1 соединен с информационным входом первого буферного передатчика 12 и первым информационным входом первого блока 15 параллельного сравнения, второй информационный вход которого подключен к выходу первого буферного передатчика 12, который, кроме того, соединен с адресным входом первого блока 22 оперативной памяти, выходами второго 13 и третьего 14 буферных передатчиков, адресным входом второго блока 23 оперативной памяти и первым информационным входом второго блока 16 параллельного сравнения, выход которого подключен к входу сброса триггера 19 разрешения индикации, входу установки триггера 18 контрольной суммы, входу сброса триггера 17 вывода из памяти и выходу первого блока 15 параллельного сравнения, выход триггера 20 управления памятью соединены с управляющими входами первого 15 и второго 16 блоков параллельного сравнения, первыми разрешающими входами первого 12, второго 13 и третьего 14 буферных передатчиков и входами разрешения обращения первого 22 и второго 23 блоков 22 и 23 оперативной памяти, вход сброса триггера 20 управления памятью является входом 36 признака ввода данных, вход установки триггера 17 вывода из памяти является входом 37 команды вывода устройства, выход триггера 17 вывода из памяти подключен к первому входу первого элемента И 5, первому входу установки триггера 20 управления памятью и первому входу сброса триггера 10 признака ошибки, второй вход сброса которого соединены с входом 34 признака записи устройства, а также с вторым входом установки триггера 20 управления памятью, вторыми разрешающими входами первого 12 и второго 13 буферных передатчиков и входом разрешения записи первого блока 22 оперативной памяти, выход которого подключен к первому информационному входу первого регистра 2, первому информационному входу мультиплексора 7 и выходу второго блока 23 оперативной памяти, информационный вход которого объединен с первым информационным входом блока 9 поразрядного сравнения и входом операции блока 8 поразрядного суммирования и образует второй вход 11 данных устройства, выход блока 8 поразрядного суммирования соединен с вторым информационным входом блока поразрядного сравнения, выход которого подключен к входу установки триггера 10 признака ошибки, выход которого является выходом

38 признака ошибки устройства, первый выход первого регистра 2 соединен с информационными входами второго регистра 3, блока 4 вычисления контрольной суммы и

блока 21 вычисления контрольного бита, выход которого подключен к второму информационному входу первого регистра 2, второй выход которого соединен с вторым информационным входом мультиплексора

07, первый управляющий вход которого подключен к выходу первого элемента И 5, выход первого дешифратора 26 соединен с вторым входом первого элемента И 5, первый входом второго элемента И 6, входами режи5 ма первого 2 и второго 3 регистров, счетными входами второго 29 и четвертого 31 счетчиков, входом сброса триггера 18 контрольной суммы, вторым управляющим входом мультиплексора 7 и управляющим входом блока

0 4 вычисления контрольной суммы, вход первого дешифратора 26 подключен к выходу третьего счетчика 30, выход триггера 18 контрольной суммы соединен с вторым входом второго элемента И 6, выход которого под5 ключей к третьему управляющему входу мультиплексора 7, третий информационный вход которого соединен с выходом блока 21 вычисления контрольного бита, выход второго счетчика 29 подключен к информацион0 ному входу второго буферного передатчика 13, первый и второй выходы второго регистра 3 соединены с адресными входами соответственно первого 24 и второго 25 блоков памяти перекодирования, выход первого

5 блока 24 памяти перекодирования подключен к информационным входам нечетных индикаторов 39 группы, выход второго блока 25 памяти перекодирования соединен с информационными входами четных индикаторов 40

0 группы, выход четвертого счетчика 31 подключен к входу второго дешифратора 27, выход которого соединен с управляющими входами индикаторов 39 и 40 группы, входом разрешения установки триггера 17 вывода

5 из памяти и входом установки триггера 19 разрешения индикации, выход которого подключен к входам разрешения обращения первого 24 и второго 25 блоков памяти перекодирования, вход 36 признака ввода

0 данных устройства соединен с входом сброса пятого счетчика 32 и счетным входом шестого счетчика 33, выход пятого счетчика 32 подключен к информационному входу третьего буферного передатчика 14 и второ5 му информационному входу второго блока 16 параллельного сравнения, выход шестого счетчика 33 соединен с входом третьего дешифратора 28, выход которого подключен к счетному входу пятого счетчика 32, разрешающему входу блока 8 поразрядного

суммирования, входу управления записью второго блока 23 оперативной памяти и управляющему входу блока 9 поразрядного сравнения, синхровходы всех счетчиков 1, 29-33, регистров 2 и 3 и триггеров 10,17-20, а также синхровходы блока 4 вычисления контрольной суммы и блока 8 поразрядного суммирования объединены и образуют вход 41 местной синхронизации устройства.

Счетчик 1 предназначен для выборки адреса ячейки ОЗУ и хранения числа бит, записанных в ОЗУ. Счетчик 30 и дешифратор 26 формируют синхропоследователь- ность (пилот-сигнал), предназначенную для синфазирования узлов индикации и вывода. Счетчик 29 осуществляет выборку адреса блока 22 или 23 в режиме индикации или вывода. Счетчик 31 коммутирует индикаторы (по питанию). Регистры 2 и 3 предназначены для вывода информации из блока 22 в режимах индикации и вывода. Блоки 24 и 25 формируют из двоичного кода специальный двоичный код вводимой/выводимой информации для подачи на индикаторы 39 и 40. Мультиплексор 7 коммутирует в не- обходимые интервалы времени (сообразно с пилот-сигналом) полезной и служебной информации (контрольного бита для каждого полезного байта информации и контрольного байта) в режиме вывода. Счёт- чик 33 и дешифратор формируют синхро- последовательность, предназначенную для идентификации полезной информации и контрольного бита в пакете последовательной информации, поступающей по шине 11. Счетчик 32 осущствляет выборку адреса счетчика блока 23 в процессе приема пакета с шины 1.1, а затем хранит значение числа бит, записанных в блоке 23. Триггер 20 предназначен для переключения выходов блока 22 или 23 на индикацию.

Условно устройство можно разделить на узел записи информации (например, с клавиатуры) в блок 22 передающей части (счетчик 1, буферный передатчик 12, блок 22 памяти), узел индикации (блок 15 или 16, блок 22 или 23 в зависимости от режима индикации: набранного или принято сообщения, регистры 2 и 3, блоки 13, 19, 24, 25-27, 29-31, 39 и 40), узел вывода инфор- мации из блока 22 в последовательную шину (блоки 2, 3, 4, 21, 29, 13,30,26,7, 17, 18, 5, 6 и 15), узел ввода информации по последовательной шине 11 (блоки 32, 33, 28, 14, 23,8 и 9). Узел вывода информации из блока ОЗУ и узел ввода из последовательной шины составляют контроллер линии коллективного пользования (ЛКП).

Рассмотрим режим записи информации по шине 35. Поступающий последовательный код (слово) сопровождается сигналом признака записи (побитовые стробы) по шине ЗУ. По стробам признака записи последовательный код (с клавиатуры) поступает на информационный вход блока 22.

Рассмотрим режим индикации информации, являющейся также режимом хранения записанного с клавиатуры сообщения. Счетчик 30 и дешифратор 26 формируют пилот-сигнал с периодом повторения, равным 9Т, скважностью 8/9 и дискретностью Т, где Т - период повторения сигнала, поступающего на шину VI местной синхронизации. Пилот-сигнал синхронизирует работу узлов индикации и передающей части контроллера ЛКП. Счетчик 19 через буферный передатчик 13 формирует код адреса (с нулевого по R Кмакс, где R - разрядность слова сообщения, поступающего с клавиатуры. кмакс - максимальное число записываемых с клавиатуры в блок 22 слов) по шине адреса, образуемой выходами буферных передатчиков 12-14, входами блоков 15 и 16 и адресными входами блоков 22 и 23. В течение восьми периодов Т в субцИкле tc счетчик 29 инкре- ментирует свое содержимое, во время девятого (последнего) дискрета Т в субцикле tc наступает тайм-аут, назначение которого в режиме вывода на шину - формирование и битстаффинг в последовательную выводимую в ЛКП информацию контрольного бита. Синфазно со счетчиком 29 счетчик 31 и дешифратор 27 формирует сигналы последовательного включения (переключения) пар индикаторов 39 и 40, минимальное число секций индикаторов составляет 0,5 Кмакс при условии вывода чисел в двоично-десятичной или двоично-шестнадцатиричной форме представления на ЛКП. Цикл работы счетчика 31 составляет Тц 9Т (0,5КМакс + гл), где т - объем контрольной суммы в конце сообщения. Выводимый в текущем субцикле байт информации в течение интервала длительностью 8Т записывается последовательно в регистр 2, где в течение последнего (девятого) дискрета текущего субцикла tc хранится и в параллельном виде поступает на вход блока 21 вычисления логического значения контрольного (девятого) бита (используется в режиме вывода на ЛКП), на параллельные входы регистра 3 для запоминания и хранения в течение следующего субцикла tc, на счетные входы блока 4 вычисления контрольной суммы (используется в режиме вывода на ЛКП). С регистра 3 в следующем субцикле tc информация поступает через блоки 24 и 25 на соответствующие шины индикаторов 39 и 40. В рассматриваемом режиме текущий код адреса ячейки блока 22 с шины адреса поступает на информационные входы logaR Кмакс-разрядного блока 15, на вторые информационные входы которого поступает содержимое (число К) счетчика 1. В цикле т.ц индикации происходит непрерывное сравнение числа К, храняще- гося в счетчике 1, с текущим значением кода на адресной шине, При равенстве этих кодов триггер 19 блокирует дальнейшую инди- кацию в текущем цикле 1ц. Блокировка индикации осуществляется путем подачи сигнала выключения на соответствующие входы управления блоков 24 и 25. Блокировка индикации снимается в следующем цикле 1ц в начале второго субцикла tc. Длительность непрерывной подсветки каждой пары (секции) индикаторов 33 и 40 составляет величину 9Т при скважности сканирования Q (0,5 Кмакс + т) 2

Рассмотрим режим вывода последовательной информации по Л КП. По шине 37 на вход установки триггера 17 поступает асинхронно (относительно фазы цикла т.ц) команда Вывод, длительность которой должна быть не менее длительности т.ц. Триггер 17 может быть установлен только в начале пер- вого субцикла tc цикла tu индикации, осуще- ствляя фазировку процесса вывода информации на ЛКП и на индикаторы. С первого по 0,5 К-й субцикл tc в каждые первые восемь тактовых периодов осуществля- ется вывод из блока 22 и трансляция через мультиплексор 7 последовательной информации. В каждом девятом тактовом периоде каждого субцикла tc с номерами с первого по 0,5К-й мультиплексором 7 осуществляет- ся битстаффинг контрольного бита с выхода блока 21 и суммирование текущего байта информации с предыдущим результатом суммирования в блоке 4. По достижении равенства содержимого счетчика 1 коду на адресной шине осуществляется сброс триггера 17, прекращение вывода на ЛКП информации из блока 22 и установка триггера 18 для вывода на ЛКП контрольной суммы, накопленной в блоке 4. В течение девятого тактового периода субцикла tc под номером 0,5К осуществляется вывод информации на параллельные входы регистра 2, откуда в последовательном виде информация в течение первых восьми тактовых периодов суб- цикла tc (номер (0,5К + т) транслируется через мультиплексор 7 на ЛКП. Битстаффинг контрольного бита в контрольной сумме осуществляется аналогично описанному. Процесс вывода на ЛКП заканчивается сбросом триггера 18.

Рассмотрим режим ввода информации с ЛКП. При поступлении с ЛКП признака приема (шина 36) инициализируется счетчик

33 и дешифратор 28, формирующие синхро- последовательность с параметрами синхро- последовательности передающей части. Признак приема должен выставляться на все время режима приема. В течение каждых первых восьми тактовых периодов синхро- последовательности осуществляется инкре- ментирование счетчиком 32 числа принятых бит информации (за вычетом бит контроля).

В блоке 8 осуществляется последовательное сложение вводимой информации в течение каждых первых восьми тактовых периодов синхропоследовательности, В течение каждого девятого тактового периода синхропоследовательности осуществляется в блоке 9 сравнение накопленного результата суммирования с текущим значением бита контроля на ЛКП, по окончании каждого девятого тактового периода осуществляется обнуление содержимого блока 8. По окончании ввода в счетчике 32 хранится число принятых бит информации, а триггер 20 переключает блок 16 сравнения на вход сброса триггера 19 и отключает блок 15, блокирует буферные передатчики 14 и 12, подключает выход блока 23 на последовательный вход регистра 2 и отключает выход блока 22.

По адресной шине код адреса в режиме индикации, который инициализируется автоматически по завершении процесса ввода, поступает на адресные входы блока 23, информация с выхода которого поступает для индикации на регистры 2 и 3. Узел индикации переключается вновь на индикацию содержимого блока 22 после первого же поступления информации по шине 35 или при повторной инициализации процесса вывода путем установки триггера 20. В процесса приема из-за искажения вводимой информации возможна установка триггера 10, сброс которого осуществляется аналогично установке триггера 20.

Формула изобретения

Устройство ввода-вывода с контролем ошибок и индикацией, содержащее первый счетчик, два регистра, блок вычисления контрольной суммы, два элемента И, мультиплексор, блок поразрядного суммирования, блок поразрядного сравнения, триггер признака ошибки, причем выход мультиплексора является последовательным информационным выходом устройства, а информационный вход блока поразрядного суммирования является последовательным информационным входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения повторной передачи пакета информации и его динамической индикации, оно содержит три буферных передатчика, два блока параллельного сравнения, триггер вывода из памяти, триггер контрольной суммы, триггер разрешения индикации, триггер управления памятью, блок вычислений контрольного бита, два блока оперативной памяти, два блока памяти перекодирования, группу из N индикаторов, три дешифратора, второй, третий, четвертый, пятый и шестой счетчики, пои этом счетный вход первого счетчика является входом признака записи устройства, информационный вход первого блока оперативной памяти является первым входом данных устройства, выход первого счетчика. соединен с информационным входом первого буферного передатчика и первым ин- формационным входом .первого блока параллельного сравнения, второй информационный вход которого подключен к выходу первого буферного передатчика, который, кроме того, соединен с адресным входом первого блока оперативной памяти, выходами второго и третьего буферных передатчиков, адресным входом второго блока оперативной памяти и первым информационным входом второго блока параллельного сравнения, выход которого подключен к входу сброса триггера разрешения индикации, входу установки триггера контрольной суммы, входу сброса триггера вывода из памяти,/и выходу первого блока параллельного сравнения, выход триггера управления памятью соединен с управляющими входами первого и второго блоков параллельного сравнения, первыми разрешающими входами первого, второго и третьего буферных передатчиков и входами разрешения обращения первого и второго блоков оперативной памяти, вход сброса триггера управления памятью является входом признака ввода данных, вход установки триггера вывода из памяти является входом команды вывода устройства, выход триггера вывода из памяти подключен к первому входу первого элемента И, первому входу установки триггера управления памятью и первому входу сброса триггера признака ошибки, второй вход сброса которого соединен с входом признака записи устройства, а также с вторым входом установки триггера управления памятью, вторыми разрешающими входами первого и второго буферных передатчиков и входом разрешения записи первого блока оперативной памяти, выход которого подключен к первому информационному входу первого регистра, первому информационному входу мультиплексора и выходу второго блока оперативной памяти, информационный вход которого объединен с первым информационным входом блока

поразрядного сравнения и входом операции блока поразрядного суммирования и образует второй вход данных устройства, выход блока поразрядного суммирования

соединен с вторым информационным входом блока поразрядного сравнения, выход которого подключен к входу установки триггера признака ошибки, выход которого является выходом признака ошибки устройства,

0 первый выход первого регистра соединен с информационными входами второго регистра, блока вычисления контрольной суммы и блока вычисления контрольного бита, выход которого подключен к второму информацион5 ному входу первого регистра, второй выход которого соединен с вторым информационным входом мультиплексора, первый управляющий вход которого подключен к выходу первого элемента И, выход первого дешиф0 ратора соединен с вторым входом первого элемента И, первым входом второго элемента И, входами режима первого и второго регистров, счетными входами второго и четвертого счетчиков, входом сброса триггера

5 контрольной суммы, вторым управляющим входом мультиплексора и управляющим входом блока вычисления контрольной суммы, вход первого дешифратора подключен к выходу третьего счетчика, выход триггера

0 контрольной суммы соединен с вторым вхо-. дом второго элемента И, выход которого подключен к третьему управляющему входу мультиплексора, третий информационный вход которого соединен с выходом блока

5 вычисления контрольного бита, выход второго счетчика подключен к информационному входу второго буферного передатчика, первый и второй выходы второго регистра соединены с адресными входами соответст0 венно первого и второго блоков памяти перекодирования, выход первого блока памяти перекодирования подключен к информационным входам нечетных индикаторов группы, выход второго блока памяти

5 перекодирования соединен с информационными входами четных индикаторов группы, выход четвертого счетчика подключен к входу второго дешифратора, выход которого соединен с управляющими входами инди0 катеров группы, входом разрешения установки триггера вывода из памяти и входом установки триггера разрешения индикации, выход которого подключен к входам разрешения обращения первого и второго

5 блоков памяти перекодирования, вход признака ввода данных устройства соединен с входом сброса пятого счетчика и счетным входом шестого счетчика, выход пятого счетчика подключен к информационному входу третьего буферного передатчика и

пТя°лРлГлУ пФ°РмпационномУ BX°W бл°к па- блока оперативной памяти и управляющему раллельного соавнения. ВМУПП тег-™™ г,л„,,к

раллельного сравнения, выход шестого счетчика соединен с входом третьего деM IRJ4Cn К.f, м wivsixt wrinAUUDAU/lEal UIIUKd ВЫЧИСЛРЫМО

емГвхол1Х ;яЯТ°ГОСЧеТЧИКа РаЗРеШаЮ-5 КОНТР°ЛЬНОЙ суммы и блока поразрядного

щему входу блока поразрядного суммирова-суммирования объединены и образуют вход

ния, входу управления записью второгоместной синхронизации устройства.

входу блока поразрядного сравнения, синх- ровходы всех счетчиков, регистров и триггеров, а также синхровходы блока вычисления

блока оперативной памяти и управляющему г,л„,,к

f, м wivsixt wrinAUUDAU/lEal UIIUKd ВЫЧИСЛРЫМО

КОНТР°ЛЬНОЙ суммы и блока поразрядного

входу блока поразрядного сравнения, синх- ровходы всех счетчиков, регистров и триггеров, а также синхровходы блока вычисления

S в г д

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

| Устройство передачи информации по волоконно-оптической линии связи | 1988 |

|

SU1675919A1 |

| Устройство для сопряжения между абонентами | 1987 |

|

SU1411759A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для контроля информации | 1986 |

|

SU1399774A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

| ИМПУЛЬСНЫЙ КОДОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2248607C1 |

| УСТРОЙСТВО ДЛЯ УЧЕТА НОМЕРОВ ТРАНСПОРТНЫХ ОБЪЕКТОВ | 1991 |

|

RU2068583C1 |

Изобретение относится к области вычислительной техники и может быть использовано в аппаратуре передачи, приема и обработки информации. Целью изобретения является расширение функциональных возможностей за счет обеспечения повторной передачи пакета информации него динамической индикации. С этой целью в устройство, содержащее первый счетчик, два регистра, блок вычисления контрольной суммы, два элемента И, мультиплексор, блок поразрядного суммирования, блок поразрядного сравнения, триггер признака ошибки, введены три буферных передатчика, два блока параллельного сравнения, триггер вывода из памяти, триггер контрольной суммы, триггер разрешения индикации, триггер управления памятью, блок вычисления контрольного бита, два блока оперативной памяти, два блока памяти перекодирования, группу из N индикаторов, три дешифратора, второй, третий, четвертый, пятый и шестой счетчики. 2 ил.

Фиг. 2 35

| Устройство для приема и выдачи информации с контролем ошибок | 1976 |

|

SU611244A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для приемопередачи информации с контролем ошибок | 1985 |

|

SU1277166A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1992-04-23—Публикация

1989-04-24—Подача