Предлагаемое устройство относится к области цифровой обработки сигналов, в частности к амплитудным ограничителям для частотно- и фазомодулированных сигналов.

Амплитудные ограничители широко применяются для обработки простых и особенно сложных сигналов в приемных устройствах радиотехнических систем [1-3]. Использование ограничителей позволяет, например, произвести нормировку динамического диапазона принимаемых сигналов и защиту от импульсных помех [4].

Известны амплитудные ограничители [6], работающие на высокой или промежуточной частоте и обеспечивающие минимальные, примерно 1 дБ, потери в отношении сигнал/шум при жестком ограничении слабых сигналов с большой базой [2]. Достоинством радиочастотных ограничителей является то, что в них осуществляется ограничение модуля сигнала, а фаза передается на выход без искажений.

Однако такие ограничители не могут быть использованы при цифровой обработке сигналов, получающей все большее распространение.

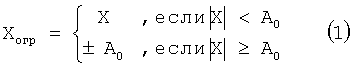

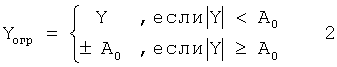

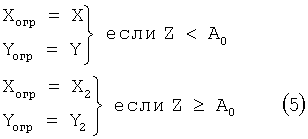

Известна схема ограничителя, применяемого в цифровых устройствах обработки сигналов [7]. Он является наиболее близким по технической сущности к заявляемому устройству и принят за прототип. В состав ограничителя, принятого за прототип, входят датчик кода (уровня), схема сравнения кодов и коммутатор. Сущность его работы заключается в следующем. Синусная (X) и косинусная (Y) составляющие сигнала в цифровой форме, например г в двоичном коде, по входной шине поступают параллельно или последовательно на вход схемы сравнения. На второй входе схемы сравнения поступает постоянный по уровню сигнал с датчика кода. В схеме сравнения значения квадратурных (синусной и косинусной) составляющих сигнала сравнивается с уровнем А0 сигнала датчика кода. На выходе схемы сравнения вырабатывается логический сигнал управления, равный единице, если выполняется условие X(Y)≥A0, и логическому нулю, если X(Y)<A0. На выходной шине коммутатора, один вход которого подключен ко входной шине ограничителя, а другой - к выходу датчика кода, квадратурные составляющие сигнала принимают значения

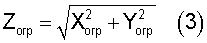

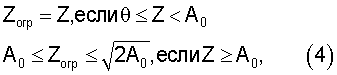

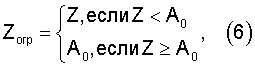

Знак при ограничении сохраняется, модуль Zогр сигнала на выходе ограничителя

принимает в соответствии с (1, 2) следующие значения:

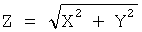

где  - модуль сигнала на входе ограничителя.

- модуль сигнала на входе ограничителя.

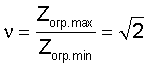

Как следует из неравенства (4), амплитудная характеристика ограничителя на нелинейном участке, где Z>A0, может иметь неравномерность до величины  или до 40%.

или до 40%.

Такая высокая неравномерность амплитудной характеристики прототипа является его недостатком.

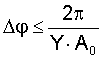

Кроме того, из (1, 2) следует также, фаза ограниченного сигнала  может принимать только 8А0 дискретных значений, где A0 выражено числом уравнений квантования входного процесса, а наибольшая ошибка квантования фазы, вносимая таким ограничителем при условии

может принимать только 8А0 дискретных значений, где A0 выражено числом уравнений квантования входного процесса, а наибольшая ошибка квантования фазы, вносимая таким ограничителем при условии  то есть при сильных сигналах, может составить величину

то есть при сильных сигналах, может составить величину

При жестком ограничении (A0=1) фаза сигнала на выходе может принимать значения, кратные  Такие ошибки квантования фазы существенно снижают эффективность последующей когерентной обработки даже сильных сигналов, а при жестком ограничении слабых сигналов приводят к увеличению потерь в отношении сигнал/шум до 2 дБ.

Такие ошибки квантования фазы существенно снижают эффективность последующей когерентной обработки даже сильных сигналов, а при жестком ограничении слабых сигналов приводят к увеличению потерь в отношении сигнал/шум до 2 дБ.

Уменьшение ошибок квантования фазы в ограничителе, принятом за прототип, возможно лишь за счет увеличения линейного участка (числа уровней A0) в амплитудной характеристике ограничителя. Однако увеличение участка частот неприемлемо, например, из-за ухудшения качества нормировки динамического диапазона сигналов или защищенности от импульсных помех.

Таким образом, первая цель заявляемого изобретения состоит в увеличении равномерности амплитудной характеристики.

Второй целью является уменьшение ошибок квантования фазы без увеличения линейного участка амплитудной характеристики.

Первая из поставленных целей достигается тем, что в состав ограничителя, содержащего датчик кода (уровня), соединенного с одним входом схемы сравнения кодов, выход которой подключен к управляющему входу коммутатора, один сигнальный вход которой соединен со входом ограничителя, а выход является выходом ограничителя, дополнительно введены блок вычисления модуля, делитель и перемножитель, прячем вход блока вычисления модуля и один вход делителя подключены ко входу всего ограничителя, выход блока вычисления модуля соединен со вторыми входами схемы сравнения и делителя, выход делителя подключен ко входу перемножителя, второй вход которого подключен к выходу датчика кода, а выход перемножителя - ко второму входу коммутатора.

Для достижения второй цели на выходе заявленного устройства введен второй перемножитель и соединенный с его вторым входом второй датчик кода, причем первый вход перемножителя является входом ограничителя, а выход соединен со входом блока вычисления модуля и первыми входами делителя и коммутатора.

Изложенная сущность поясняется описанием работы заявлялемого устройства и приведенными ниже чертежами.

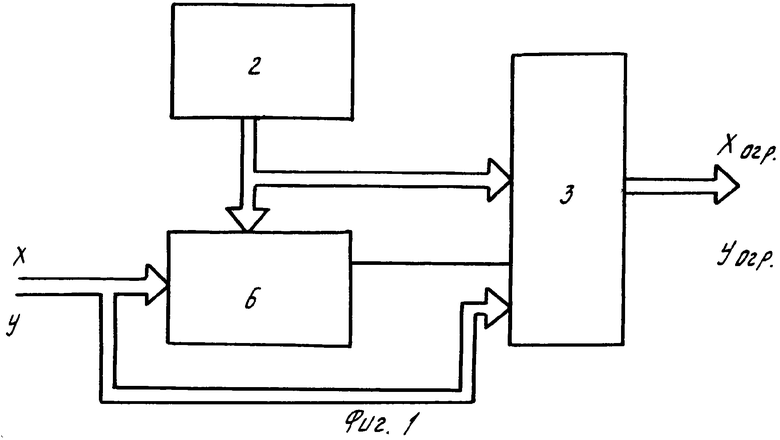

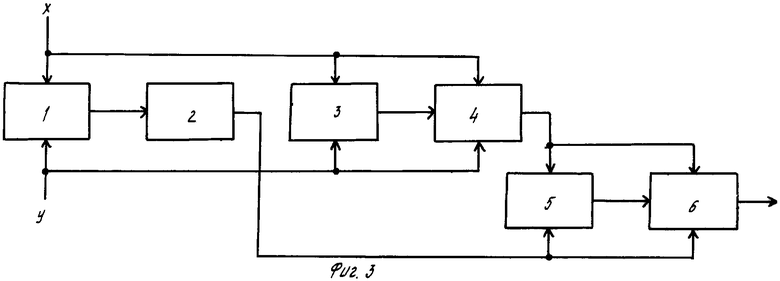

На фиг.2 показана функциональная схема заявленного ограничителя. На фиг.1 - функциональная схема прототипа. На чертежах и в тексте введены следующие обозначения:

1 - первый перемножитель;

2 - датчик кода;

3 - коммутатор;

4 - делитель;

5 - блок вычисления модуля;

6 - схема сравнения;

7 - второй перемножитель;

8 - дополнительный датчик кода;

X, Y - квадратурные (синусная и косинусная) составляющие сигнала на входе ограничителя;

Xогр, Yогр - квадратурные составляющие сигнала на выходе ограничителя;

А0 - уровень ограничения;

А1 - коэффициент, определяющий величину линейного участка амплитудной характеристики ограничителя.

Заявленный амплитудный ограничитель состоит из первого перемножителя 1, один из входов которого является сигнальным входом, второй его вход соединен с выходом основного датчика кодов 2, а выход - с первым входом коммутатора 3; делителя 4, выход которого соединен с входом перемножителя 1, а первый вход соединен со вторым входом коммутатора 3 и входом вычислителя модуля 5, выход вычислителя модуля 5 одновременно подключен ко второму входу делителя 4 и входу схемы сравнения кодов 6, второй вход которой соединен с выходом основного датчика кодов 2, а выход ее соединен с управляющим входом коммутатора 3. Вход вычислителя модуля 5 соединен с выходом второго перемножителя 7, второй вход которого соединен с выходом дополнительного датчика 8. Первый вход перемножителя 7 является сигнальным входом ограничителя. Выход коммутатора 3 является выходом ограничителя.

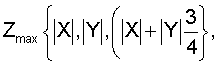

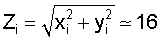

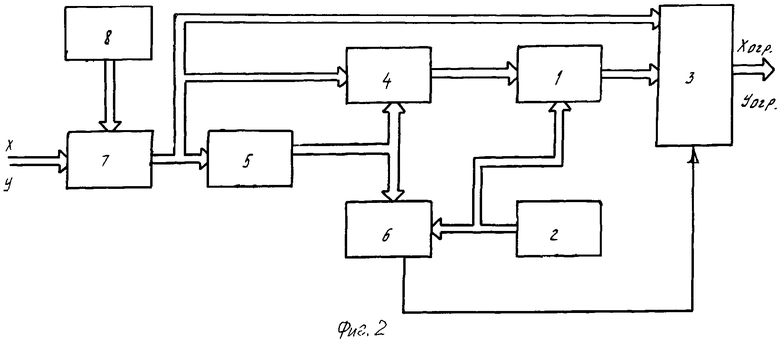

Рассмотрим вначале работу схемы, когда элементы 7 и 8 отсутствуют. Квадратурные, синусная X и косинусная Y, составляющие входного процесса по входной шине поступают параллельно или последовательно на блок 5 вычисления модуля комплексной огибающей Z. Вычисление величины Z может быть выполнено различными методами. Наиболее простым в техническом воплощении является алгоритм [7].

который может быть реализован в виде цифровой схемы (фиг.3), содержащий сумматор 1 (на ИМС 133ИМ3 или 533ИМ6), умножитель 2 на коэффициент  (на ИМС 133ИМ3 или 533ИМ6), две схемы сравнения 3,5 (на ИМС 533СП1 или 530СП1) и два коммутатора 4,6 (ИМС 533КП11, 530КП11 или 533КП13).

(на ИМС 133ИМ3 или 533ИМ6), две схемы сравнения 3,5 (на ИМС 533СП1 или 530СП1) и два коммутатора 4,6 (ИМС 533КП11, 530КП11 или 533КП13).

В делителе 4 осуществляется нормировка входного сигнала по правилу

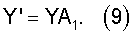

Нетрудно показать, что в результате нормировки значения Z, модуля сигнала на выходе делителя 4, Z=1. После умножения квадратурных составляющих X1 и Y1, на величину А0, формируемую датчиком кода 2, в перемножителе 1 получаем на его выходе

а модульное значение Z2 комплексной огибающей

а модульное значение Z2 комплексной огибающей

Для реализации делителя 4 и перемножителя 1 могут быть применены, например, известные [8] схемы, реализованные на логических и арифметических микросхемах указанных выше серий, а также микропроцессоры серий 1802, 1804 или 1813. Значения X2 и У2 поступают на один из входов коммутатора 3, для реализация которого можно использовать, например, мультиплексоры 533КП13 или 533КП16. Другой вход коммутатора соединен с входной шиной всего ограничителя, поэтому на него поступают значения X и Y квадратурных составляющих входного сигнала.

В схеме сравнения 6 вычисленное значение Z модуля комплексной огибающей входного сигнала сравнивается с уровнем ограничения А0, поступающим с выхода датчика кода 2. Результатом сравнения является управляющий сигнал для коммутатора 3, равный, например, логической единице, если Z≥A0, и логическому нулю, если Z<A0.

Для реализации схемы сравнения могут бить использованы, например, логические микросхемы 533СП1.

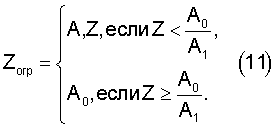

На выходную шину коммутатора 3, в зависимости от уровня управляющего сигнала, проходят либо информация со входа ограничителя, либо с выхода перемножителя 1. А именно

На основании формул (5) можно записать, что модульное значение комплексной огибающей на выходе ограничителя

откуда следует, что амплитудная характеристика заявляемого ограничителя на нелинейном участке Z>А0 равномерна, то есть Zогр=const, чем достигается первая из поставленных целей заявляемого устройства.

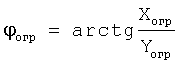

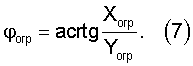

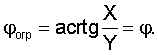

Фаза комплексной огибающей ограниченного сигнала

Подставив в (7) (5), получаем, что

Следовательно, в принципе заявляемый ограничитель не вносит дополнительной ошибки в фазу сигналов.

Однако практически фазовые ошибки существуют. Причина их состоит в уменьшении разрядности на выходе ограничителя по сравнению с разрядностью на его входе. Причем величина ошибки  увеличивается при уменьшении линейного участка A0 амплитудной характеристики.

увеличивается при уменьшении линейного участка A0 амплитудной характеристики.

Для устранения данного недостатка в заявляемый ограничитель введены второй перемножитель 7 и второй датчик кода 6. Рассмотрим работу ограничителя, включающего эти элементы.

Значения квадратурных составляющих X и Y входного сигнала умножаются в перемножителе 7 на коэффициент А1, задаваемый вторым датчиком кода 8. В результате получается

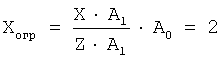

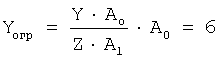

Использовав теперь зависимости (5), получаем, что на выходной шине коммутатора 3

Для модуля комплексной огибающей получаем в этом случае

Из этого выражения следует, что уровень ограниченного сигнала А0, то есть разрядность, остается постоянной при изменении величины А1. Величина линейного участка амплитудной характеристики при этом сокращается в А1 раз. При условии А1=А0 ограничитель становится жестким, а при А1=1 для него полностью справедливо описание работы без элементов 7 и 8 схемы фиг.2. Для фазы комплексной огибающей и при условии А1>1 справедливо равенство (8).

Таким образом, за счет умножения квадратурных составляющих входного сигнала на коэффициент A1 удается уменьшить величину линейного участка амплитудной характеристики заявляемого ограничителя и даже сделать его жестким, не меняя при этом разрядность A0 на выходе, то есть не изменяя величину ошибки квантования фазы, чем достигается вторая из поставленных целей заявляемого ограничителя.

Введение элементов 7 и 8 на вход ограничителя, принятого за прототип, приводит лишь к сокращению линейного участка, но именно вследствие этого увеличивает ошибку квантования фазы.

Рассмотрим численный пример, иллюстрирующий преимущества заявляемого ограничителя.

Пусть задан сигнал, квадратурные составляющие комплексной огибающей которого в некоторый момент времени ti принимают значения

Xi=4; Yi=15.

Тогда модуль комплексной огибающей

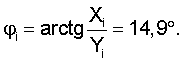

с учетом округления до целого, а фаза

с учетом округления до целого, а фаза

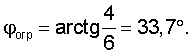

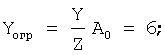

Установим уровень ограничения А0=6. В этом случае на выходе ограничителя, принятого за прототип, согласно (4) получаем Xiогр=4; Yiогр=6; Ziогр=7; то есть

Фазовая ошибка, вносимая ограничителем

,

,

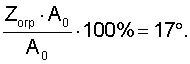

а отклонение амплитуды

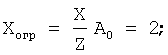

В заявляемом ограничителе согласно (5)

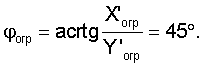

Zогр=6;

ϕогр=18,4°; Δϕогр=3,5°.

То есть амплитуда сигнала на выходе равна уровню ограничения, а фазовая ошибка в 5 раз меньше, чем в прототипе.

Допустим теперь, что A1=3, тогда из формулы (10) получаем, что ограничиваться будут все сигналы, амплитуда которых превышает значение

На выходе заявленного ограничителя при этом ничего не изменяется

Zогр=6; ϕогр=18,4°,

т.е. уменьшение линейного участка не привело к дополнительным фазовым ошибкам.

Нетрудно показать, что если в устройстве, выбранном за прототип, умножить предварительно значения квадратурных составляющих сигнала на коэффициент A1, то величина линейного участка также сократится. Однако величина разовой ошибки при этом возрастает. Действительно в рассматриваемом примере

X1=A1X=12>A0, след. X'огр=A0

Y'=A1Y=45>A0, след. Y'огр=A0,

поэтому

Следовательно, ошибка квантования фазы при уменьшении линейного участка в прототипе возросла до величины Δϕ=30,1°, то есть стала почти в 9 раз больше, чем в заявленном ограничителе.

Таким образом, в заявленном ограничителе при помощи соответствующего выбора коэффициентов A0 и A1 можно получить необходимую равномерность амплитудной характеристики ограничителя и минимальные ошибки квантования фазы, а следовательно, и минимальные потери в отношении сигнал/шум.

Источники информации

1. Гоноровский И.С. Радиотехнические цели и сигналы. - М.: Советское радио, 1971.

2. Черняк Ю.Б. Чувствительность, точность и разрешающая способность многоканального приемника с широкополосным ограничителем. - Радиотехника и электроника, 1962, том 12, №8.

3. Зачепицкий А.А., Лейких М.А., Марескин В.М. К вопросу приема сложных сигналов радиолокационным приемником, содержащем ограничитель. - Радиотехника и электроника, 1974, №9.

4. Зачепицкий А.А., Пахомов Ю.И. К вопросу защищенности радиолокационного приемника с ограничением от импульсных помех. - Изв. ВУЗов "Радиоэлектроника", 1969, т.12, №2.

5. Авторское свидетельство №843167.

6. Авторское свидетельство №881979.

7. Поиск, обнаружение и измерение параметров сигналов в радионавигационных системах, стр.125. Под редакцией Ю.М.Казаринова.

8. Каган Б.М., Каневский М.М. Цифровые вычислительные машины и системы, стр.349.

| название | год | авторы | номер документа |

|---|---|---|---|

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2582331C1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2566813C1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| СПОСОБ ОПРЕДЕЛЕНИЯ КОЭФФИЦИЕНТА КОМАНДЫ ОДНОКАНАЛЬНЫХ ВРАЩАЮЩИХСЯ РАКЕТ И СНАРЯДОВ С РЕЛЕЙНЫМ РУЛЕВЫМ ПРИВОДОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2574500C2 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2567002C1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ИЗМЕНЯЮЩЕЙСЯ ЧАСТОТЫ | 2021 |

|

RU2765264C1 |

| ДВУХКАНАЛЬНЫЙ АУДИОМЕТР | 2024 |

|

RU2835841C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ НЕСТАБИЛЬНОСТИ НЕСУЩЕЙ ЧАСТОТЫ ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2006 |

|

RU2336650C2 |

| СПОСОБ РЕГИСТРАЦИИ АРТЕРИАЛЬНОГО ДАВЛЕНИЯ И ЧАСТОТЫ ДЫХАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2006 |

|

RU2345704C2 |

Изобретение относится к области цифровой обработки сигналов. Технический результат заключается в увеличении равномерности амплитудной характеристики и уменьшении ошибок квантования фазы без увеличения линейного участка амплитудной характеристики. Для этого устройство содержит первый и второй датчики кода, блок сравнения, коммутатор, первый и второй перемножители. 1 з.п. ф-лы, 3 ил.

Авторы

Даты

2006-07-20—Публикация

1985-01-16—Подача