Известны параллельные комбинационные двоичные сумматоры с параллельным переносом. Основу их составляют одноразрядные полусумматоры на два входа (число сумматоров определяется разрядностью слагаемых). В состав таких сумматоров входят элементы конъюнкции, дизъюнкции и инверторы.

Предложенный сумматор выполнен на элементах «ЗАПРЕТ и дизъюнкции, реализованных на оптоэлектронных приборах, и отличается от известных тем, что в нем выходы триггера каждого разряда одного регистра соединены с запретными входами двух элементов «ЗАПРЕТ, а противоположные выходы триггера каждого разряда другого регистра - с соответствующими «мечеными входами этих же элементов, образующих совместно со схемой «ИЛИ, ко входам которой подключены выходы упомянутых элементов, схему «равнозначности, имеющую два выхода, один из которых является выходом схемы «ИЛИ, а другой выходом элемента «ЗАПРЕТ, «меченый вход которого соединен с прямым выходом триггера одного из регистров. Это позволяет повысить быстродействие сумматора и упростить устройство, уменьшить количество его оборудования.

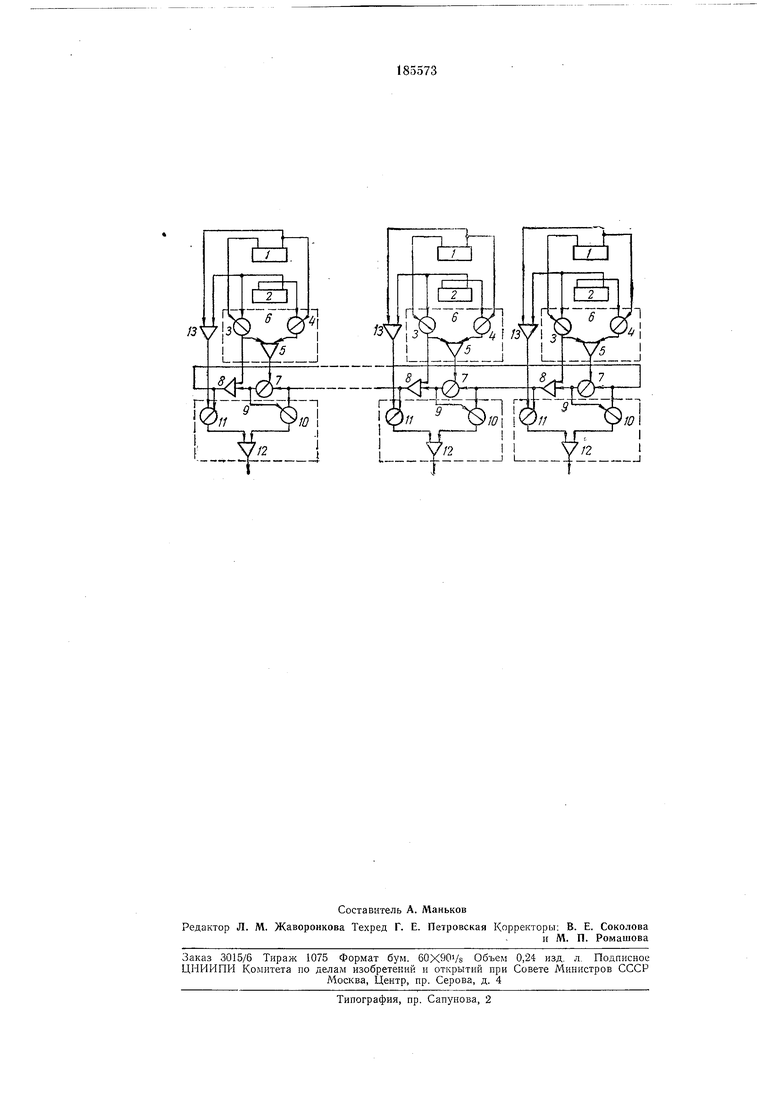

Сумматор содержит триггеры 1 регистра первого слагаемого, триггеры 2 регистра второго слагаемого, элементы 3, 4, 7, 10, 11 «ЗАПРЕТ, схемы 5, 8, 12, 13 «ИЛИ.

В схему входят два регистра, один из которых состоит из триггеров 1, а другой из триггеров 2. Нулевой выход триггера 1 соединен с запретным входом элемента 3 «ЗАПРЕТ, а единичный выход того же триггера соединен с запретным входом элемента 4 «ЗулПРЕТ. Нулевой выход триггера 2 второго слагаемого соединен с «меченым входом схемы 4 «ЗАПРЕТ, а единичный - с «меченым входом элемента 3 «ЗАПРЕТ.

Выходы элементов 3 и 4 «ЗАПРЕТ соединены со входом элемента 5 «ИЛИ, они образуют схему 6 «равнозначности ; схема «равнозначности имеет два выхода, один из которых является выходом схемы 5 «ИЛИ, другой - выходом элемента 3 «ЗАПРЕТ переноса.

Выход схемы 5 «ИЛИ соединен с запретным входом элемен1а 7 «ЗАПРЕТ, который образует вместе со схемой 8 «ИЛИ линию параллельного переноса, представляющую собой последовательно соединенные элементы 7 «ЗАПРЕТ и схемы 8 «ИЛИ.

На другой вход схемы 8 «ИЛИ линии параллельного переноса подается сигнал с выхода элемента 3 «ЗАПРЕТ переноса схемы 6 «равнозначности.

Окончательная сумма формируется при помощи схемы 9 окончательной суммы, которая состоит из двух элементов 10, 11 «ЗАПРЕТ и схемы 12 «ИЛИ.

На «меченый вход элемента 10 подводится сигнал с выхода схемы 8 «ИЛИ младшего разряда - линии параллельного переноса, на запретный вход того же элемента - выход элемента 7 «ЗАПРЕТ данного разряда линии параллельного переноса. На запретный вход элемента 11 «ЗАПРЕТ подводится выход схемы 8 «ИЛИ данного разряда - линии параллельного переноса; на «меченый вход того же элемента - выход схемы 13 «ИЛИ, входы которой соединены с единичными выходами триггеров У и 2 регистров.

Выходы элементов 10 и 11 «ЗАПРЕТ соединены со входами схемы 12 «ИЛИ, выход которой дает окончательную сумму в данном разряде.

Устройство работает следующим образом.

Оба двоичных числа в обратном коде записываются одновременно во все разряды двух регистров.

На первом этапе после приема чисел в триггерах / и 2 формируются сигналы g, р и 2;, где gi - выход схемы 6 «равнозначности, получаемый с выхода элемента 5 PI - другой выход схемы 6 «равнозначности, получаемый с элемента 3 «ЗАПРЕТ «переноса.

ef; 6г А аТубГД а, «;; Pi-bi Д а,; Zi aflbi

Сигналы gi и р I поступают соответственно на входь элемента 7 «ЗАПРЕТ и элемента S «ИЛИ, в результате чего происходит управление линией нараллельного переноса.

На втором этапе заканчивается распространение сигнала переноса по линии параллельного переноса, после чего начинается

третий этап формирования окончательной суммы схемой 9 окончательной суммы.

Линии параллельного переноса управляются следующим образом.

При наличии в триггерах 1 н 2 данного разряда регистров комбинации 01 или 10 элемент 7 «ЗАПРЕТ линии параллельного переноса открыт, так как g 0, Сигнал переноса из младшего разряда распространяется в

старшие разряды по линии параллельного переноса. Если сигнал переноса приходит из младшего разряда в данный разряд, то он используется для формирования суммы схемой 5окончательной суммы в данном разряде.

Сигнал переноса будет формироваться в тех разрядах, где встречается комбинация 11, и будет распространяться по линии параллельного переноса до тех нор, пока не встретит комбинации 00 и И, нри этом элемент 7

«ЗАПРЕТ будет закрыт сигналами «равно-, значности схемой 6 «равнозначности. Сигнал переноса в старший разряд с элемента 3 «ЗАПРЕТ схемы 6 «равнозначности поступает через схему 8 «ИЛИ в линию

параллельного переноса.

Предмет изобретения

Комбинационный двоичный сумматор, содержащий триггерные регистры исходных чисел, цепь параллельного переноса и схемы «равнозначности, отличающийся тем, что, с целью повышения быстродействия и упрощения устройства, выходы триггера каждого

разряда одного регистра соединены с запретными входами двух элементов «ЗАПРЕТ, а противонололсные выходы триггера каждого разряда другого регистра - с соответствующими «мечеными входами этих же элементов, образующих совместно со схемой «ИЛИ, ко входам которой подключены выходы упомянутых элементов, схему «равнозначности, имеющую два выхода, один из которых является выходом схемы «ИЛИ, а другой выходом элемента «ЗАПРЕТ, «меченый вход которого соединен с прямым выходом триггера одного из регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТРУЙНЫЙ ДВОИЧНЫЙ СУММАТОР | 1970 |

|

SU282740A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР НА ФЕРРИТ-ТРАНЗИСТОРНЫХ МОДУЛЯХ | 1970 |

|

SU277409A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| СУММАТОР В КОДЕ ГРЕЯ | 1965 |

|

SU172131A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Многофункциональный регистр | 1986 |

|

SU1411828A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU429423A1 |

Авторы

Даты

1966-01-01—Публикация