Изобретение относится к вычислительной технике и предназначено для преобразования кодов в линиях передачи дискретной информации.

Известные устройства для преобразования двоичного безызбыточного кода в двоичный код постоянного веса, содержащие большое количество логических элементов, критичны к их быстродействию.

Предложенное устройство отличается тем. что выходы всех й-разрядов регистра входного кода соединены через элементы «И логических блоков прямого и обратного кодов с единичными входами первых /е-разрядов регисгра выходного кода, причем вторые входы элементов «И логического блока прямого кода соединены с п-/г+1 выходами счетчика, а входы элементов «И анализатора весовой структуры входного кода соединены с остальными 2k-п выходами счетчика. Выходы анализатора через диодные блоки соединены со входами всех элементов «И логического блока обратного кода и со входами первых fe-элементов «И логического блока прямого кода, а входы последних п-k элементов «И логического блока прямого кода соедииены с /е-выходами счетчика. Это позволяет упростить схему устройства.

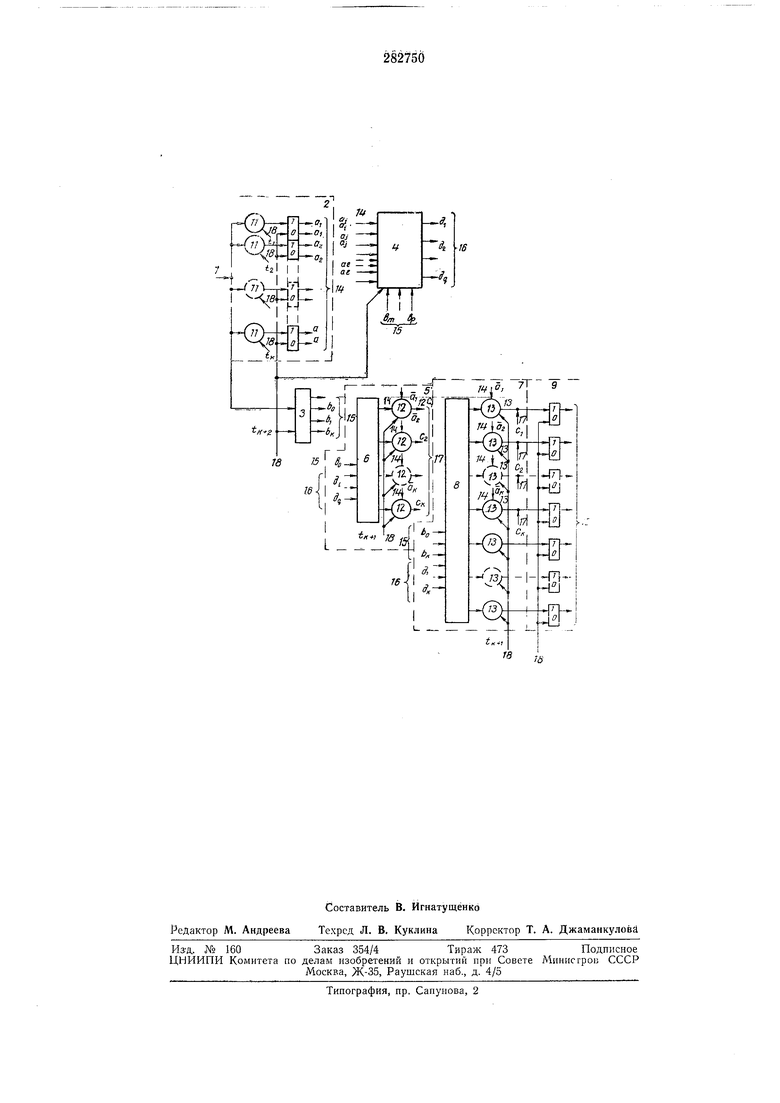

Схема устройства приведена на чертеже.

регистр 2 входного кода, счетчик , анализатор 4 весовой структуры входного кода, логический блок 5 обратного кода, диодный блок 6 логического блока обратного кода, логический блок 7 прямого кода, диодный блок 8 логического блока прямого кода, регистр 9 выходного кода, шнны 10 параллельного выходного кода, элементы «И //-13, выходы 14 регистра входного кода (ai, а ..., UK, «к), выходы /5 счетчика (Ьо-Ьк), выходы 16 анализатора (di-di;), выходы 17 блока обратного кода (ci-CK), шины 18 синхроннзируюш,их импульсов.

С выходов 15 счетчика 3 на анализатор 4 подаются сигналы разрядов Ьт-Ьр, а на блок 6-только сигнал разряда Ьо. На элементы «И 12 подаются лишь сигналы ai-а с вы.ходов 14, а на элементы «И 13-сигналы .

На элементы «И (число которых равно k) по шинам 18 подаются синхронизируюш,ие импульсы (1 - иа первый элемент, tz - на второй элемент и т. д.). На разряды регистра 2, на счетчик 3 и на анализатор 4 по шине 18 подается импульс к+2, на элементы «И 12 и 13- импульс tk+i, на разряды регистра 9 - импульс считывания t.

Устройство работает следуюш,им образом. Сигнал последовательного двоичного безызпает на входы элементов «И 11, которые с помощью синхронизирующнх имнульсов /1-t-k преобразуют последователыный входной код в параллельный, записанный в регистре 2. Входной код поступает также в счетчик 3, который фиксирует вес (число еднниц) в словах входного кода и имеет (k+ состояний.

Сигналы с единичных и нулевых выходов 14 регистра 2 и с выходов 15 счетчика 3 поступают в анализатор 4 и в блоки 5 и 7. Анализатор 4 анализирует весовую структуру входного кода, т. е. наличие определенного числа единиц в разрядах с определенными номерами. Сигналы, вырабатываемые анализатором 4 в зависимости от весовой структуры входного кода, поступают в блоки 5 и 7. Последние, в зависимости от состояния счетчика 3 и сигналов с выходов 16 анализатора 4, переводят в единичное состояние п определенных триггеров регистра 9. Выходной параллельный код считывается с выходов 10 регистра 9 при наличии импульса считывания t.

Рассмотрим преобразование двух слоев - 000 000 000 и 001001000 -девятиразрядного () двоичного безызбыточного кода в двенадцатиразрядный () код веса w &.

Поступление первого слова не изменяет начального состояния регистра 2 и счетчика 3. Цепь bo выходов 15 будет возбуждена. Импульс tid возбуладает цепи выходов 17 элементов «И 12 и выход двенадцатого элемента «И 13. В единичное состояние переходят: первый, второй, третий, четвертый, пятый и двенадцатый триггеры регистра 9, т. е. получим слово 111110000001.

При поступлении второго слоя возбуждаются цепи из и Яб выходов 14 регистра 2, цепь bz выходов 15 счетчика 3, цепь dz выходов 16 анализатора 4, цепи С7-Сд выходов 17 блока 5, выходы третьего, десятого и двенадцатого элементов «И 13, т. е. в регистре 9 появляется слово 0001000111101.

Предмет изобретения

Устройство для преобразования двоичного безызбыточного кода в двоичный код постоянного веса, содержащее й-разрядный регистр входного кода, л-разрядный регистр выходного кода, элементы «И, счетчик, анализатор весовой структуры входного кода, выполненный на триггерах и элементах «И, логические блоки прямого и обратного кодов, выполненные на диодных блоках и элементах «И, отличающееся тем, что, с целью упрощения схемы, выходы всех /г-разрядов регистра входного кода соединены через элементы «И логических блоков прямого и обратного кодов с единичными входами первых jfe-разрядов регистра выходного кода, причем вторые входы элементов «И логического блока прямого кода соединены с п- k+l выходами счетчика, а входы элементов «И анализатора весовой структуры входного кода соединены с остальными 2k-п выходами счетчика; выходы анализатора через диодные блоки соединены со входами всех элементов «И логического блока обратного кода и со входами первых k элементов «И логического блока прямого кода, а входы последних п-k элементов «И логического блока прямого кода соединены с -выходами счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Преобразователь двоичного кода в код постоянного веса | 1982 |

|

SU1089572A1 |

| УСТРОЙСТВО для ПЕРЕКОДИРОВАНИЯ ДВОИЧИОГО КОДА В ДВОИЧНЫЙ код с постоянным ВЕСОМ | 1967 |

|

SU191895A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1983 |

|

SU1124282A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Устройство формирования укороченного псевдослучайного @ -разрядного кода | 1982 |

|

SU1200424A1 |

| Двоичный счетчик | 1983 |

|

SU1150758A1 |

Даты

1970-01-01—Публикация