Известны цифровые фильтры для статистической обработки низкочастотных сигиалов, содержащие запоминающие устройства для хранения значений сигналов, адресные устройства, счетные регистры, логические схемы управления и сглаживающие устройстг а.

Предложенный фильтр отличается от известных тем, что в нем сглаживающее устройство содержит регистр для хранения одноименных разрядов п обрабатываемых чисел со схемами передачи прямым и обратным кодом, регистр весовых коэффициентов, счетный регистр со схемой передачи прямым кодом, регистр оперативной памяти со схемой передачи прямым кодом, схему комбинационного сравнения, коммутатор «п трехвходовых логических схем // и я-входовую логическую схему ИЛИ; причем выходы схемы передачи регистра .разрядов подключены ко входам региетра весовых коэффициентов; выходы регистра весовых коэффициентов подсоединены к первым входам соответствующих схем И; ко второму и третьему входам каждой из схем И подключены прямые выходы регистра разрядов чисел и одноименные выхода коммутатора; выходы схем Я соединены со входами схемы ИЛИ; выход схемы ИЛИ подключен ко входу счетного регистра, выход которого подсоединен, как и один из выходов коммутатора, к,схеме комбинационного сравнения и через

схему передачи ко входу регистра онерати иой памяти; выход схемы передачи регистра оперативной памяти соединен со входом счетного регистра; а выходы схемы комбинациониого сравнения подключены к управляющим входам схем передачи регистра разрядов чисел, счетного регистра н регистра оперативной памяти.

Это повышает эффектшмчость обработки и увеличивает быстродействие фильтра.

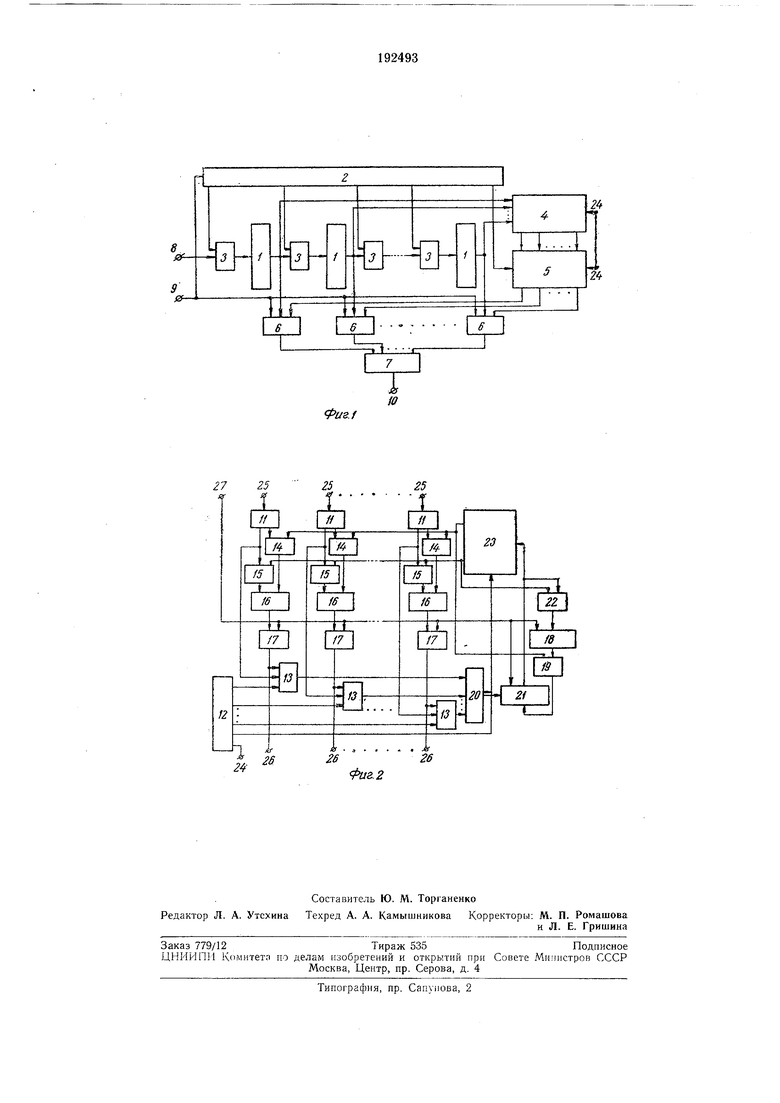

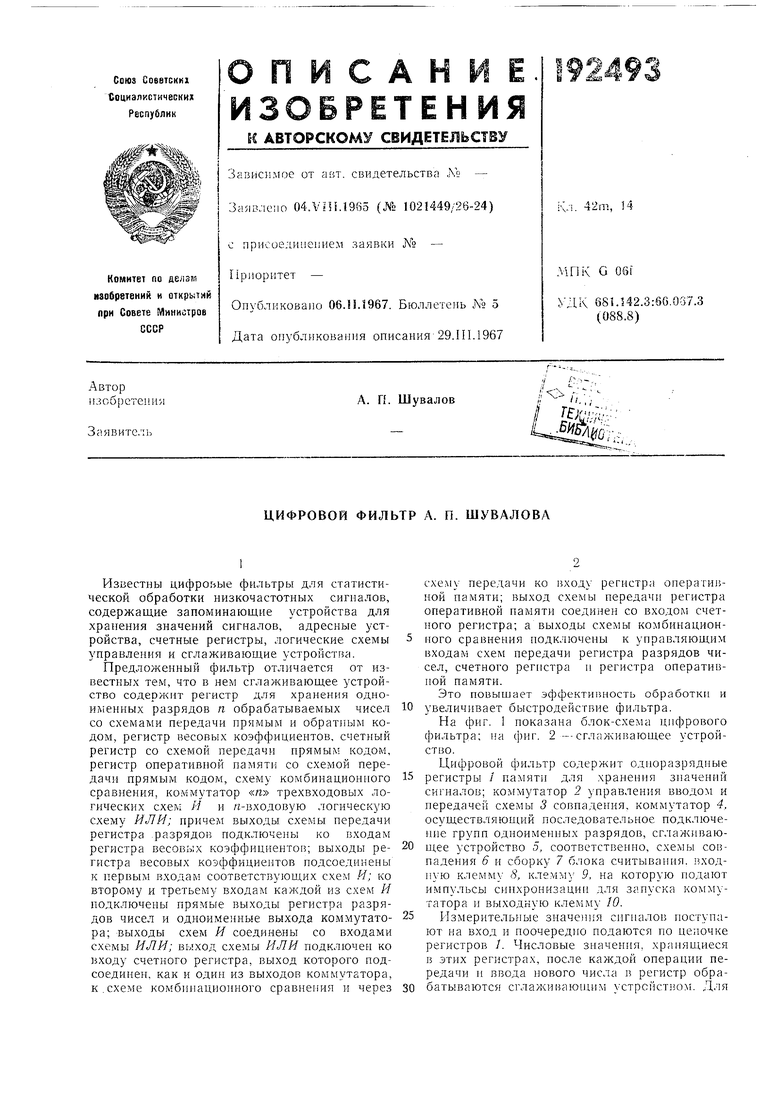

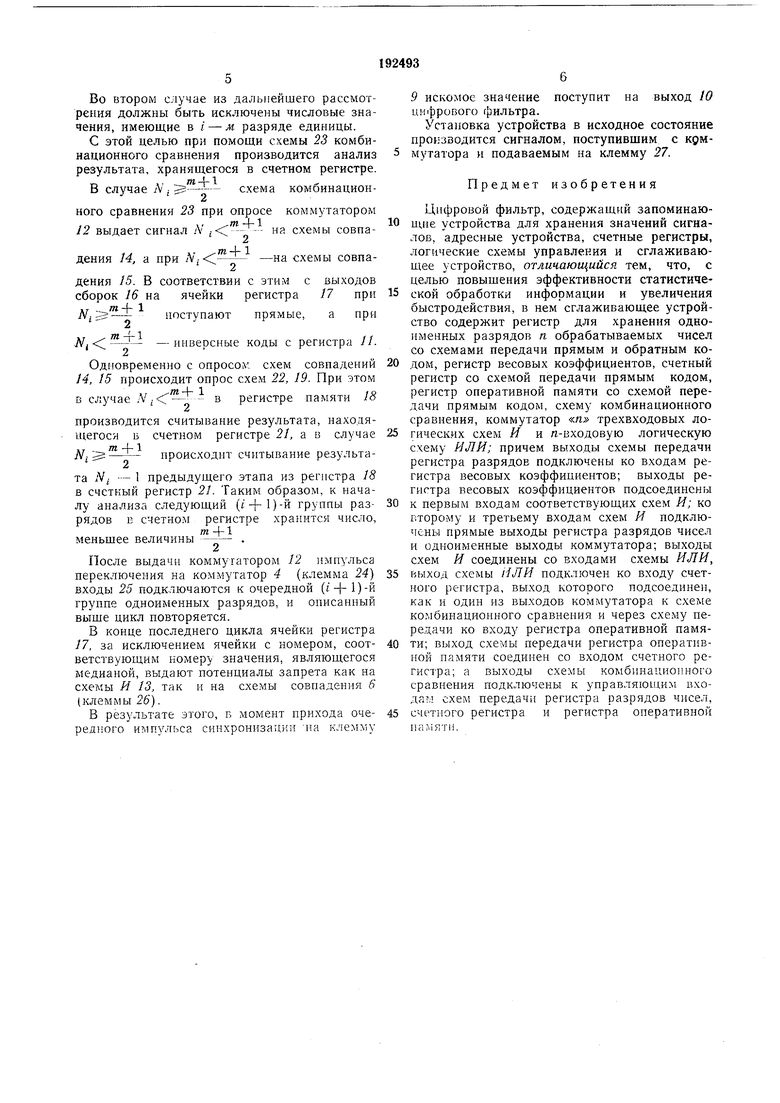

На фиг. 1 показана блок-схема цифрового фильтра; на фиг. 2 --сглаживающее устройство.

Цифровой фильтр содержит одноразрядные регистры / памяти для хранения значений сигналов; коммутатор 2 управления вводом и передачей схемы 3 совпадения, коммутатор 4, осуществляющий последовательное подключение групп одноименных разрядов, сг.таживаюН1,ее устройство 5, соответственно, схемы совпадения 6 и сборку 7 блока считывания, входную клемму 8, клеД1му 9, на которую подают импульсы синхронизации для зануска коммутатора н выходную клемму 10.

Измерительные значе) сигналов ностунают на вход и поочередно подаются по цепочке регистров 1. Числовые значення, хранящиеся в этих регистрах, после каждой операции передачи и ввода нового числа в регистр обрабатываются сглаживаюии1м устройством. Для

этого коммутатор 4 подключает поочередно вход сглаживающего устройства к одноименным группам разрядов регистра, начиная с группы старших разрядов.

Сглаживающее устройство обрабатывает информацию. После этого на одну из схем совпадения 6 с соответствующим порядковым номером подается сигнал разрешения, в результате чего в момент поступления на клемму 9 очередного импульса синхронизации искомое число поступает на сборку 7 н далее на вход (клемма 10) цифрового фильтра.

Особенность предложенного устройства состоит в том, что при обработке случайного процесса определяется наиболее достоверное значение, которое берется в качестве сглаженного значения, относящегося к центру анализируемого временного интервала. В качестве достоверного значения берется медиана, представляющая собой срединное значение ранжированного ряда анализируемой совокупности измерений.

Использование медианы в качестве статистической характеристики носледовательности измерительных значений обеспечивает эффективное определение достоверных значений результатов измерений при наличии как отдельных сбоев, так и рассеивания измерительных точек в некоторой области. Причем характер распределения амплитуд сбойных значений не оказывает существегп-юго влияния на точность результатов обработки, а также на достоверную передачу различных процессов, которые могут быть охарактеризованы как неубывающие или как невозрастающие в том числе и нрямоугольные нерепады значений амплитуд. Кроме того, обеспечивается возможность повышения эффективности обработки за счет увеличения длительности интервала обработки без внесения искажений в исследуемый процесс.

Для сокращения числа логических онераций и объема аппаратуры, находят медиану путем поочередного анализа одноименных разрядов рассматриваемых числовых значений.

Сглаживающее устройство (см. фиг. 2) содержит яч-ейку регистра // для хранения одноименных разрядов обрабатываемых чисел; коммутатор 12, производящий опрос одноименных разрядов чисел; трехвходовые схемы Я 13, осуществляющие логическое умножение анализируемых разрядов на весовые коэффициенты; схемы 14-/5 совпадения; схемы сборки 16 (схемы 14, 15, 16 образуют схему передачи регистра разрядов), ячейку регистра

17хранения весовых коэффицие1гтов; регистр

18оперативной памяти, предиазиаченны ; для хранения промежуточных результатов анализа, и его схему 19 передачи, предназначенной для вывода числсиых нз регистра 18; многовходовую схему ИЛИ 20 счетный регистр 21; 22 передачи счетного регистра; схему 23 комбинац1юн1юго cpaii-eium. клемму 24 передачи управления коммутатора, входные клеммы 25 схемы поиска меднаны;

выходные клеммы 26 схемы поиска медианы/ клемму 27 установки.

Сглаживающее устройство осуществляет поочередный анализ одноименных разрядов рассматриваемой группы чисел с целью поэтапного исключения из дальнейшего рассмотрения числовых значений, не являющихся медианой. При этом результаты анализа предыдущих разрядов учитываются при анализе последующих с помощью весовых коэффициентов, принимающих значения, равные 1 или 0. Лля упрощения обработки число одновременно анализируемых значений п берется нечетным.

Одноименные разряды чисел, начиная со старщего, поочередно поступают с коммутатора 4 через входы 25 на регистр П памяти, где они хранятся до начала обработки следуюидей группы разрядов.

При аиализе каждой одноименной группы разрядов коммутатор 12 осуществляет сброс схем И 13, на которые кроме чисел, хранящихся в регистре 11, поступают также весовые коэффициенты с регистра 17, полученные

в результате предшествующего анализа более старщих разрядов.

Равенство нулю весового коэффициента, хранящегося в каком-либо разряде регистра 17, означает, что из дальнейшего рассмотрения должно быть исключено число с порядковым номером, соответствующим номеру этого разряда. Поскольку анализ числовых 3 iaчений производится, начиная со старших разрядов, из дальнейшего рассмотрения постепенно исключаются числа, имеющие наиболь иие или наименьшие величины.

Б результате логического умножения числовых значений группы разрядов на весоьые коэффициенты с выхода сборки на счетный

регистр 21 поступают импульсы, число которых равно числу единичных значений, содержаш,нхся среди этой группы разряде без учета разрядов числовых значений, нсключепных из рассмотрения ранее.

Счетный регистр 21 к началу анализа i - лразрядов содержат число , выражающее количество чисел, нревосходящих по своей величине и:едиаку и имеющих наибольн1ие величины.

В результате анализа разрядов счетный регистр содержит число /V; . для которого выт - пслняются условия: лиоо :V,. э -, лиоо

Л

и нервом сл},ча1 значение меднаны следует искать среди чисел.} которых / -- е разряды являются единицами, так как в этом случае общее

колнчест о ;|;и больп;ях :нс/;ог:;1л значений превысит половину общего числа одновременно аналнзнрхсмых пзмер(П1Г. П)и этом из дальненн его рассмотрения должны быть исключены числовые значения, имеющне в /-е Во втором случае из дальнейшего рассмотрения должны быть исключены числовые значения, имеющие в / - м разряде единицы. С этой целью при помощи схемы 23 комбинационного сравнения производится анализ результата, хранящегося в счетном регистре. В случае N схема комбинационного сравнения 23 при опросе коммутатором ) W Ч- 1 12 выдает сигнал Л .;--- на схемы совпа Jх wi Ч 1 дения 14, а при C-- -на схемы совпадения 15. В соответствии с этим свыходов сборок 16 на ячейки регистра17 при г-- поступают прямые,а при т Z г i1 i -инверсные коды с регистра 11. Одновременно с опросов схем совпадений 14, 15 происходит опрос схем 22, 19. При этом в случае N, - в регистре памяти 18 производится считывание результата, находящегося в счетном регистре 21, а в случае ...771-1-1 происходит считывание результата ;V; - 1 предыдущего этапа из регистра 18 в счетный регистр 21. Таким образом, к началу анализа следующий (г + 1)-й группы разрядов Е счетном регистре хранится число, т - меньшее величины . После выдачи коммутатором /2 импульса переключения на коммутатор 4 (клемма 24) входы 25 подключаются к очередной (г-|- 1)-й группе одноименных разрядов, и описанный выше цикл повторяется. В конце последнего цикла ячейки регистра П, за исключением ячейки с номером, соответствующим номеру значения, являющегося медианой, выдают потенциалы запрета как на схемы И 13, так и на схемы совпадения 6 (клеммы 26. В результате этого, Б момент прихода очередного иАШульса синхронизации на клемму .9 искомое значение поступит на выход 10 цифрового фильтра. Установка устройства в исходное состояние производится сигналом, поступившим с KQMмутатора и подаваемым на клемму 27. Предмет изобретения Цифровой фильтр, содержащий запоминающне устройства для хранения значений сигналов, адресные устройства, счетные регистры, логические схемы управления и сглаживающее устройство, отличающийся тем, что, с целью повышения эффективности статистической обработки информации и увеличения быстродействия, в нем сглаживающее устройство содержит регистр для хранения одноименных разрядов п обрабатываемых чисел со схемами передачи прямым и обратным кодом, регистр весовых коэффициентов, счетный регистр со схемой передачи прямым кодом, регистр оперативной памяти со схемой передачи прямым кодом, схему комбинационного сравнения, коммутатор «п трехвходовых логических схем И и п-входовую логическую схему ИЛИ; причем выходы схемы передачи регистра разрядов подключены ко входам регистра весовых коэффициентов; выходы регистра весовых коэффициентов нодсоединены к первым входам соответствующих схем И; ко второму и третьему входам схем Я подключены прямые выходы регистра разрядов чисел и одноименные выходы коммутатора; выходы схем И соединены со входами схемы ИЛИ, выход схемы ИЛИ подключен ко входу счетного регистра, выход которого подсоединен, как и один из выходов коммутатора к схеме комбинационного сравнения и через схему нередачи ко входу регистра оперативной памяти; выход схемы передачи регистра оперативной памяти соединен со входом счетного регистра; а выходы схемы комбинационного сравнения подключены к управляющим входатл схем передачи регистра разрядов чисел, счетного регистра и регистра оперативной наняти.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ЧИСЛОВЫХ ВЕЛИЧИН | 1965 |

|

SU167366A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ДАННЫХ | 1991 |

|

RU2028664C1 |

| Устройство для сбора телеметрителеметрической информации | 1975 |

|

SU527727A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для передачи телеметрической информации | 1974 |

|

SU512484A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

Авторы

Даты

1967-01-01—Публикация