Изйёстны Цифровые устройства дЛя решения рекуррентных уравнений, содержащие запоминающее устройство, арифметическое устройство, устройство управления и устройство ввода-вывода.

Предлагаемое устройство отличается тем, что запоминающее устройство выполнено на сдвигающих регистрах, в разрядах которых хранится значение рекуррентно вычисляемых величин, выходы разрядов величин вплоть до п-1 через вентили, связанные с устройством управления, соединены со входами множительного устройства выход множительного устройства соединен со входо.м накопительного сумматора, выход которого через вентиль, соединенный с устройством управления, связан со входом записи п-то значения величины в запоминающее устройство.

Это поз1воляет увеличить быстродействие устройства.

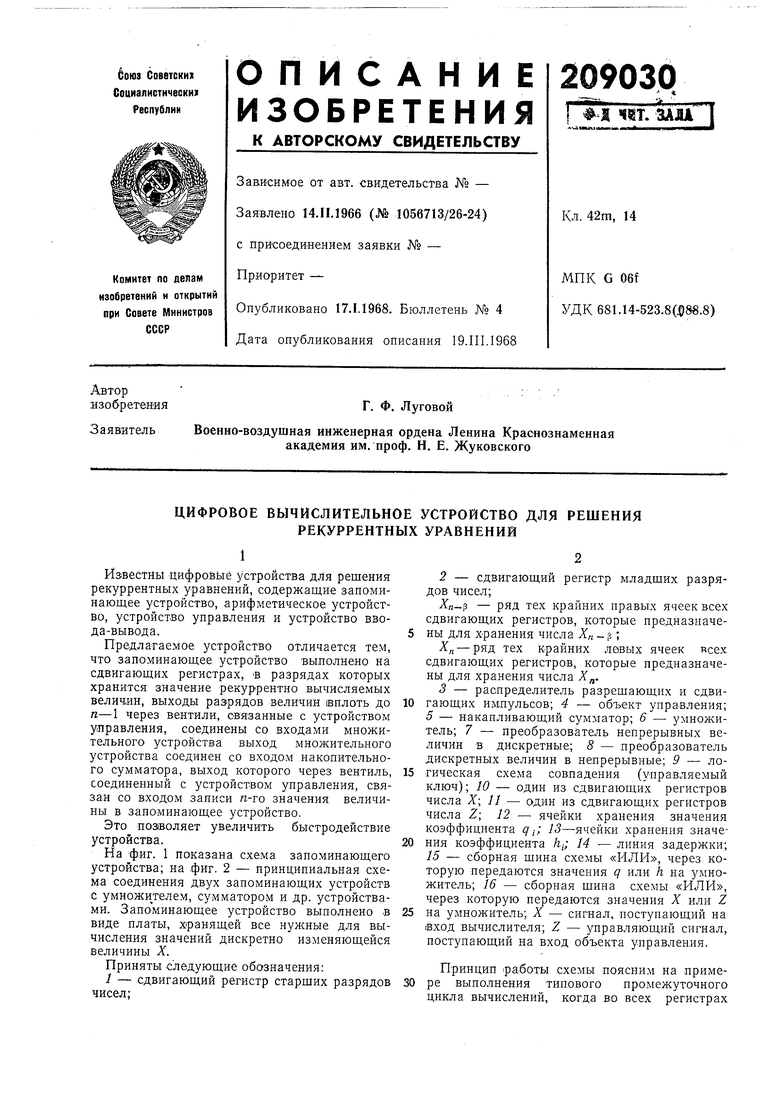

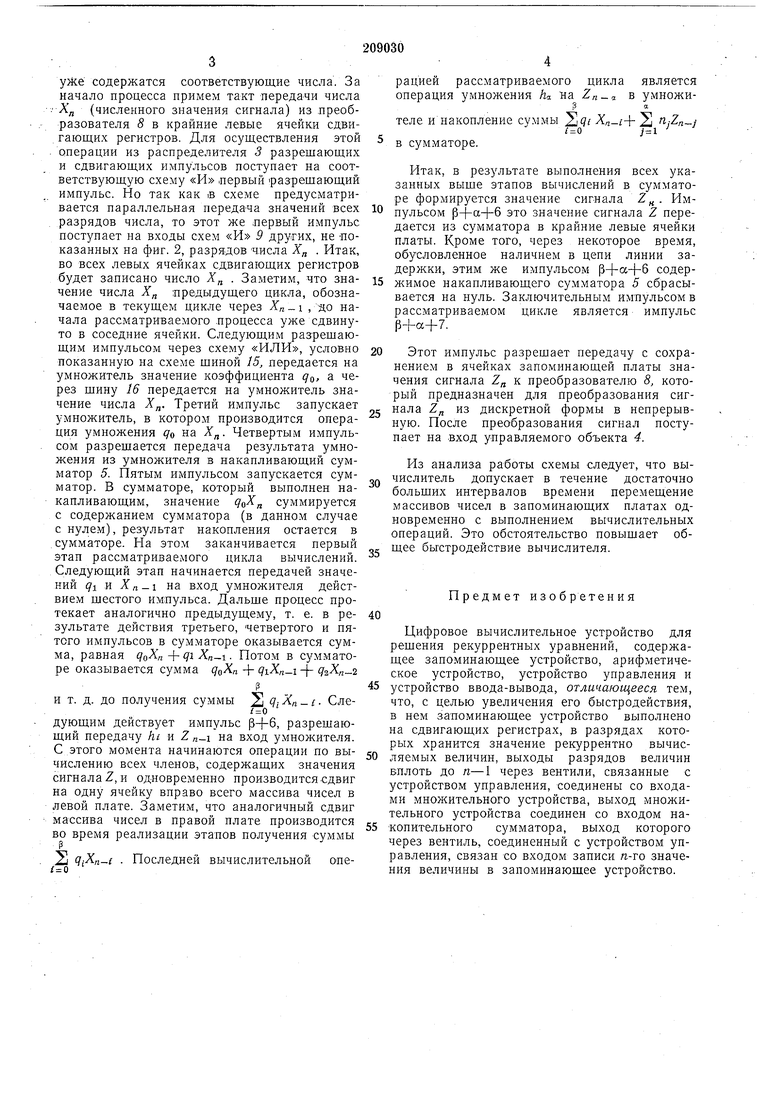

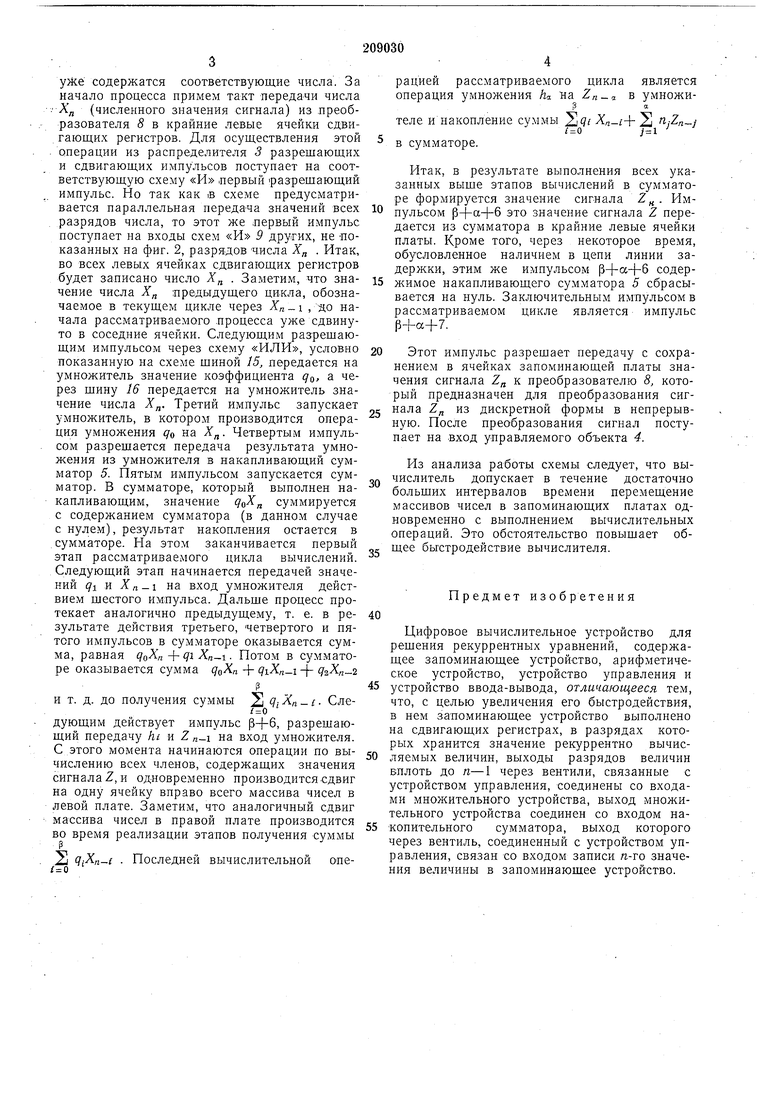

На фиг. 1 показана схема запоминающего устройства; на фиг. 2 - принципиальная схема соединения двух запоминающих устройств с умножителем, сумматором и др. устройствами. Запоминающее устройство выполнено в виде платы, хранящей все нужные для вычисления значений дискретно изменяющейся величины X.

2- сдвигающий регистр младших разрядов чисел;

ХЛ-Р - ряд тех крайних правых ячеек всех сдвигающих регистров, которые предназначены для хранения числа X,i р;

-ряд тех крайних левых ячеек всех сдвигающих регистров, которые предназначены для хранения числа Х,

3- распределитель разрешающих и сдвигающих импульсов; 4 - объект управления;

5 - накапливающий сумматор; 6 - умножитель; 7 - преобразователь непрерывных величин в дискретные; 5 - преобразователь дискретных величин в непрерывные; 9 - логическая схема совпадения (управляемый ключ); 10 - один из сдвигающих регистров числа Х 11 - один из сдвигающих регистров числа Z; 12 - ячейки хранения значения коэффициента qi, 13-ячейки хранения значения коэффициента 14 - линия задержки; 15 - сборная шина схемы «ИЛИ, через которую передаются значения q или h на умножитель; 16 - сборная шина схемы «ИЛИ, через которую передаются значения X или Z

на умножитель; X - сигнал, поступающий на (ВХОД вычислителя; Z - управляющий сигнал, поступающий на вход объекта управления.

уже содержатся соответствующие числа. За начало процесса примем такт передачи числа

Х„ (численного значения сигнала) из .преобразователя 8 в крайние левые ячейки сдвигающих регистров. Для осуществления этой

. операции из распределителя 3 разрещающих и сдви.гающих импульсов поступает на соответствующую схему «И первый разрещающий импульс. Но так как в схеме предусматривается параллельная передача значений всех разрядов числа, то этот же .первый импульс поступает на входы схем «И 9 других, не показанных на фиг. 2, разрядов числа А„ . Итак, во всех левых ячейках сдвигающих регистров будет записано число Х„ . Заметим, что значение числа Х предыдущего цикла, обозначаемое в текущем цикле через Хп- , до начала рассматриваемого процесса уже сдвинуто в соседние ячейки. Следующим разрешаюЩИ1М импульсом через схему «ИЛИ, условно показанную на схеме шиной 15, передается на умножитель значение коэффициента q, а через щину 16 передается на умножитель значение числа Х„. Третий импульс запускает умножитель, в котором производится операция умножения 90 на Х. Четвертым импульсом разрешается передача результата умножения из умножителя в накапливающий сумматор 5. Пятым импульсом запускается сумматор. В сумматоре, который выполнен накапливающим, значение суммируется с содержанием сумматора (в данном случае с нулем), результат накопления остается в

.сумматоре. На этом заканчивается первый этап рассматриваемого цикла вычислений. Следующий этап начинается передачей значений 1 и Хп.- на вход умножителя действием шестого импульса. Дальше процесс протекает аналогично предыдущему, т. е. в результате действия третьего, четвертого и пятого импульсов в сумматоре оказывается сумма, равная q Xfi-{-qi Хп-. Потом в сумматоре оказывается сумма -}- -j-

И Т. д. до получения суммы 2 Сле/ 0

дующим действует импульс р+6, разрешающий передачу ht и Z n-i на вход умножителя. С этого момента начинаются операции по вычислению всех членов, содержащих значения сигнала Z, и одновременно производится сдвиг на одну ячейку вправо всего массива чисел в левой плате. Заметим, что аналогичный сдвиг массива чисел в правой плате производится во время реализации этапов получения суммы

2 ( Последней вычислительной опе1 0

рацией рассматриваемого цикла является операция умножения Ла на 2„ в умножи3ее

теле и накопление суммы 2 Хп-1+ S n.-Zft-i

в сумматоре.

Итак, в результате выполнения всех указанных выше этапов вычислений в сумматоре формируется значение сигнала 2„. Импульсом |3-j-a+6 это значение сигнала Z передается из сумматора в крайние левые ячейки платы. Кроме того, через некоторое время, обусловленное наличием в цепи линии задержки, этим же импульсом |3+а+6 содержимое накапливающего сумматора 5 сбрасывается на нуль. Заключительным импульсом в рассматриваемом цикле является импульс Р+а+7.

Этот импульс разрешает передачу с сохранением в ячейках запоминающей платы значения сигнала 2„ к преобразователю 8, который предназначен для преобразования сигнала 2„ из дискретной формы в непрерывную. После преобразования сигнал поступает на вход управляемого объекта 4.

Из анализа работы схемы следует, что вычислитель допускает в течение достаточно больщих интервалов времени перемещение массивов чисел в запоминающих платах одновременно с выполнением вычислительных операций. Это обстоятельство повышает общее быстродействие вычислителя.

Предмет изобретения

Цифровое вычислительное устройство для рещения рекуррентных уравнений, содержащее запоминающее устройство, арифметическое устройство, устройство управления и

устройство ввода-вывода, отличающееся тем, что, с целью увеличения его быстродействия, в нем запоминающее устройство выполнено на сдвигающих регистрах, в разрядах которых хранится значение рекуррентно вычисляемых величин, выходы разрядов величин вплоть до п-1 через вентили, связанные с устройством управления, соединены со входами множительного устройства, выход множительного устройства соединен со входом накопительного сумматора, выход которого через вентиль, соединенный с устройством управления, связан со входом записи п-то значения величины в запоминающее устройство.

, , .-г/

х4-,i,/X

i/ X ХТГ

/ //л

ХГ/П

JJ т т

;й/е.

)г

//7Л- Х(п-г)г

(п-Л)о

/ Л/ЗУг , ,/ /

х/ /

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Арифметическое устройство для цифровой фильтрации с автоматической регулировкой усиления | 1979 |

|

SU881987A1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Цифровой преобразователь координат | 1981 |

|

SU1076903A1 |

| Контроллер измерительного преобразователя | 1988 |

|

SU1541632A1 |

| Устройство для решения системы линейных уравнений | 1987 |

|

SU1411776A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Генератор широкополосных случайных процессов | 1980 |

|

SU881743A1 |

| Цифровое множительно-делительное устройство | 1990 |

|

SU1730623A1 |

Даты

1968-01-01—Публикация