Известны заноминающие устройства для знаковой индикации, содерл ащие блок оперативной памяти, подключенный к дешифратору адреса и разрядным фор.мирозателям, и; буферный регистр, соединенный с блоком управления.

Описываемое устройство отличается тем, что в нем блок оперативной памяти подключен к буферному регистру через блок параллельного сквозного переноса на импульсных трапзисторных ключах с ипульсными источниками электродвижущей силы, соединенный с дешифратором адреса и разрядными формирователями.

Это позволяет осуществить на экране синтез динамического изображения больщого количества символов.

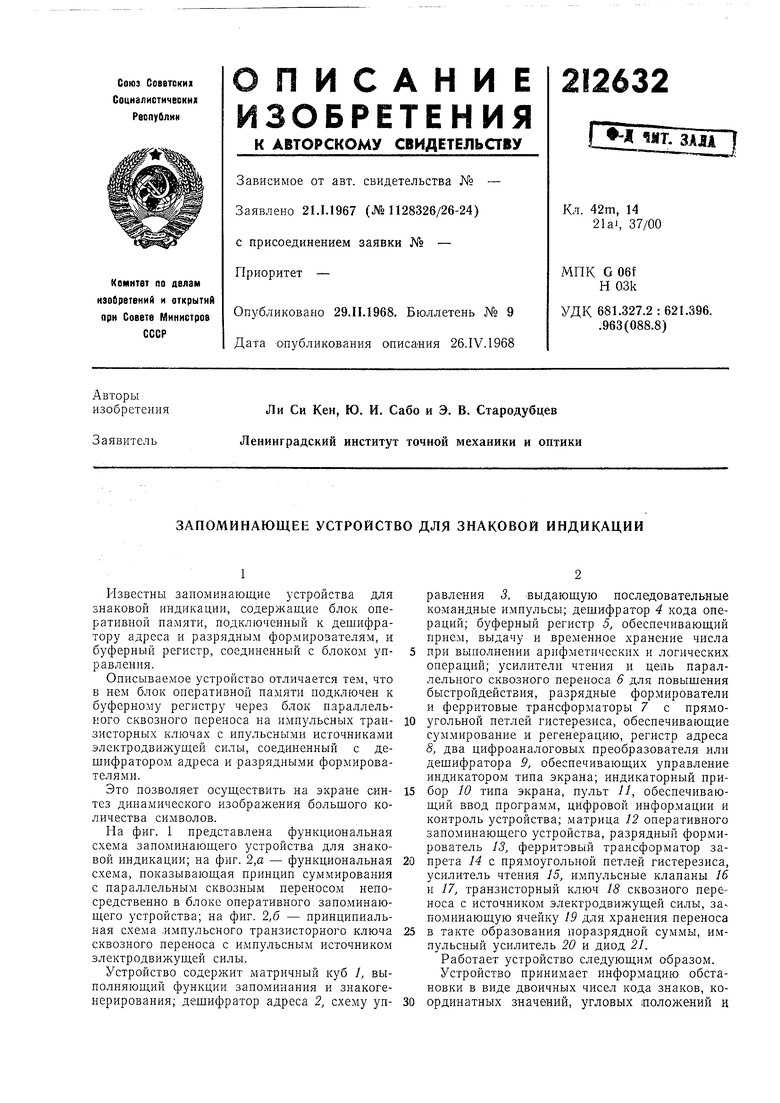

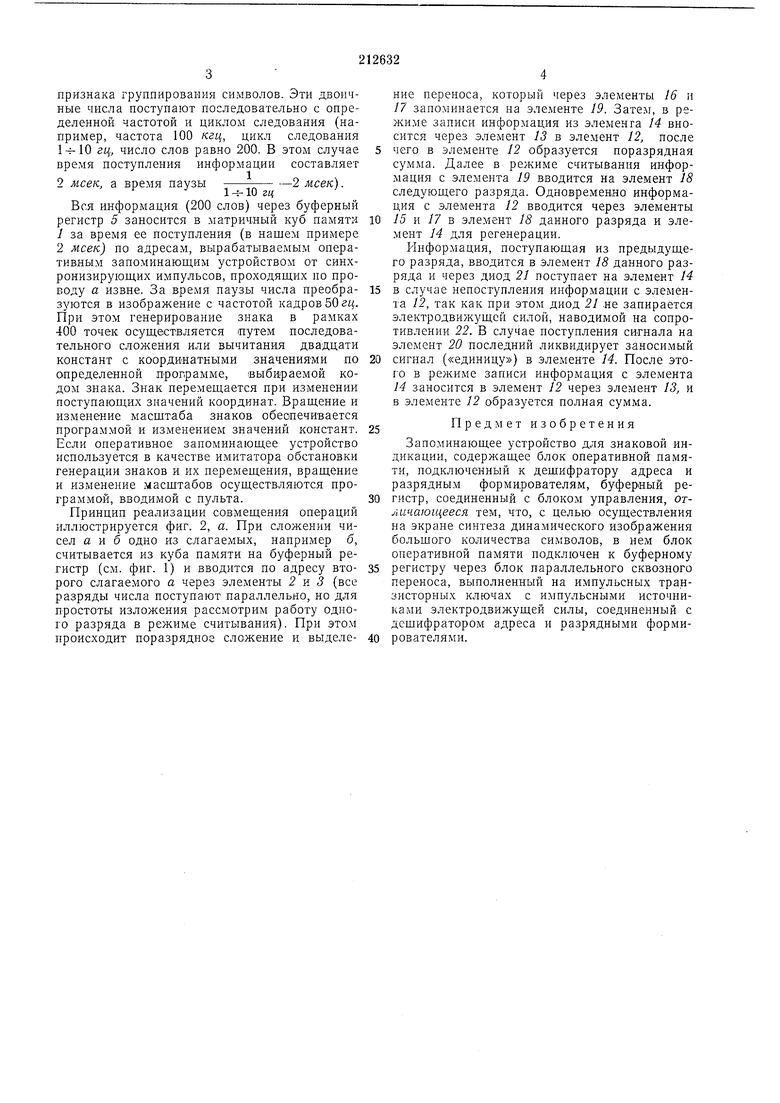

На фиг. 1 представлена функциональная схема запоминающего устройства для знаковой индикации; на фиг. 2,а - функциональная схема, показывающая принцип суммирования с параллельным сквозным переносом непосредственно в блоке оперативного запоминающего устройства; на фиг. 2,6 - принципиальная схема .импульсного транзисторного ключа сквозного переноса с импульсным источником электродвижущей силы.

равления 3, 1выдающую последовательные командные импульсы; дешифратор 4 кода операций; буферный регистр 5, обеспечивающий прием, выдачу и временное хранение числа при выполнении арифметических и логических операций; усилители чтения и цепь параллельного сквозного переноса 6 для повышения быстройдейстзия, разрядные формирователи и ферритовые трансформаторы 7 с прямоугольной петлей гистерезиса, обеспечивающие суммирование и регенерацию, регистр адреса 8, два цифроаналоговых преобразователя или дешифратора 9, обеспечивающих управление индикатором типа экрана; индикаторный прибор 10 типа экрана, пульт Л, обеспечивающий ввод программ, цифровой информации и контроль устройства; матрица 12 оперативного запоминающего устройства, разрядный формирователь 13, ферритэвый трансформатор запрета 14 с прямоугольной петлей гистерезиса, усилитель чтения 15, импульсные клапаны 16 и 17, транзисторный ключ 18 сквозного переноса с источником электродвижущей силы, запоминающую ячейку 19 для хранения переноса в такте образования поразрядной суммы, импульсный усилитель 20 и диод 21. признака группирования символов. Эти двоичные числа поступают последовательно с определенной частотой и циклом следования (например, частота 100 кгц, цикл следования 1-f-lO гц, число слов равно 200. В этом случае время поступления информации составляет 2 мсек, а время паузы2 мсек). Вся информация (200 слов) через буферный регистр 5 заносится в матричный куб памяти 1за время ее поступления (в нашем примере 2мсек) по адресам, вырабатываемым оперативным запоминающим устройством от синхронизирующих импульсов, проходящих по проводу а извне. За время паузы числа преобра- 15 зуются в изображение с частотой кадров 50 eif. При этом генерирование знака в рамках 400 точек осуществляется путем последовательного сложения или вычитания двадцати констант с координатными значениями по 20 определенной программе, выбираемой кодом знака. Знак перемещается при изменении поступающих значений координат. Вращение п изменение масщтаба знаков обеспечивается програм.мой и изменением значений констант. 25 Если оперативное запоминающее устройство используется в качестве имитатора обстановки генерации знаков и их перемещения, вращение и изменение масщтабов осуществляются программой, вводимой с пульта.30 Принцип реализации совмещения операций иллюстрируется фиг. 2, а. При сложении чисел а и б одно из слагаемых, например б, считывается из куба памяти на буферный регистр (см. фиг. 1) и вводится по адресу вто- 35 рого слагаемого а через элементы 2 и 3 (все разряды числа поступают параллельно, но для простоты изложения рассмотрим работу одного разряда в режиме считывания). При этом происходит поразрядное сложение и выделе- 40 5 10 ние переноса, который через элементы 16 и 17 запоминается на элементе 19. Затем, в режиме записи информация из элемента 14 вносится через элемент 13 в элемент 12, после чего в элементе 12 образуется поразрядная сумма. Далее в режиме считывания информация с элемента 19 вводится на элемент 18 следующего разряда. Одновременло информация с элемента 12 вводится через элементы 15 и 17 в элемент 18 данного разряда и элемент 14 для регенерации. Информация, поступающая из предыдущего разряда, вводится в элемент 18 данного разряда и через диод 21 поступает на элемент 14 в случае непоступления информации с элемента 12, так как при этом диод 21 .не запирается электродвижущей силой, наводимой на сопротивлении 22. В случае поступления сигнала на элемент 20 последний ликвидирует заносимый сигнал («единицу) в элементе 14. После этого в режиме записи информация с элемента 14 заносится в элемент 12 через элемент 13, и в элементе 12 образуется полная сумма. Предмет изобретения Запоминающее устройство для знаковой индикации, содержащее блок оперативной памяти, подключенный к дешифратору адреса и разрядным формирователям, буферный регистр, соединенный с блоком управления, отличающееся тем, что, с целью осуществления па экране синтеза динамического изображения больщого количества символов, в нем блок оперативной памяти подключен к буферному регистру через блок параллельного сквозного переноса, выполненный на импульсных транзнсторпых ключах с импульсными источниками электродвижущей силы, соединенный с дещифратором адреса и разрядными формирователями.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| Нерекурсивный цифровой фильтр | 1984 |

|

SU1171995A1 |

| Цифровое устройство числового программного управления | 1971 |

|

SU441858A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| Микропроцессорное вычислительное устройство | 1982 |

|

SU1269145A1 |

| Устройство для программного управления | 1981 |

|

SU987579A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Многокоординатное устройство для управления | 1987 |

|

SU1522155A1 |

Даты

1968-01-01—Публикация