1

Изобретение может быть использовано автономно в Качестве специализированного арифметического устройст1ва в системах автоматического регулирования, в телеметрии, автоматике и т. д. или входить в качестве предпроцессора в вычислительные системы для ускорения и повышения эффективности вычислений в реальпом .масштабе времени.

Известны устройства двоичного деления по традиционным алгоритмам, состоящие из регистров делимого, делителя и частпого, сумматора и схемы упра вления.

Цель изобретения - повышение быстродействия устройства.

Цель достигается тем, что предлагаемое устройство содерл ит матричную схему умножеиия, накопительный сумматор, схему расширения, преобразователь дополнительного кода, схему сравнения, распределитель тактовых импульсов и вентили, пр.ичем выход регистра делимого соединен с входом схемы сравнения, выход накопительного сумматора соединен с вторым входом схемы сравнения, выходы регистров делителя и частного соединены с соответствующимИ входами матрицы умно кен1ия, выход которой соединен с входами накопительного сумматора и преобразователя кодов, выход которого соединен с входом накопительного сумматора через вентили, вторые входы которых соединены с входом схемы расширения и с первым выходом схемы сравнения, выход схемы расширения соединен с входом регистра частного через вентили, в,тор.ые в.ходы которых соединены с выходом распределителя тактовых импульсов, второй выход схемы сравнения соединен с вторым входом преобразователя кодов, третий выход схемы сравнения соединен с входом распределителя тактовых импульсов.

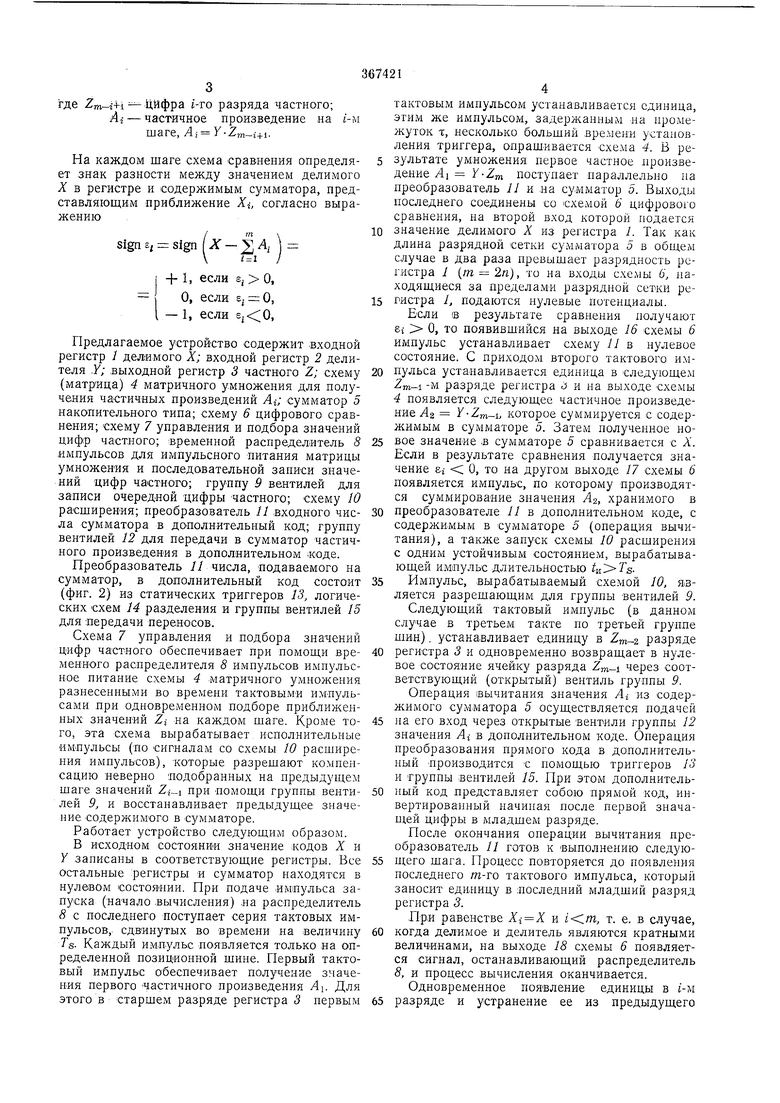

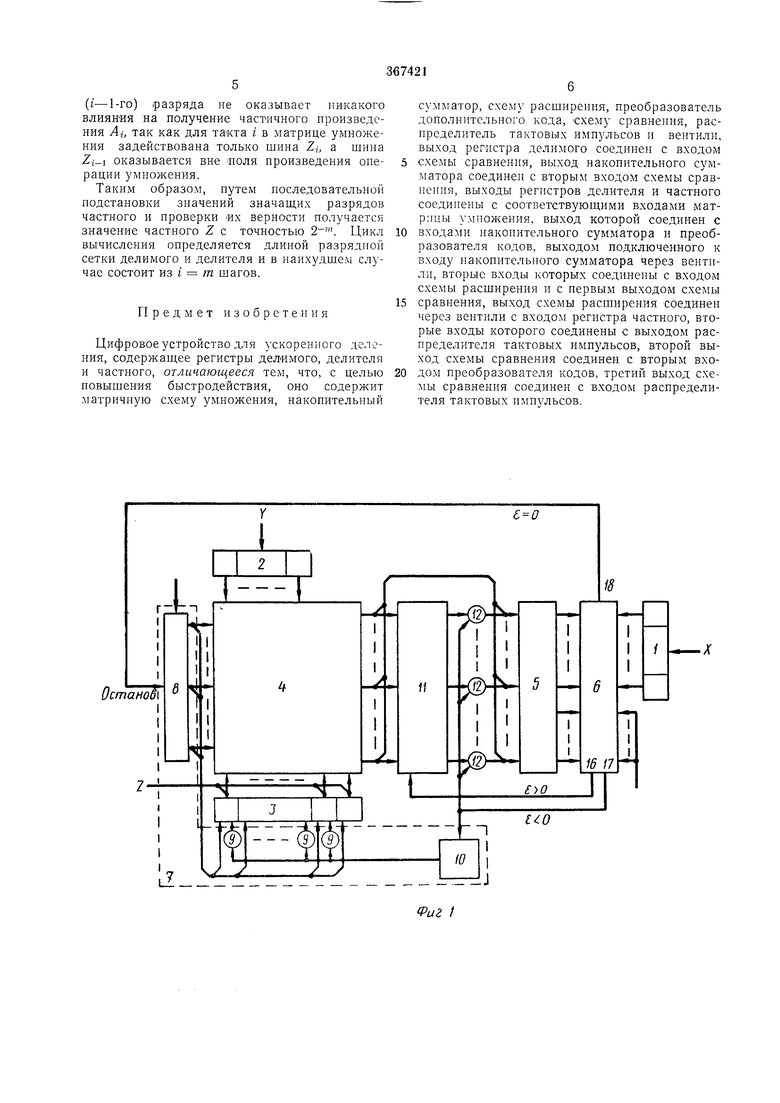

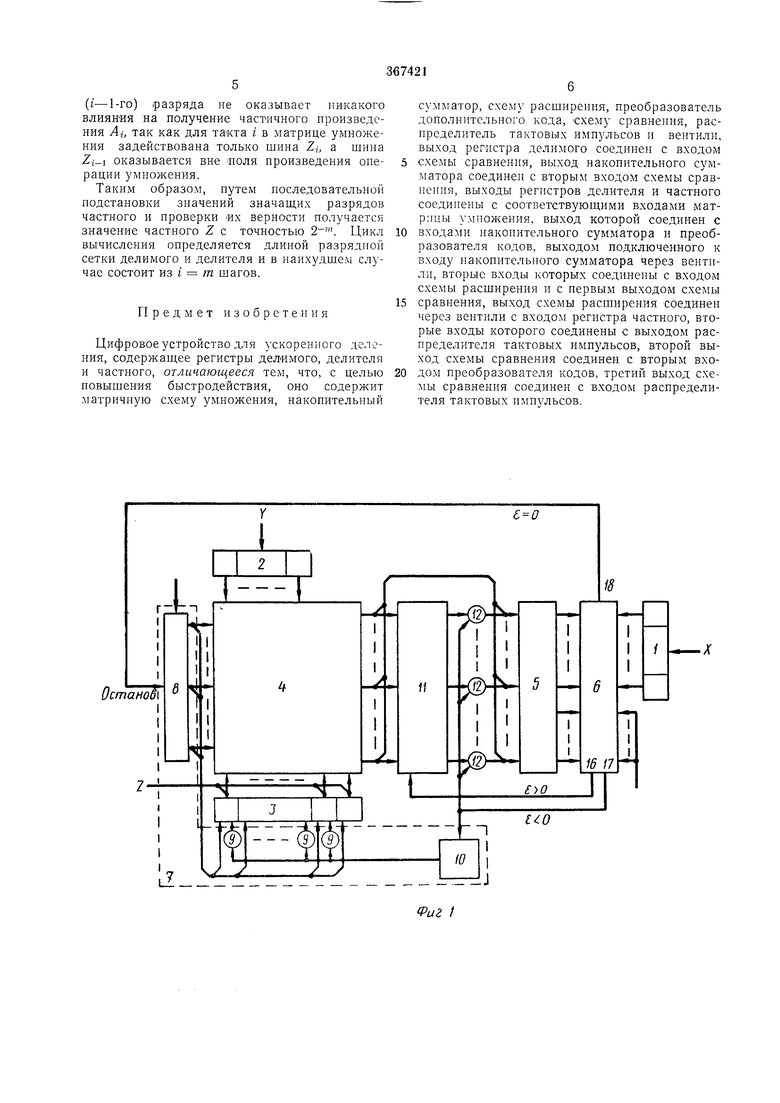

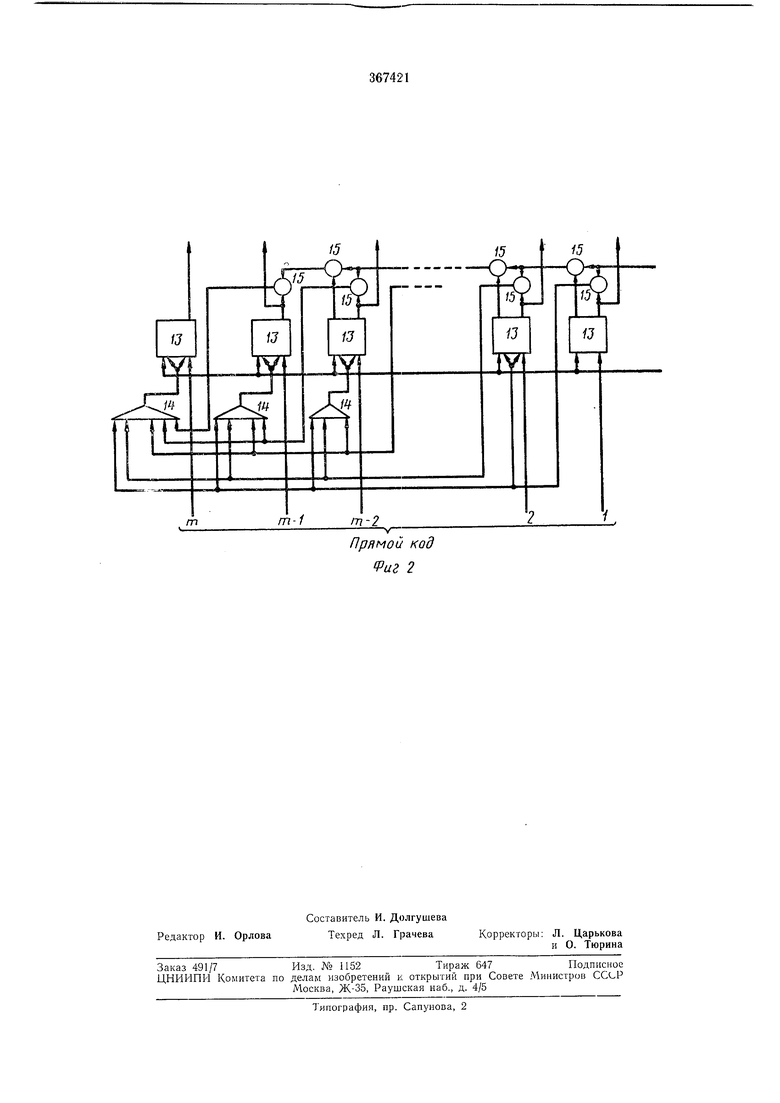

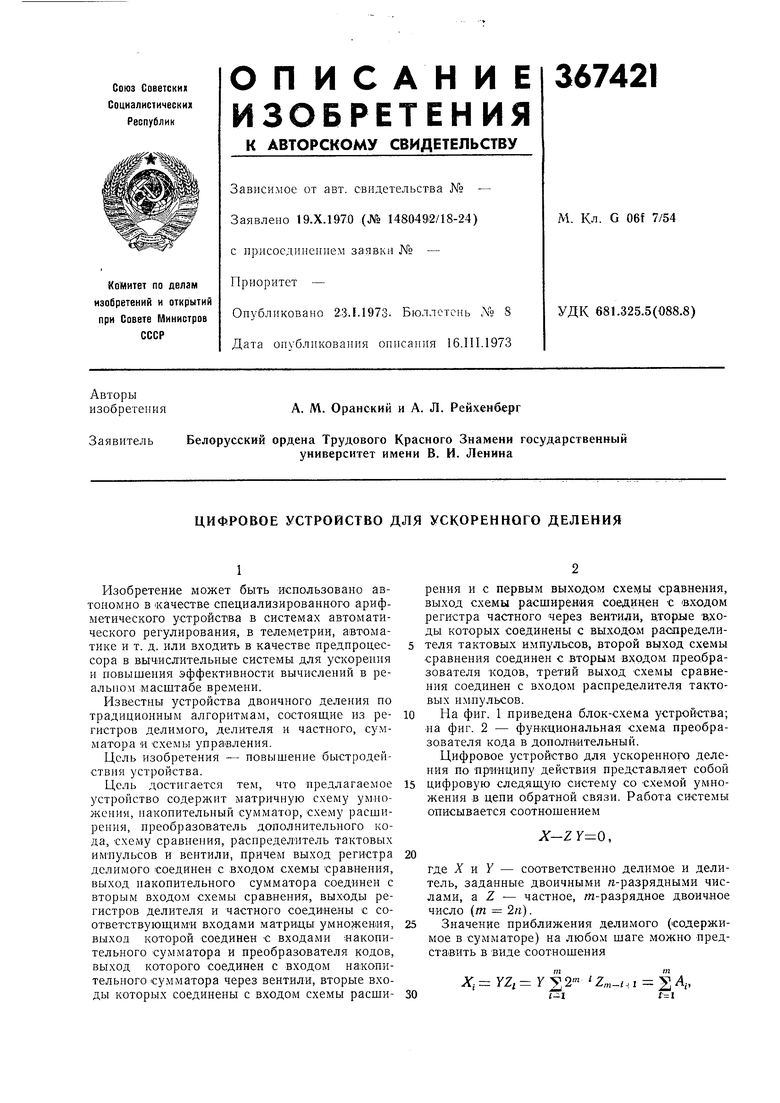

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - функциональная схема преобразо.вателя кода в дополнительный.

Цифровое устройство для ускоренного деления по принципу действия представляет собой

цифровую следяшую систему со схемой умножения в цепи обратной связи. Работа системы описывается соотношением

,

где J и У - соответственно делимое и делитель, заданные двоичными к-разрядными числами, а Z - частное, от-разрядное двоичное число (т 2rt).

Значение приближения делимого (содержимое в сумматоре) на любом шаге можно представить в виде соотношения

X, 2 Z,,,i, ,, i-i1 1 где ZOT-,--)- цифра i-ro разряда частного; Аг - частичное произведение на J-M шаге, Лг . На каждом шаге схема сравнения определяет знак разности между значением делимого X в регистре и содержимым сумматора, представляющим приближение Хг, согласно выражениюsign г, г sign X -f-1, если Sj О, О, если s. 0, - 1, если s.0, Предлагаемое устройство содержит входной регистр / делимого X; входной регистр 2 делителя ,У; .выходной регистр 3 частного Z; схему (матрица) 4 матричного умножения для получения частичных произведений сумматор 5 накопительного типа; схему 6 цифрового сравнения; схему 7 управления и подбора значений цифр частного; временной распределитель импульсов для импульсного питания матрицы умножения и последовательной записи значений цифр частного; группу 9 вентилей для записи очередной цифры -частного; схему 10 расширения; преобразователь 11 входного числа сумматора в дополнительный код; группу вентилей 12 для передачи в сумматор частичного произведения в дополнительном «оде. Преобразователь /У числа, подаваемого на сумматор, в дополнительный код состоит (фиг. 2) из статических триггеров 13, логических схем 14 разделения и группы вентилей 15 для передачи переносов. Схема 7 управления и подбора значений цифр частного обеспечивает при помош,и временного распределителя 5 импульсов импульсное питание схемы 4 матричного умножения разнесенными во времени тактовыми импульсами при одновременном подборе приближенных значений Z, на каждом шаге. Кроме того, эта схема вырабатывает исполнительные имлульсы (по сигналам со схемы 10 расширения импульсов), которые разрешают компенсацию неверно подобранных на предыдущем шаге значений при -помощи группы вентилей 9, и восстанавливает предыдущее значение содержимого в сумматоре. Работает устройство следующим образом. В исходном состоянии значение кодов X и Y записаны в соответствующие регистры. Все остальные регистры и сумматор находятся в нулевом состоянии. При подаче импульса запуска (начало вычисления) на распределитель 8 с последнего постуцает серия тактовых импульсов, сдвинутых во времени на величину TS. Каждый имлульс появляется только на определенной позиционной шине. Первый тактовый импульс обеспечивает получение значения первого Частичного произведения Ль Для этого в старшем разряде регистра 5 нервым тактовым импульсом устанавливается единица, этим же импульсом, задержанным на промежутоК т, несколько больший времени установления триггера, опрашивается схема 4. В результате умножения первое частное произведение Л Y-Zm поступает иараллельно на преобразователь 11 и на сумматор 5. Выходы последнего соединены со схемой 6 цифрового сравнения, на второй вход которой подается значение делимого X из регистра 1. Так. как длина разрядной сетки сумматора 5 в общем случае в два раза превышает разрядность регистра 1 (т 2п}, то на входы схел1Ы 6, находящиеся за пределадМИ разрядной сетки регистра /, подаются нулевые потенциалы. Если IB результате сравнения получают бг О, то появившийся на выходе 16 схемы 6 импульс устанавливает схему 11 в нулевое состояние. С приходом второго тактового импульса устанавливается единица в следующем Zm-i -м разряде регистра j и на выходе схемы 4 появляется следующее частичное произведение Лз Y-Zm-i которое суммируется с содержимым в сумматоре 5. Затем полученное новое значение .в сумматоре 5 сравнивается с Л . Если в результате сравнения получается значение &г С О, то на другом выходе 17 схемы 6 появляется импульс, по которому производятся суммирование значения Л2, хранимого в преобразователе 11 в дополнительном коде, с содержимым в сумматоре 5 (операция вычитания), а также запуск схемы 10 расширения с одним устойчивым состоянием, вырабатывающей имнульс длительностью 4 sИмпульс, вырабатываемый схемой 10, является разрешающим для группы вентилей 9. Следующий тактовый импульс (в данном случае в третьем такте по третьей группе шин). устанавливает единицу в Zm-z разряде регистра 3 и одновременно возвращает в нулевое состояние ячейку разряда Zm-i через соответствующий (открытый) вентиль группы 9. Операция вычитания значения Лг из содержимого сум.матора 5 осуществляется подачей на его вход через открытые вентили группы 12 значения Л; в дополнительном коде. Операция преобразования прямого кода в дополнительный производится с помощью триггеров /J и труппы вентилей 15. При этом дополнительный код представляет собою прямой код, инвертированный начиная после первой значащей цифры в младшем разряде. После окончания операции вычитания преобразователь // готов к выполнению следуюHtero шага. Процесс повторяется до появления последнего /п-го тактового импульса, который заносит единицу в последний младший разряд регистра 3. При равенстве Xi X и , т. е. в случае, когда делимое и делитель являются кратными величинами, на выходе 18 схемы 6 появляется сигнал, останавливающий распределитель 8, и процесс вычисления оканчивается. Одновременное появление единицы в i-м разряде и устранение ее из предыдущего

(i-1-го) разряда не оказывает никакого влияния на получение частичного произведения Ai, так как для такта / в матрице умножения задействована только шина Z,-, а шина Z, оказывается вне поля произведения операции умножения.

Таким образом, путем последовательной подстановки значений значащих разрядов частного и проверки -их верности получается значение частного Z с точностью 2-™. Цикл вычисления определяется длиной разрядной сетки делимого и делителя и в наихудшем случае состоит из i т шагов.

Предмет и з о б р е т е :Н и я

Цифровое устройство для ускоренного деления, содержащее регистры делимого, делителя и частного, отличающееся тСхМ, что, с целью повышения быстродействия, оно содержит матричную схему умножения, накопительный

сумматор, схему расширения, преобразователь дополнительного кода, схему сравнения, распределитель тактовых импульсов и вентили, выход регистра делимого соединен с входом 5 схемы сравнения, выход накопительного сумматора соединен с вторым входом схемы сравнения, выходы регистров делителя и частного соединены с соответствующими входами матрицы умножения, выход которой соединен с

0 входами накопительного сумматора и преобразователя кодов, выходом подключенного к входу накопительного сумматора через вентили, вторые входы которых соединены с входом схемы расширения и с первым выходом схемы

5 сравнения, выход схемы расширения соединен через вентили с входом регистра частного, вторые входы которого соединены с выходом распределителя тактовых импульсов, второй выход схемы сравнения соединен с вторым входом преобразователя кодов, третий выход схемы сравнения соединен с входом распределителя тактовых ИМПУЛЬСОВ.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU217718A1 |

| Генератор векторов для системы отображения графической информации | 1974 |

|

SU525980A1 |

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ И ДЕЛЕНИЯ | 1973 |

|

SU385273A1 |

| Устройство для деления | 1985 |

|

SU1357946A1 |

| Устройство для деления | 1991 |

|

SU1783523A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

Остано

Прямой код Риг 2

Авторы

Даты

1973-01-01—Публикация