Известны схемы быстродействующих сумматоров на феррит-диодных элементах последовательного и параллельного действия. Известна также схема параллельного сумматора на феррит-диодных элементах, в которой для построения одного разряда сумматора использованы два универсальных логических элемента и один простой.

Предложенный сумматор отличается от известного тем, что входы логического элемента разделения сигналов суммы и переноса соединены с выходами универсального логического элемента на три входа, причем выходы, соответствующие числам, содержащим по одной единице и по две единицы в разрядах, соответственно объединены. Это позволяет значительно упростить устройство.

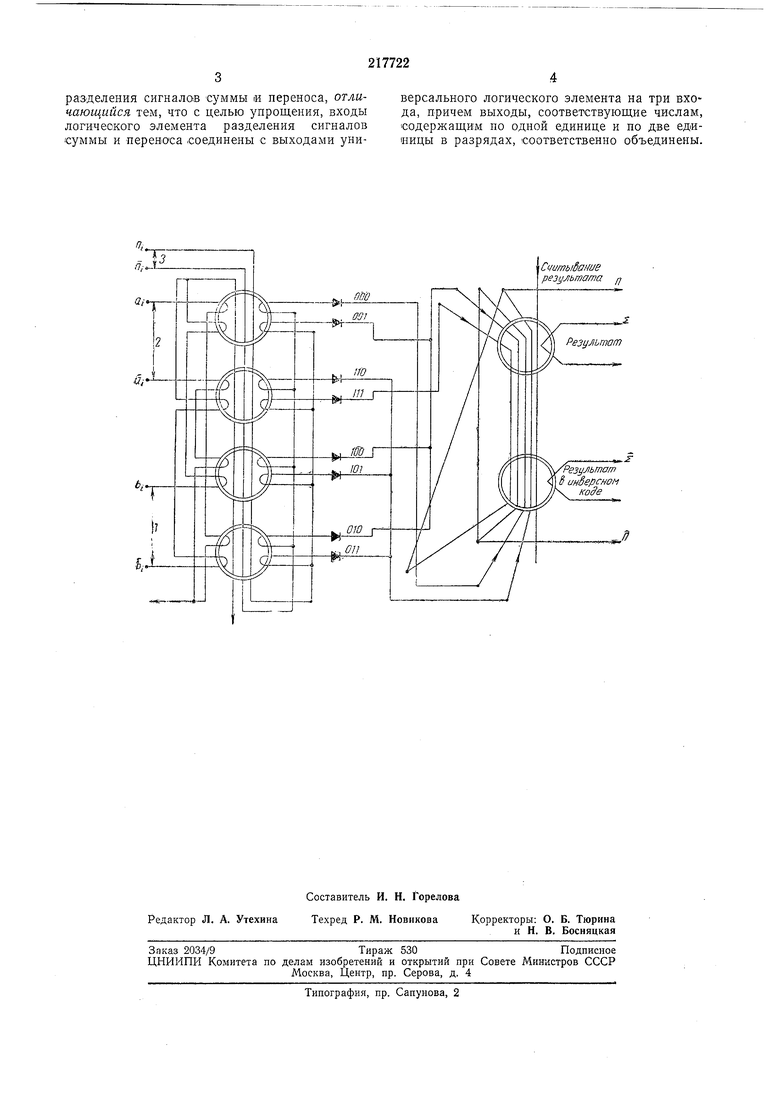

Для Построения одного разряда сумматора использован один универсальный элемент на три входа и один простой логический элемент разделения сигналов суммы и переноса.

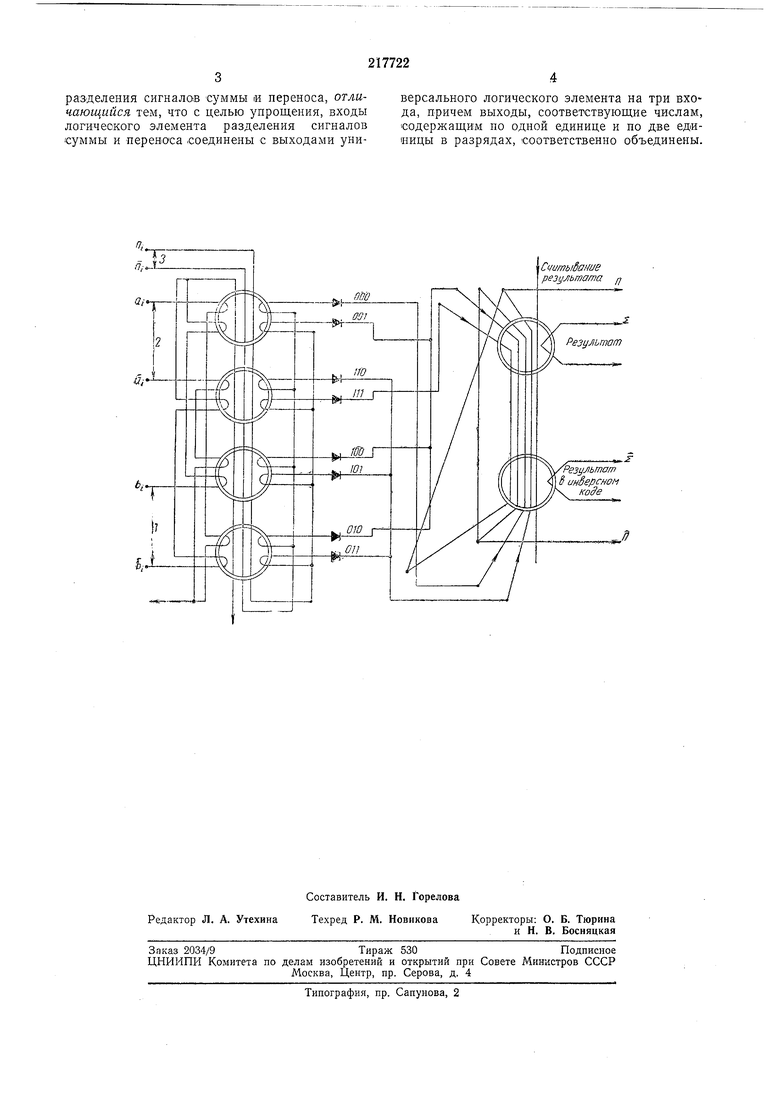

Схема одного разряда предложенного сумматора дана на чертеже.

Слагаемые а, Ь подаются на входы 1 и 2, а перенос П (сигнал считьБвания) - на вход 3. В зависимости от наличия или отсутствия переноса в предыдущем разряде возбуждается одна из шин считывания входа 3. Выходы универсального элемента соединены определенным образом и поступают на вход

простого логического элемента соответствующего разряда и далее на вход 3 универсального элемента следующего разряда.

Объединение выходных щин универсального элемента и последующая коммутация импульсов тока на соответствующие входы простого логического элемента выполнены согласно логике двоичного суммирования.

Наличие или отсутствие переноса из предыдущего разряда приводит к тому, что канальный имлульс тока поступает на ту или иную шину входа 3 элемента следующего разряда. Результат суммирования может быть считан в прямом или инверсном коде и по всем разрядам получен в течение одного периода работы элементов.

Все последующие разряды аналогичны f-му.

Схема является полностью феррит-диодной и имеет высокое быстродейств ие (лроверенная частота 0,5 ± 1 Мгц).

Предмет изобретения

разделения сигналов суммы и переноса, отличающийся тем, что с целью упрощения, входы логического элемента разделения сигналов суммы и переноса соединены с выходами унинереального логического элемента на три входа, причем выходы, соответствующие числам, содержащим по одной единице и по две единицы в разрядах, соответственно объединены.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФЕРРИТ-ДИОДНЫЙ СУММАТОР ПАРАЛЛЕЛЬНОГОДЕЙСТВИЯ | 1968 |

|

SU218519A1 |

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

| ФЕРРИТ-ДИОДНЫЙ СУММАТОР ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ | 1967 |

|

SU215610A1 |

| ДВУХРАЗРЯДНЫЙ КОМБИНАЦИОННЫЙ СУММАТОР | 1973 |

|

SU374600A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| ДВОИЧНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ СУММАТОР НА ФЕРРИТ-ДИОДНЫХ ЭЛЕМЕНТАХ | 1967 |

|

SU204685A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР НА ФЕРРИТ-ТРАНЗИСТОРНЫХ МОДУЛЯХ | 1970 |

|

SU277409A1 |

| Устройство для умножения матричного типа | 1980 |

|

SU935948A1 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| УНИВЕРСАЛЬНЫЙ ФЕРРИТ-ДИОДНЫЙ КОММУТАЦИОННЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1973 |

|

SU375793A1 |

Cijumb/SaHue результата fj

Результат

Результат

6 инберснон

Даты

1968-01-01—Публикация