(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ МАТРИЧНОГО

1

Изобретение относнтся к вычислитель ной технике и может быть использовано в быстродействующих арифметических устройствах различных цифровых малогабаритных комплексов, например, в устройствах цифровой фильтрации.

Известно матричное множительное уст ройство, содержащее две идентичные мат рицы умножения, подключенные ев ими выходами к первым входам двух сумматоров, две шины сомножителей, связанные через регистры и коммутаторы со входами матриц умножения. При этом матрица умножения с сук1матором, подключенным к ее выходу, офазует наращив ваемый матричный элемент, входом наращивания которого является второй вход сумматора, а выходом - выход сумматора. Выход первого наращиваемого матричного элемента соединен со входом второго наращиваемого элемента, выход которого подключен к выходу устройства. При построении умножителей большой разрядности наращиваемый матричный ТИПА

элемент может быть выполнен в виде наращиваемого модуля умножения Вследствие того, что быстродействие такого устройства, главным образом зависит от быстродействия выходных сумматсфовнаращиваемых матричных элементов, в нем обеспечивается высокое быстродей- ствие Lil

Недостатком такого устройства является больщой объем оборудования, обуоловленный наличием дополнительных регистров слов сомножителей, регистра сдвига, двух коммутаторов, регистра задержки..t

Известно матричное устройство для умножения и сложения, содержащее ыат . рицу сложения, которая содержит Yn-i У рааряаньк сумматоров, расположенных в Ы линейках матрицы (где М 7/ , а УУ1 - разрядность множителя), причем , ( У -2) старших выхода сумматоров млад,шей линейки соответственно соединены с

Р-вводами первой группы сумматоров 1 сродней линейки (), младшие выходь первого сумматора младшей линейки соединены соответственно с младшими входами первой группы, сумматора старшей линейки, 1И-2) старших входа первой группы которого соединены с соответствующими выходами первого сумматора средней линейки, выходы BTqDoro сумматора средней линейки соответственно соединены с входами второй груптты сумматора старшей линейки 2 . Недостатком известного устройства является его высокая сложность, обусловленная наличием большого числа двухвходовых вентилей. Цель изобретения - сокращение оборудования при сохранении быстродействия. Поставленная, цель достигается тем, что в устройство введены W групп двухвхоДовьЕХ элементов И-НЕ по И в каждой группе, (У1 -fW) элементов НЕ и (у1+П1)входово сумматор, причем первый вход -гоэлемен таИ-НЕ ( ,..., и I j 1..., JT) соединенс соотвествующим входом множимого устройства, вторые входы элементов И-НЕ каждой группы объединены и подключены к соответствующему входу множителя устройства, входы младших разрядов сумматоров матрицы сложения объединены и подключены к шине логический единицы входы первой группы сумматоров младшей линейки матрицы сложения соединены соответственно с вькодами элементов И-НЕ первых Vrv/3 групп, входы второй группы сумматоров средней линейки соединены с выходами элементов И-НЕ вторых Ш/З групп, выходы элементов Й-НЕ последних групп соединены соответственно со старшими входами сумматоров средней линейки матрицы сложения, выходы (и-1) младших элементов И-НЕ последних И/З групп соединены соответс гвенно с входами второй группы сумматоров младшей линейки, матрицы сложения, выходы сумматора старшей линейки и младшие выход второго. сумматора младшей линейки соот 5 ших

вественно соединены с входами элементов НЕ, выходы которых соединены соответственно с входами сумматора.

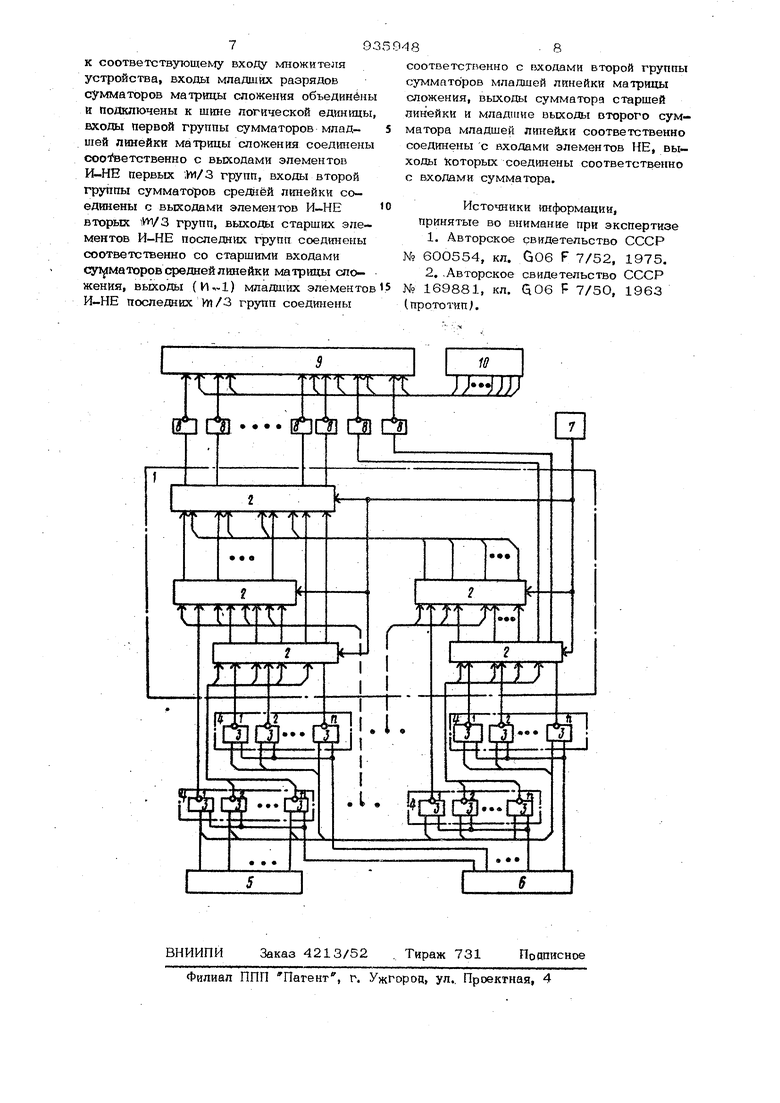

Сущность изобретения состоит в том, что в матрице сложения суммируют инверсии частичных произведений, предварительно сформированные с помощью элементов И-НЕ, ввводят в сумматоры матриц по1фавку, обеспечивающую формирование на ее выходе инверсии произведения обрабатываемой части сомножителей, инвертируют инверсию произведения и суммируют ее в (И ))- входовомсумсоединены соответственно со старшими входами сумматоров 2 средней линейки матрицы 1 сложения, выходы () , младших элементов 3 И-НЕ последних

Ш/З групп соединены соответственно с входами второй группъ сумматоров 2 младшей линейки матрицы 1 сложения, въхходы сумматора 2 старшей линейки и младшие выходы второго сумматора 2

младшей линейки соответственно соединены с входами элементов 8 НЕ, выходы которых соединенъ соответственно с входами сумматора 9, маторе с формируемым аналогично произведением другой части co r нoжитeлeй. На чертеже представлена структурная схема устройства. Устройство соде|э«ит матрицу 1 сложения, которая состоит из hi-l Я -разрядных сумматоров 2, элементы 3 И-НЕ, объединенных в Ж групп 4, вхоа S множимого, вход 6 множителя, шину 7 логической единицы, элементы 8 НЕ, ( и + И1)входовой сумматор 9. Для наращивания разрядности в устройстве предусмотрена шина Ю наращивания разрядности. I. , В устройстве (И-2) старших выходов сумматоров 2 младшей линейки соответственно соединены с р входами первой группы сумматоров 2 средней линейки ( младшие выходы первого сумматора 2 младшей линейки соединены соответственно- с младшими входа- ми первой группы сумматора 2 старшей линейки IVI -2) старших входа первой группы которого соединены с соответствующими въ1ходами первого сумма тора 2 средней линейки, выходы второго сумматора 2 средней линейки соответственно соединены с входами второй группы сумматора 2 старшей линейки, первый вход i/J -го элемента И-НЕ ( //,..., м i ,... hi ) соединен, с соответствующим входом 5 множимого устройства, вторые входы элементов 3 И-НЕ каждой группы объединены и подключены к соответствующему входу 6 множителя устройства, входы младших разрядов сумматоров 2 матрицы 1 сложения объединенъ и подключены к шине 7 логической единицы, входы первой группы сумматоров 2 младшей линейки матрицы 1 сложения соединены соответственно с выходами элементов 3. И-НЕ первых групп, входы второй группы сумматоров 2 средней линейки соединены с выходами элементов 3 И-НЕ вторых групп, выходы старэлементов 3 И-НЕ последних групп Устройство работает следующим образом. Сигналы множимого и миожятеля в прямом коде поступают соответственно через входы 5 и б на первые и вторые входы элементов 3 И-НЕ, Элементы 3 И-НЕ каждой группы 4 управляются разрядом множителя так, что число на выходе Последующей группы имеет вдвое больший вес, чем на выхода предыдущей Число на вьрсоДе группы 4 представляет собой инверсию частичного произведения множимого на соответствующий разряд множителя. Обозначив множимое через X, а мно житель через У, и используя двоичире представление чисел, записывают И -раз рядное число X и Vn -разрядное число У В виде Х--.Х,2 . , V -- 5i ; 1 , где X, У - значение I -X разрядов чисел X и У. Инверсия частичного произведения на выходе |-ой группы элементов 3 И-НЕ с учетом веса разряда множителя равна - .-i-f , A,-XV,1 где А - И ,- разрядное частичное про изведение ( , 2,... ГЛ ) Учитывая, что инверсшо (обратный хо некоторого И -разрядного числа В можно записать в виде , представляю инверсии частичных произведений А следующим образом: A,--xv-,,a-2; К.-- г --г - г2, .Л 5 -7 o -JoM-vw- vj 2 :ow V« VYСумма частичных произведений 13) представляет собой М +т разрядное число которое с учетом выражения (1) может быть представлено в виде C--2L - X5-r-(2 2... 2.)(Ч Для получения инверсии произведения ХУ необходимо в выражении (4) компенсировать выражения в скобках. Для этого на входы переносов младших разрядов сумматоров 2 матрицы 1 сложения подаю компенсирующий сигнал поправки от шины 7 логической единицы. Образовавшийся на выходе матрицы 1 сложения инверсный код произведения инвертируется элементами 8 НЕ. С выхода элементов 8 НЕ про нзведения обрабатываемых разрядов сомножителей поступает на первые входь (VI + )-входового сумматора 9, на вторые входы которого одновременно от шины Ю наращивания разрядности поступает произведение Другой части сомножителей. После сумк1ированпя на выходах ; сумматора 9 сжазывается сформированным полное произведение сомножителей. При построении многоразрядных множительных устройств такого типа в отличие от из вестного, сигналы переноса распрост раняются одновременно и независимо во всех устройствах, вследствие чего быстродействие всего устройства опреДе ляется быстродействием одного устрой.ства. Поэтому при увеличении разрядности сомножителей для сохранения высокого быстродействия не приходится увеличивать быстродействие сумматоров матрицы сложения, КПК в известном, что позволяет уюпользовать в матрице простые сумматоры, и следовательно, упростить устройство в целом без снижения быстродействия, Форм у л а и-3 обретения Устройство для умножения матричного типа, содержащее матр1щу сложения, которая содержит Wv-l И-разрядных сумматоров, расположенных в Ы линейках матрицы (где N7/ , а - разрядаость. множителя), причем () старшие выходы сумматоров младшей линейки соответственно соединены с р входами первой группы сумматоров средней линейки (где ), младшие выходы первого сумматора младшей линейки соединены соответственно с младшими входами первой группы сумматорт старшей линей- ки, СИ-2) старших входа первой группы которого соединены с соответствующими вьрсоДйми первого сзумматора средней л нейки, выходы второго сумматора cpeft ней линейки Соответственно соединены с входами второй гру;ппы сумматора старшей линейки, отличающееся тем, что, с целью сокращения оборудрвания при сохранении быстродействия, в него введены J rRrnn двухвходовых элементов И-НЕ по И в каждой группвг (У +У) элементов НЕ и (п +111)-вхоДовЬй сумматор, причем первый вход lY-ro элемента И-НЕ ( ,..., Vi , ...t /т) соединен с соответствующим входом МНОЖИМОГО устройства, вторью входы элементов И-НЕ каждой группы o6beMBHCTtr. 70 к соответствующему входу множителя устройства, входы младших разрядов сумматоров матрицы сложения объединены и подключены к шине логической единицы входы первой группы сумматоров младшей линейки матрицы сложения соединены сооЛзетственно с выходами элементов И-НЕ первых ,Уи/3 групп, входы второй группы сумматоров средней линейки соединены с выходами элементов И-НЕ вторых VH/3 групп, выходы старших элементов И-НЕ последн{1х групп соединены соответственно со старшими входами cyi MaTopoB средней л ииейки матрицы сложения, вьйоды (И,-1) младших элементо И-НЕ последних УМ/3 групп соеди 1ены 18 соответственно с Е5ходами второй группы сумматоров младшей линейки матрицы сложения, выходы сумматора старшей линейки и младшие выходы второго сумматора младшей линейди соответственно соединены с входами элементов НЕ, выходы icoTopbtx соединены соответственно с входами сумматора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 600554, кл. G06 F 7/52, 1975. 2..Авторское свидетельство СССР № 169881, кл. (дОб F 7/50, 1963 (прототипh

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное множительное устройство | 1980 |

|

SU942003A1 |

| Устройство для умножения | 1981 |

|

SU1019442A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для умножения | 1988 |

|

SU1529216A1 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| Устройство для умножения двух @ -разрядных чисел | 1988 |

|

SU1575174A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Матричное устройство для умножения | 1979 |

|

SU842800A1 |

| Матричное множительное устройство | 1984 |

|

SU1170450A1 |

Авторы

Даты

1982-06-15—Публикация

1980-09-15—Подача