Известны множительные устройства, содержащие запоминающее устройство, схему выдачи адресов запоминающего устройства, регистр первого сомножителя, регистр второго сомножителя и схему приема результата.

Предлагаемое устройство отличается от известных тем, что единичные выходы усилителей считывания разрядов с первого по седьмой запоминающего устройства соединены соответственно с первыми входами клапанов приема в первый, второй, третий и четвертый разряды регистра первого сомножителя и первый, второй, третий разряды регистра второго сомножителя. Вторые входы клапанов приема связаны с выходом источника сигнала разрешения приема в устройстве управления, выходы клапанов приема регистра первого сомножителя соединены с соответствующими единичными входами регистра первого сомножителя, а выходы клапанов приема в первый, второй и третий разряды регистра второго сомножителя подключены соответственно к единичным входам первого, второго и третьего разрядов регистра второго сомножителя. Единичные выходы триггеров разрядов с первого по четвертый регистров первого и второго сомножителей соединены со входами схемы выдачи адресов, выходы которой связаны со входами схемы возбуждения адресов запоминающего устройства. Единичные выходы триггеров первого и четвертого разрядов регистров первого и второго сомножителей подсоединены ко входам схемы совпадения, выход которой через схему отрицания соединен с первым входом схемы совпадения, а выход схемы совпадения связан со стробирующим входом схемы выдачи адресов и через первый элемент задержки - с нулевыми входами первого, второго, третьего разрядов регистра первого сомножителя и второго, третьего и четвертого разрядов регистра второго сомножителя. Второй вход схемы совпадения подключен к источнику сигнала запуска множительного устройства и через второй элемент задержки - с нулевыми входами триггеров четвертого разряда регистра первого сомножителя и первого разряда регистра второго сомножителя.

Такое выполнение устройства позволяет сократить затраты на оборудование, а также повысить быстродействие устройства.

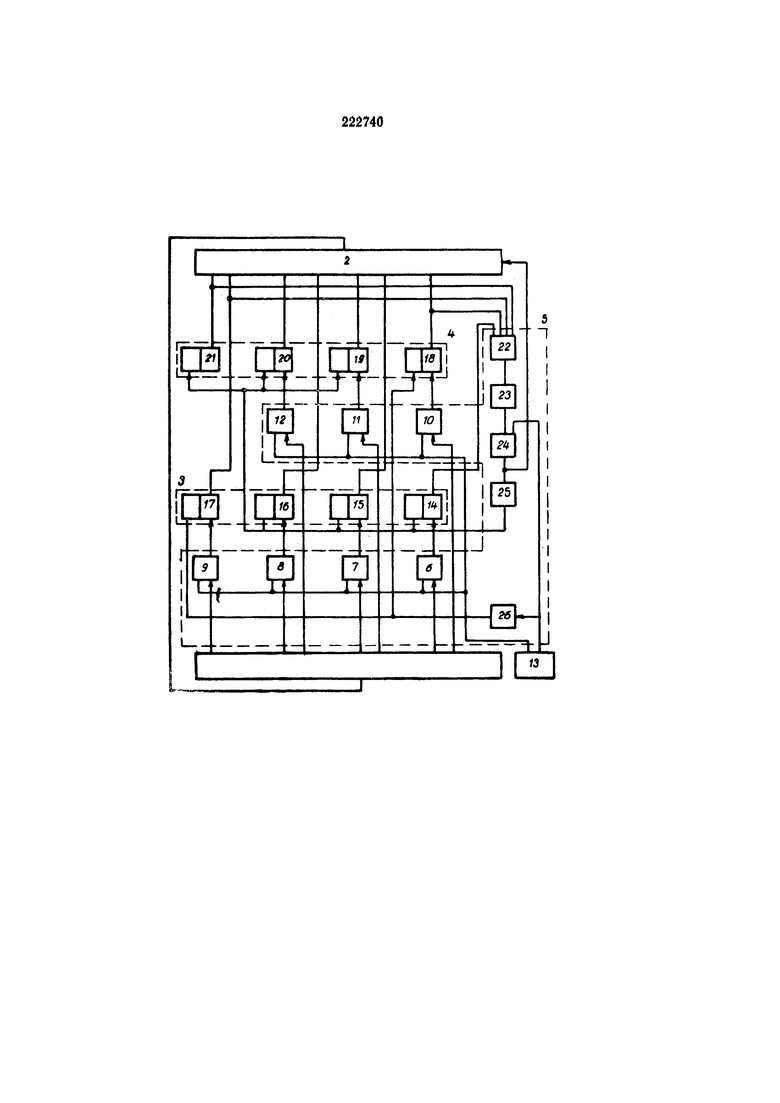

На чертеже представлена схема множительного устройства.

В известных машинах, оперирующих с семибитными символами, результат перемножения двух десятичных разрядов записывается в двух символах, так как при перемножении 9×9 результат равен 81 и для его представления в коде 8421 требуется восемь битов (10000001). Один десятичный разряд результата записывается в одном символе, другой - в другом символе.

Результаты перемножения двух десятичных разрядов занимают, таким образом, 200 символов, т.е. 200 ячеек запоминающего устройства. Для выборки результата требуется как правило два обращения к запоминающему устройству (за младшим, а затем за старшим символами результаты или наоборот).

Предлагаемое множительное устройство отличается от известных тем, что оно имеет специальную схему приема результата, позволяющую сократить размер таблицы умножения до 99 ячеек запоминающего устройства.

В каждой ячейке хранится результат от перемножения соответствующей пары сомножителей, за исключением пары 9×9, результат перемножения которой получается аппаратурным способом. Символ произведения, выбираемый из таблицы, имеет, например, при перемножении 8×9, следующий вид: 1110010, где 0010, (2) - младший десятичный разряд произведения; 111, (7) - старший десятичный разряд произведения.

Перед приемом результата из таблицы регистры сомножителей гасятся. Результат перемножения, прочитанный из таблиц, принимается в регистры сомножителей. Если перемножаются цифры 9×9, то блокируется обращение к таблице умножения и гашение первого второго и третьего разрядов регистра первого сомножителя, второго, третьего и четвертого разрядов регистров второго сомножителя. Так как в этих регистрах при умножении 9×9 содержались коды 1001 и 1001, то после гашения первого разряда регистра второго сомножителя и четвертого разряда регистра первого сомножителя регистры содержат коды 1000 и 0001, т.е. код 81.

Множительное устройство содержит запоминающее устройство 1, схему 2 выдачи адресов запоминающего устройства, регистр 3 первого сомножителя, регистр 4 второго сомножителя и схему 5 приема результата.

Единичные выходы усилителей считывания первого - седьмого разрядов запоминающего устройства соединены соответственно с первыми входами клапанов (схем «И») 6, 7, 8, 9 приема в первый, второй, третий и четвертый разряды регистра 3 и клапанов (схем «И») 10, 11, 12 приема в первый, второй и третий разряды регистра 4. Вторые входы клапанов 6-12 соединены с выходом источника сигнала разрешения приема в устройстве 13 управления. Выходы клапанов 6-12 соединены соответственно с единичными входами триггеров 14-17 регистра 3 и триггеров 18-20 регистра 4.

Единичные выходы триггеров 14-17 регистра 5 и триггеров 18-21 регистра 4 соединены со входами схемы «И» 22, выход которой через схему «НЕ» 23 соединен с входом схемы «И» 24. Выход схемы «И» 24 соединен со стробирующим входом схемы выдачи адресов и через элемент 25 задержки гашения - с нулевыми входами триггеров 14, 15, 16 регистра 3 и триггеров 19, 20, 21 регистра 4. Второй вход схемы «И» 24 соединен с источником сигнала запуска множительного устройства, находящимся в устройстве 13 управления, и входом элемента 26 задержки гашения, выход которого соединен с нулевыми входами триггеров 17 и 18.

Операнды, участвующие в операции, находятся в регистре 3 и в регистре 4.

Сигнал запуска множительного устройства из устройства 13 управления поступает на вход схемы «И» 24. Если выполняется умножение 9×9, то импульс запуска через схему «И» 24 не проходит.

Запрещающий сигнал на схему «И» 24 поступает через схему «НЕ» 23 с выхода схемы «И» 22, анализирующей значение операндов в регистрах первого и второго сомножителей. Если в указанных регистрах не находится одновременно код 9, то сигнал с выхода схемы «И» 24 поступает в схему 2, которая выдает адрес для обращения к таблице умножения. Одновременно сигнал с выхода схемы «И» 24 поступает через элемент 25 задержки на нулевые входы триггеров 14, 15, 16 регистра 3 и триггеров 18, 19, 20 регистра. 4.

На нулевые входы триггера 17 регистра 3 и триггера 18 регистра 4 поступает сигнал запуска множительного устройства из устройства управления, задержанный на элементе 26 задержки. Величина задержки элементов 25, 26 определяется временем, необходимым для срабатывания схемы выдачи адресов. Таким образом, при перемножении любых сомножителей, за исключением 9×9, производится сброс триггеров 18-21 и 14-17 регистров операндов. На единичные входы триггеров 14-17 регистра первого сомножителя поступают соответственно через схемы «И» 6, 7, 8, 9 сигналы с единичных выходов усилителей считывания первого-четвертого разрядов запоминающего устройства, а на единичные входы триггеров 18, 19, 20 регистра второго сомножителя поступают соответственно через схемы «И» 10-12 сигналы с выходов усилителей считывания пятого-седьмого разрядов запоминающего устройства.

Информация, считанная из таблиц, поступает на вход указанных триггеров при наличии на схемах «И» 6-12 сигнала, разрешающего прием и вырабатываемого в устройстве управления.

После завершения приема в регистре второго сомножителя находится разряд произведения, а в регистре первого сомножителя - младший разряд произведения. Если производится умножение 9×9, то сигнал с выхода схемы «НЕ» 23 запрещает прохождение сигнала запуска множительного устройства через схему «И» 24, в результате чего не вырабатывается сигнал опроса схемы выдачи адресов, т.е. не производится обращение к запоминающему устройству.

Так как сигнал на выходе схемы «И» 24 не появляется, то сброса триггеров 14-16 и 19-21 не происходит. Импульс запуска множительного устройства через элемент 26 задержки сбрасывает триггеры 17 и 18. В регистре первого сомножителя остается в единичном состоянии триггер 14, а в регистре второго сомножителя - триггер 21, что и соответствует результату выполнения умножения 9×9.

Таким образом, новизной предлагаемого устройства является наличие схемы 5 приема, позволяющей сократить объем запоминающего устройства для хранения таблиц и получать результат операции за одно обращение к запоминающему устройству.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для МОДИФИКАЦИИ АДРЕСОВ | 1969 |

|

SU249057A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Устройство для умножения | 1985 |

|

SU1305667A1 |

| Устройство для вычисления суммы произведений двух массивов чисел | 1980 |

|

SU985782A1 |

| Устройство для дифференцирования частоты повторения импульсов | 1974 |

|

SU525117A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| ТАБЛИЧНОЕ СУММИРУЮЩЕ-МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU253442A1 |

| Частотно-импульсное множительно-делительное устройство | 1975 |

|

SU556437A1 |

| Устройство для контроля электропотребления | 1988 |

|

SU1566371A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

Множительное устройство, содержащее запоминающее устройство, схему выдачи адресов запоминающего устройства, регистр первого сомножителя, регистр второго сомножителя и схему приема результата, отличающееся тем, что, с целью сокращения оборудования, увеличения быстродействия, единичные выходы усилителей считывания разрядов с первого по седьмой запоминающего устройства соединены соответственно с первыми входами клапанов приема в первый, второй, третий и четвертый разряды регистра первого сомножителя и первый, второй, третий разряды регистра второго сомножителя, вторые входы клапанов приема связаны с выходом источника сигнала разрешения приема в устройстве управления, выходы клапанов приема регистра первого сомножителя соединены с соответствующими единичными входами регистра первого сомножителя, а выходы клапанов приема в первый, второй и третий разряды регистра второго сомножителя подключены соответственно к единичным входам первого, второго и третьего разрядов регистра второго сомножителя единичные выходы триггеров разрядов с первого по четвертый регистров первого и второго сомножителей соединены со входами схемы выдачи адресов, выходы которой связаны со входами схемы возбуждения адресов запоминающего устройства, единичные выходы триггеров первого и четвертого разрядов регистров первого и второго сомножителей подсоединены ко входам схемы совпадения, выход которой через схему отрицания соединен с первым входом схемы совпадения, выход которой связан со стробирующим входом схемы выдачи адресов и через первый элемент задержки - с нулевыми входами первого, второго, третьего разрядов регистра первого сомножителя и второго, третьего и четвертого разрядов регистра второго сомножителя, второй вход схемы совпадения подключен к источнику сигнала запуска множительного устройства и через второй элемент задержки - с нулевыми входами триггеров четвертого разряда регистра первого сомножителя и первого разряда регистра второго сомножителя.

Авторы

Даты

1968-12-12—Публикация

1967-03-06—Подача