Известны устройства для модификации адресов цифровой вычислительной машины, содержащие регистр, устройство управления, триггеры, формирователи потенциалов и логические схемы.

Известные устройства не позволяют выполнять операцию умножения способом, требующим небольшого количества оборудования без увеличения времени на выполнение операции.

Предлагаемое устройство аналогичного назначения отличается тем, что, с целью его упрощения и повышения быстродействия, в нем формирователь потенциала выборки первого операнда устройства управления подключен ко входам первой и второй схем «И, формирователь потенциала выборки второго операнда подключен ко входам третьей и четвертой схем «И. Единичный выход триггера нечетного разряда произведения соединен с другими входами второй и третьей схем «И, а его нулевой выход-со входами первой и четвертой схем «И. Выходы первой и третьей схем «И через потенциальную схему «ИЛИ подключены .ко входам пятой, шестой и седьмой схем «И, выход формирователя такта коррекции устройства управления и выход формирователя такта восстановления устройства управления соединены соответственно со входами пятой и седьмой схем «И и через другую (Потенциальную схему «ИЛИ и схему

«НЕ - с другими входами второй, четвертой и шестой схем «И. Единичный выход усилителя считывания запоминающего устройства цифровой вычислительной машины соединен с импульсными входами первого и второго клапанов и со входом первой импульсной схемы «ИЛИ, н левой выход усилителя соединен с импульсными входами третьего, четвертого и пятого клапанов и со входами первой и второй импульсных схем «ИЛИ. формирователя потенциалов первого цикла устройства управления нодключен к потгнциальному входу первого клапана, выход которого соединен со входом второй импульсной схемы «ИЛИ, выходы импульсных схем «ИЛИ соединены соответственно с импульсными входами шестого и седьмого клапанов. Иотенциальные входы второго, третьего, четвертого, пятого, шестого и седьмого клапанов соединены соответственно с выходами седьмой, второй, четвертой, пятой и шестой схем «И. Выход формирователя потенциала такта записи результата устройства управления соединен с потенциальным входом пятого клапана, выход которого подключен к счетному входу триггера нечетного разряда произведения и входу третьей импульсной схемы «ИЛИ, другие входы которой соединены с выходами второго, третьего и четвертого клапанов, выходы шестого, седьмого клананов и третьей импульсной схемы «ИЛИ соединены соответственно со входамн по «-2, по «-|-1 и по «-1 регистра адреса оперативного запоминающего устройства.

Устройство выполняет модификацию адресов сомножителей и произведения.

Перемножаемые числа могут быть представлены в позиционной двоично-кодированной системе счисления с произвольным основанием, кроме основания 2. Разрядность сомножителей может быть произвольной.

Работа схемы блока описана применительно к десятичной системе счисления.

Умножение выполняется по способу последовательного получения разрядов произведения, начиная с младшего. Каждый сомножитель ограничен слева и справа. Границей слева служит единица в специальном двоичном разряде старшей цифры числа. Границей справа служит единица в том же разряде, находящаяся в цифре по адресу А -|-1, где А- адрес младшей цифры числа. Старший разряд числа находится по адресу А -п, где п-количество разрядов в числе.

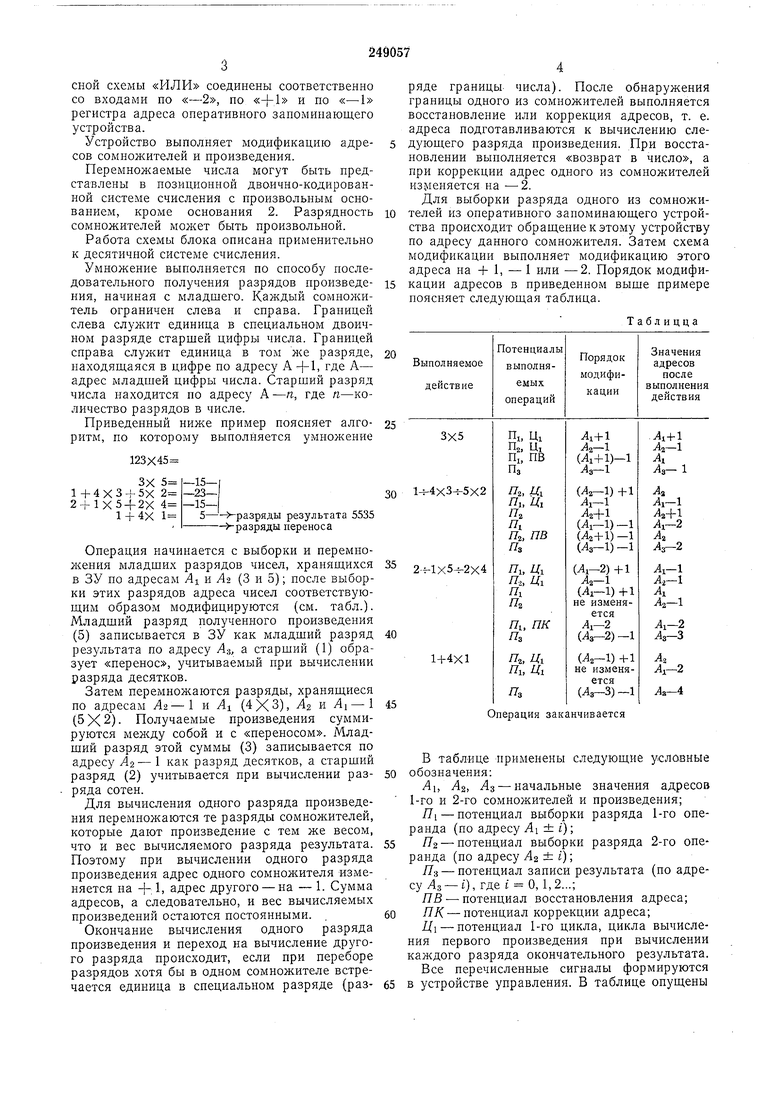

Приведенный ниже пример поясняет алгоритм, по которому выполняется умножение 123X45 1+4ХЗ + 5Х 2 2 + lX5-f2X 4 5Х-разряды результата 5535 1 + 4Х 1 -разряды переноса Операция начинается с выборки и перемножения младших разрядов чисел, хранящихся в ЗУ по адресам AI и Ла (3 и 5); после выборки этих разрядов адреса чисел соответствующим образом модифицируются (см. табл.). Младщий разряд полученного произведения (5) записывается в ЗУ как младший разряд результата по адресу AS, а старший (1) образует «перенос, учитываемый при вычислении разряда десятков. Затем перемножаются разряды, хранящиеся по адресам Л2-1 и Л1 (4X3), Лг и Л; - 1 (5X2). Получаемые произведения суммируются между собой и с «переносом. Младший разряд этой суммы (3) записывается по адресу AZ- 1 как разряд десятков, а старший разряд (2) учитывается при вычислении разряда сотен. Для вычис.1ения одного разряда произведения перемножаются те разряды сомножителей, которые дают произведение с тем же весом, что и вес вычисляемого разряда результата. Поэтому при вычислении одного разряда произведения адрес одного сомножителя изменяется на -4-;1, адрес другого - на - 1. Сумма адресов, а следовательно, и вес вычисляемых произведений остаются постоянными. . Окончание вычисления одного разряда произведения и переход на вычисление другого разряда происходит, если при переборе разрядов хотя бы в одном сомножителе встречается единица в специальном разряде (разряде границы числа). После обнаружения границы одного из сомножителей выполняется восстановление или коррекция адресов, т. е. адреса подготавливаются к вычислению следующего разряда произведения. При восстановлении выполняется «возврат в число, а при коррекции адрес одного из сомножителей изменяется на -2.

Для выборки разряда одного из сомножителей из оперативного запоминающего устройства происходит обращение к этому устройству по адресу данного сомножителя. Затем схема модификации выполняет модификацию этого адреса на -t- 1, - 1 или -2. Порядок модификации адресов в приведенном выше примере поясняет следующая таблица.

Таблицца Операция заканчивается В таблице применены следующие услоаные означения: Ль Ла, АЗ - начальные значения адресов го и 2-го сомножителей и произведения; HI - потенциал выборки разряда 1-го опенда (по адресу AI ± i); Яг - потенциал выборки разряда 2-го опенда (но адресу Ла ± i), Яз - потенциал записи результата (по адреAz i), где i О, 1,2...; ЯВ -потенциал восстановления адреса; ПК - потенциал коррекции адреса; Ifi - потенциал 1-го цикла, цикла вычислея первого произведения при вычислении ждого разряда окончательного результата.

потенциалы, по которым выполняется вычисление произведений и сумм. В этих действиях модификация адресов AI, А, АЗ не выполняется.

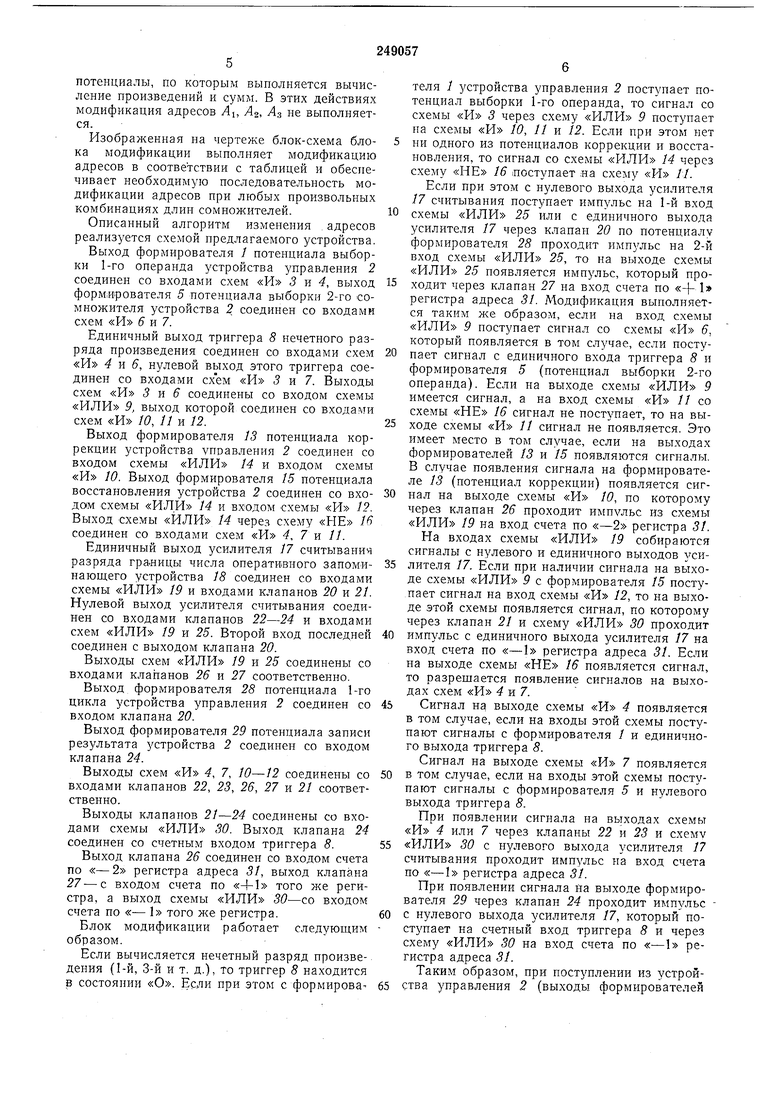

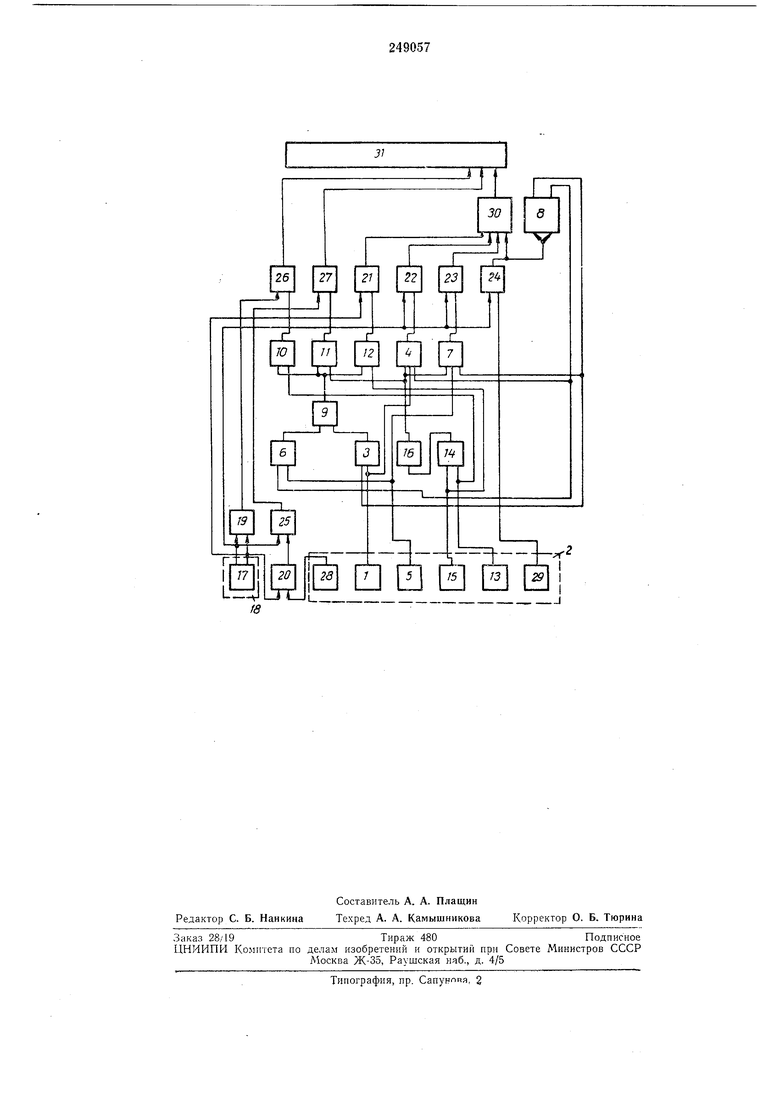

Изображенная на чертеже блок-схема блока модификации выполняет модификацию адресов в соответствии с таблицей и обеспечивает необходимую последовательность модификации адресов при любых произвольных комбинациях длин сомнолсителей.

Описанный алгоритм изменения .адресов реализуется схемой предлагаемого устройства.

Выход формирователя / потенциала выборки 1-го операнда устройства управления 2 соединен со входами схем «И 3 и 4, выход форМ|Ирователя 5 потенциала выборки 2-го сомножителя устройства 2 соединен со входами схем «И 5 и 7.

Единичный выход триггера 8 нечетного разряда произведения соединен со входами схем «И 4 и 6, нулевой выход этого триггера соединен со входами схем «И 5 и 7. Выходы схем «И 5 и б соединены со входом схемы «ИЛИ Я выход которой соединен со входами схем «И W, 11 и 12.

Выход формирователя 13 потенциала коррекции устройства управления 2 соединен со входом схемы «ИЛИ 14 и входом схемы «И 10. Выход формирователя 15 потенциала восстановления устройства 2 соединен со входом схемы «ИЛИ 14 и входом схемы «И 12. Выход схемы «ИЛИ 14 через схему «ИЕ 16 соединен со входами схем «И 4, 7 и //.

Единичный выход усилителя /7 считывания разряда градицы числа оперативного запоминаюодего устройства /5 соединен со входами схемы «ИЛИ 19 и входами клапанов 20 и 21. Нулевой выход усилителя считывания соединен со входами клапанов 22-24 и входами схем «ИЛИ 19 и 25. Второй вход последней соединен с выходом клапана 20.

Выходы схем «ИЛИ 19 и 25 соединены со входами клапанов 26 и 27 соответственно.

Выход формирователя 28 потенциала 1-го цикла устройства управления 2 соединен со входом клапана 20.

Выход формирователя 29 потенциала записи результата устройства 2 соединен со входом клапана 24.

Выходы схем «И 4, 7, 10-12 соединены со входами клапанов 22, 23, 26, 27 и 21 соответственно.

Выходы клапапов 21-24 соединены со входами схемы «ИЛИ SO. Выход клапана 24 соединен со счетным входом триггера 8.

Выход клапана 26 соединен со входом счета по «-2 регистра адреса 31, выход клапэ.на 27 - с входом счета по «+1 того же регистра, а выход схемы «ИЛИ ВО-со входом счета по «- 1 того же регистра.

Блок модификации работает следующим образом.

теля 1 устройства управления 2 поступает потенциал выборки 1-го операнда, то сигнал со схемы «И 5 через схему «ИЛИ 9 поступает на схемы «И 10, 11 и 12. Если при этом нет ни одного из потенциалов коррекции и восстановления, то сигнал со схемы «ИЛИ 14 через схему «ИЕ 16 поступает иа схему «И //.

Если при этом с нулевого выхода усилителя 17 считывания поступает импульс на 1-й вход схемы «ИЛИ 25 или с единичного выхода усилителя 17 через клапан 20 по потенциалу формирователя 28 проходит импульс на 2-й вход схемы «ИЛИ 25, то на выходе схемы «ИЛИ 25 появляется импульс, который проходит через клапан 27 на вход счета по «-f- 1 регистра адреса 31. Модификация выполняется таким ж& образом, если на вход схемы «ИЛИ 9 поступает сигнал со схемы «И 6, который появляется в том случае, если поступает сигнал с единичного входа триггера 5 и формирователя 5 (потенциал выборки 2-го операнда). Если па выходе схемы «ИЛИ 9 имеется сигнал, а на вход схемы «И // со схемы «НЕ 16 сигнал не поступает, то на выходе схемы «И 11 сигнал не появляется. Это имеет место в том случае, если на выходах формирователей 13 и 15 появляются сигналы, В случае появления сигнала на формирователе 13 (потенциал коррекции) появляется сигнал на выходе схемы «И 10, по которому через клапан 26 проходит импульс из схемы «ИЛИ 19 на вход счета по «-2 регистра 31.

На входах схемы «ИЛИ 19 собираются сигналы с нулевого и единичного выходов усилителя 17. Если при наличии сигнала на выходе схемы «ИЛИ 9 с формирователя 15 поступает сигнал на вход схемы «И 12, то на выходе этой схемы появляется сигнал, по которому через клапан 21 и схему «ИЛИ 30 проходит импульс с единичного выхода усилителя 17 на вход счета по «-1 регистра адреса 31. Если на выходе схемы «НЕ 16 появляется сигнал, то разрешается появление сигналов на выходах схем «И и 7.

Сигнал на выходе схемы «И 4 появляется в том случае, если на входы этой схемы поступают сигналы с формирователя / и единичного выхода триггера 8.

Сигнал на выходе схемы «И 7 появляется в том случае, если на входы этой схемы поступают сигналы с формирователя 5 и нулевого выхода триггера 8.

При появлении сигнала на выходах схемы «И 4 или 7 через клапаны 22 и 23 и схему «ИЛИ 30 с нулевого выхода усилителя 17 считывания проходит импульс на вход счета по «-1 регистра адреса 31.

Ири появлении сигнала на выходе формирователя 29 через клапан 24 проходит импульс с нулевого выхода усилителя 17, который поступает на счетный вход триггера 8 и через схему «ИЛИ 30 на вход счета по «-1 регистра адреса 31.

/, 5, 13, 15, 28 и 29) управляющих сигналов в определенной последовательности .блок модификации адреса выдает на счетные входы регистра адреса 31 сигналы модификации в той последовательности, которая задается описанным выше алгоритмом. В регистр 3/ попеременно по потенциалам формирователей /, 5, 29 засылаются адреса Ль Лг, Лд для выполнения модификации. Хранятся эти адреса в специальных регистрах.

Предмет изобретения

Устройство для модификации . адресов множительного устройства цифровой вычислительной машины, содержащее регистр, устройство управления, триггеры, формирователи потенциалов и логические схемы, отличающееся тем, что, с целью упрощения и повышения быстродействия, в нем формирователь потенциала выборки первого операнда устройства управления подключен ко входам первой и второй схем «И, формирователь потенциала выборки второго операнда подключен ко входам третьей и четвертой схем «И, единичный выход триггера нечетного разряда произведения соединен с другими входами второй и третьей схем «И, а его нулевой выход-со входами первой и четвертой схем «И, выходы первой и третьей схем «И через потенциальную схему «ИЛИ подключены ко входам пятой, шестой и седьмой схем «И, выход формирователя такта коррекции устройства управления и выход формирователя такта восстановления устройства управления соединены соответственно со входами пятой

и седьмой схем «И и через другую потенциальную схему «ИЛИ и схему «НЕ - с другими входами второй, четвертой и щестой схем «И, единичный выход усилителя считывания запоминающего устройства цифровой вычислительной машины соединен с импульспыми входами первого и второго клапанов и со входом первой импульсной схемы «ИЛИ, нулевой выход усилителя соединен с имнульсными входами третьего, четвертого и пятого клапанов и со входами первой и второй импульсных схем «ИЛИ, выход формирователя потенциалов первого цикла устройства управления подключен к потенциальному входу

первого клапана, выход которого соединен со входом второй импульсной схемы «ИЛИ, выходы импульсных схем «ИЛИ соединены соответственно с импульсными входами шестого и седьмого клапанов, потенциальные входы

второго, третьего, четвертого, пятого, шестого и седьмого клапанов соединены соответственно с выходами седьмой, второй, четвертой, пятой и щестой схем «И, выход формирователя потенциала такта записи результата

устройства управления соединен с потенциальным входом пятого клапана, выход которого подключен к счетному входу триггера нечетного разряда произведения и входу третьей импульсной схемы «ИЛИ, другие входы которой соединены с выходами второго, третьего и четвертого клапанов, выходы шестого, седьмого клапанов и третьей импульсной схемы «ИЛИ соединены соответственно со входами по «-2, по «+1 и по «-1 регистра адреса

оперативного запоминающего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1967 |

|

SU222740A1 |

| ДВОИЧНО-ДЕСЯТИЧНОЕ СУММИРУЮЩЕЕ УСТРОЙСТВО | 1968 |

|

SU220631A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для измерения угла опережения подачи топлива в дизель | 1985 |

|

SU1239391A1 |

| Устройство для измерения угла поворота коленчатого вала двигателя внутреннего сгорания | 1985 |

|

SU1334056A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

Авторы

Даты

1969-01-01—Публикация