Логическая схема «И-НЕ относится к элементам цифровых вычислительных машин, выполненных в транзисторно-транзисторной логике.

Известны логические схемы «И-НЕ транзисторно-транзисторной логики, содерл ащие входной многоэмиттерный транзистор, усилительный каскад и выходной каскад, состоящий из эмиттерного повторителя на составном транзисторе и выходного транзистора с заземленным эмиттером, коллектор которого соединен с эмиттером составного транзистора. В известных логических схемах «И-НЕ транзисторно-транзисторной логики база составного транзнстора выходного каскада соединена через резистор с земляной шиной. Недостаток известных схем «Н-ИЛИ-НЕ маломош,ной серии заключается в большом расходе мощности и а упомяиутом резисторе.

Предложенная схема отличается тем, что база выходного каскада составного транзистора через резистор соединена с коллектором выходного транзистора и выходом схемы. Это позволяет уменьш 1ть мощность рассеяния.

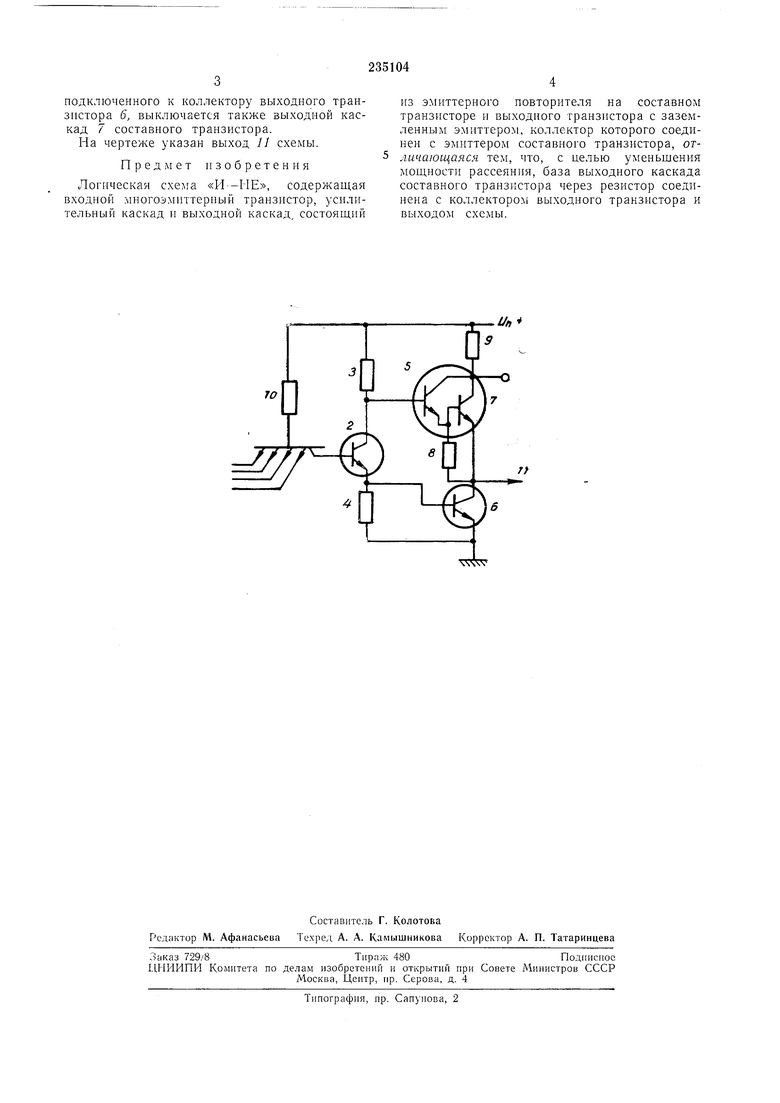

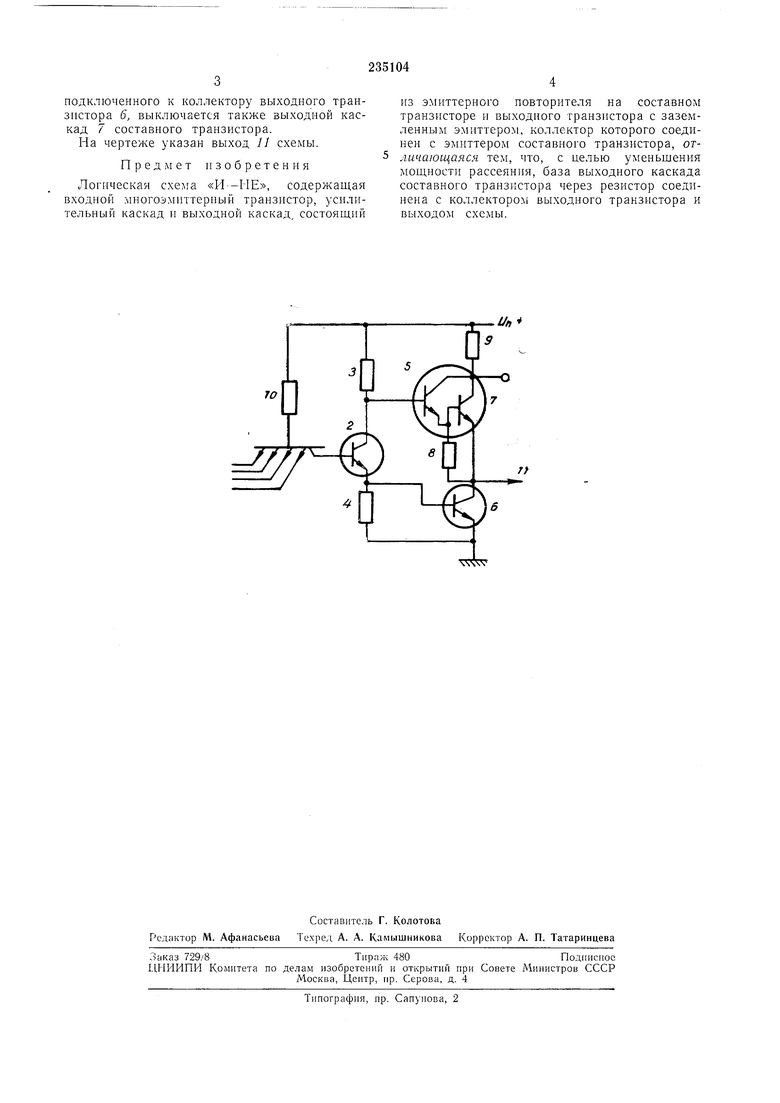

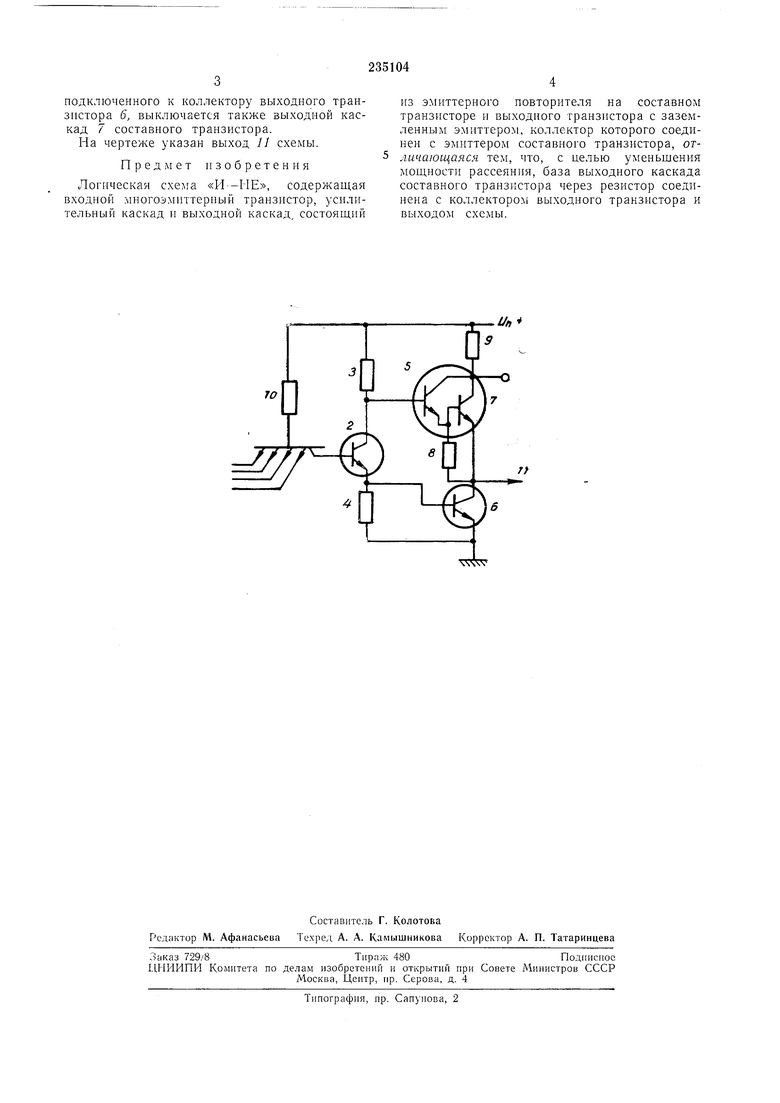

Предложенная схема «И-НЕ приведена на чертеже.

Она содери ит входной многоэмиттерный транзистор Л коллектор которого соединен с базой усилительного каскада на транзисторе 2 и резисторах Л и 4: коллектор транзистора 2

подключен к базе входного каскада 5 составного транзистора, а эмиттер - к базе выходного транзистора 6. Коллектор выходного транзистора 6 соединен с базой выходного каскада 7 составного транзистора через резистор 8. Коллектор составного транзистора через резистор 9 соединен с плюсовой шиной источника питания. При подаче на выход входного многоэмиттерного транзистора / низкого потенциала ток через резистор 10 иереключается в эмиттер этого транзистора, так что транзистор 2 выключается, )1 ток через его коллекторный резистор 3 переключается в базу входного каскада 5 составного транзистора.

Резистор 4 обеспечивает запирание выходного транзистора 6. Благодаря включению входного каскада 5 составного транзистора включается выходной каскад 7 этого транзпстора, что обеспечивает подачу высокого выходного уровня через токоограничивающий резистор 9.

При подаче на входы многоэмиттерного транзистора / высоких входных сигналов ток

через резистор 10 переключается в базу транзистора 2, затем включается выходной транзистор 6. В коллекторе транзистора 2 устанавливается низкий потенциал, И входной каскад 5 составного транзнстора выключается. Блаподключенного к коллектору выходного транзистора 6, выключается также выходной каскад 7 составного транзнстора. На чертеже указан выход 11 схемы.

Предмет изобретения

Логическая схема «И -НЕ, содержащая входиой многоэмиттерный транзистор, усилительный каскад н выходной каскад состояш,нй

из эмиттериого повторителя на составнол транзисторе и выходного транзнстора с заземленным эмиттером, коллектор которого соединен с эмиттером составного транзистора, отличающаяся тем, что, с целью уменьшения мощности рассеяния, база выходного каскада составного транзистора через резистор соединена с коллектором выходного транзистора и выходом схемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЭЛЕМЕНТ «И —НЕ» | 1973 |

|

SU409382A1 |

| Элемент для согласования насыщенных и ненасыщенных логических схем | 1972 |

|

SU438119A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| ПРИЕМНОЕ ИНТЕГРАЛЬНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU367553A1 |

| Логический элемент и-не | 1978 |

|

SU729848A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «И—ИЛИ—НЕ» и «И-ИЛИ» | 1970 |

|

SU260680A1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ДЛЯ ВОЗБУЖДЕНИЯ ДЛИННЫХ ЛИНИЙ | 1973 |

|

SU364106A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| УСТРОЙСТВО ДЛЯ СОГЛАСОВАНИЯ | 1973 |

|

SU374743A1 |

л

Даты

1969-01-01—Публикация