(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блокапОСТОяННОй пАМяТи | 1979 |

|

SU799019A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для контроля памяти | 1977 |

|

SU705526A1 |

| Устройство для контроля постоянных запоминающих устройств | 1976 |

|

SU563697A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU936036A1 |

| Устройство для контроля запоминающего блока | 1977 |

|

SU642774A2 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1003150A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

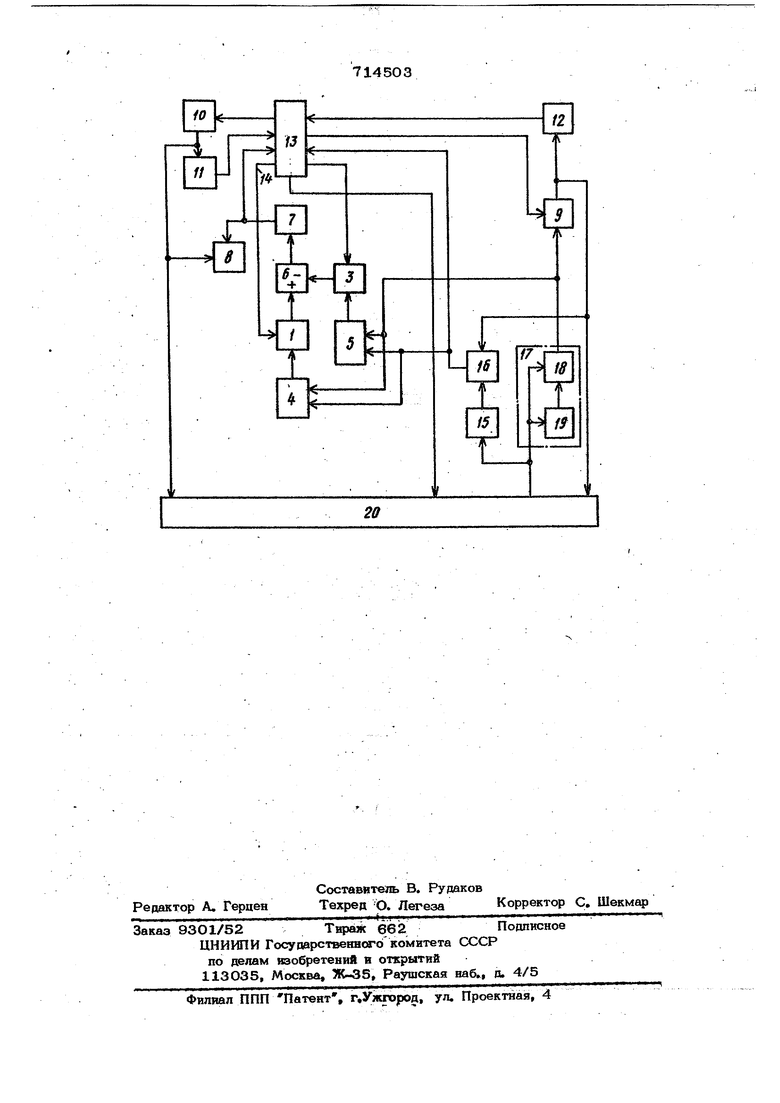

Изобретение отнсЛгится к области за- помшшющих устройств. Известно устройство для контроля памяти, которое содержит выходной регист вход которого подсоединен к выходу блока памяти, а выход - к блоку сравнения, счетчик адресов, разрядные выхо1ы кото рого подсоединены к блоку останова по адресу и запоминающему блоку, а выход к блоку управления . В этом устройстве оценка работоспособности массива ячеек блока памяти, определяемого начальным адресом, устанавливаемый в счетчике адресов и конечным адресом,за данным в блоке останова по адресу, производится-по результату сравнения поразрядной суммы по модулю два всей считанной информации с контрольной поразрядгюй суммой по модулю два всех чисел заданного массива. Та-. кая оценка работоспособности блока памяти не дозволяет выявить неисправности при четном их количестве в разрядах контролируемых чисел. Т1з известных устройств Наиболее близКИМ техническим решением к данному изобретению является устройство для контроля памяти, содержащее выходной регистр, вход которого подключен к входу устройства, а выход - к одному из входов блока сравнения, счетчик адресов, ылхо- ды которого соедю1ены с входами блока останова по заданному адресу и одним из выходов устройства, а вход - с блоком управления, коммутатор, входы которого подключены соответственно к выходу и входу преобразователя кодов и входу устройства, а выход соединен с входом счетчика контрольного кода, выход которого подключен к входу блока останова по контрольному коду, другому входу блока сравнения и другому выходу устройства 2. Это yctpoftcTBo при контроле постоянного блока памяти не позволяет опроделить разряды, в которых имеется четное количество ошибок (искажений информации), а .также количество таких разрядов; это, в свою очередь, приводит к увеличению времени контроля, так. как ОЛЯ .локализации всех ошибок требуется последовательная проверка всех разрядов блока памяти. КроМе того, в этом уст ойстве трудно сравнить результаты обшей проверки работоспособности блока С поразрядным контролем. При контроле блока оперативной памяти не осуществляется общий контроль его работоспособности (обнаружение общего количества ошибок) и не определяется зона массива, в котором обнаружены .ошибки. Целью настоящего изобретения является повышение быстродействия и упрощение устройства. Поста1зЛённая цель достигается тем, что устройство содержит счетчик ошибок регистр адреса первой ошибки, индикатор нулевого состояния счетчика ошибок, элементы И и элементы ИЛИ, входы кото рых подключены соответственно к выходам блоки сравнения и коммутатора, а . выходы - к одним из входов элементов И, :другйе входь Kdtopbix соединены с выходами блока управления, входы регис ра адреса первой ошибки подключены соответЬтвенно к выходу счетчика адресо) входу блока управления и. выходу индикатора нулевого состояния счетчика оши бок, соединенного с счетчиком ошибок, входы которого подключены к выходам элементов И. На Чертеже изображена блок-схема предложенного устройства. Устройство содержит элемент И 1, имеющий выход 2, элемент И 3, элемен ты ИЛИ 4 и 5, счетчик 6 ошибок, который выполнен реверсивным, индикатор 7 нулевого состояния счетчика ошибок, регистр 8 адреса первой ошибки, счетчик 9 контрольного кода, выполненный по схеме вычитающего счетчика с установо ,ными входами; счетчик 10 адресов, блок 11 останова по aiartaHHdivty адресу, блок 12 останова по контрольному коду, блок 13 управления, имеющий выход 14 выходной регистр 15, блок 16 сравнения, распределитель 17 Ийпупьсов, кото рый состоит вз коммутатора 18 и преоб разователя 19 кодов, служащего для преобразования парадлельного коца в пос ледовательный. К входам и выходам устройства подключается контролируемый блок 2О пам ти, который может быть либо блоком постоянной памяти (БПП), либо блоком оперативной памяти (БОН). Входы элементов ИЛИ 4 и 5 подключены соответственно к выходам блока 16 и коммутатора 18, выходы - к одним из входов элемэнтов И 1 и 3, другие входы которых соединены с выходами бЛока 13, входы регистра 8 подключень соответственно к выходу счетчика 1О, входу блока 13 и выходу индикатора 7, соединенного с счетчиком 6, входы которого подключены к выходам элементов И 1 и 3. , Устройство позволяет осушествить общий контро;ть работоспособности блоков БПП и БОП, а также локализацию искажений информации в них. Устройство работает по следующему принципу: общий контроль работоспособности блока памяти -.локализация ошибок в нем. Рассмотрим в качестве примера работу устройства при контроле блока постоянной памяти. Первоначально идет общяя проверка работоспособности блока 2О (выявление ошибок в информации или подтверждение исправности блока), для этого внешнее автоматическое контролирующее устройство (ВАКУ) (ВАКУ и его связи с устройством для контроля памяти не показаны) устанавливает в счетчике 9 конт рольный код, предбтавляюший собой о&щее количество единиц всех разрядов контролируемого массива блока 2О, через коммутатор 18 подсоединяет счетный вход счетчика 9 контрольного кода к выходу преобразователя 19 кодов, в счетчике 10 адресов устанавливает начальный адрес проверяемого массива блока 20, конечный адрес которого устанавливает в блоке 11 останова по заданному агфесу. По команде Пуск блок 13 управления начинает выдавать импульсы в блок 2О на считывание чисел из проверяемого массива и на счетный вход счетчика 1О для пересчета адресов проверяемого массива. Считанные числа с выхода блока 2 О поступают на счетные входы выходного регистра 15 и на входы преобразователя 19 и коммутатора 18. Все единицы чисел в последовательном коде на выходе коммутатора 18 подаются на счетный вход счетчика 9 контрольного кода, при этом в счетчике 9 происходит вычитание поступаюших единиц из ко1ггрольной суммы (контрольного копа), установленной в счетчике 9. Одаовременно происходит сравнение содержимого счетчика 10 адресов с конечным адресом, записанным в блоке 11 останови по заданному адресу, а блок 12 останова по контрольному коду, представляющий собой, например индикатор нулевого состояния. Следит за состоянием счетчика 9, и в выходном регистре 15 происходит поразрядное суммтфование по модулю дв всех считанных чисел. Подтверждение исправной работы блока 20 и прекра.щение контроля происход тогда, когда появляются ошювременно сигналы Останов с выхода блока II останова по заданному ащэесу и С выхода блока 12 останова по контрольному коду. В этом случае блок 13 управления передает в ВАКУ сигнал Запоминающий блок исправен. Сигнал с выхода блока 11 появляется тогда, когда содержимое счетчика 1О адресов сравнивается с содержимым блока 11, т.е. тогда, когда проверен весь заданшлй массив блока 20. Сигнал с выхода блока 12 появляет ся тогда, когда содержимое счетчика 9 будет равнйться нулю, т.е. тогда, когда количество считанных единиц всех чисел равняется заданному коду по данному ма сиву блока 20. Неодновременное появление сигналов Останов говорит о наличии искажений (ошибок) в считанной информации, т.е. о неисправной работе блока 20 в заданном массиве. При появлении на входе блока 13 управления только одного из сигналов Останов работа по контролю блока 20 не прекращается, а в дальнейшем происх дит подсчет общего количества ошибок в считанной информации. Для этого с выхода блока 13 управления па один из входов элемента И 1 выдается сигнал, который открывает элемент И 1, после чего едкнтщы считанных чисел с выхода коммутатора 18 поступают не только :ш счетный вход счетчика О, но и через элемент ИЛИ 4, элемент. И 1 на один из счетных входов счетчика 6 ошибок,, при этом в счетчике 6 будет происходить суммирование искажений информации в считанных числах, количество которых ограничивается вторым сигналом Останов, поступающим в блок 13 управления пибо от блока 11 остпнова по за- данному адресу, либо от блока 12 останова по контрольному коду. .Получив второй сигнал Останов блок 13 управления снимает сигнал с входа элемента И 1 и прекращает контроль блока 20. Налггчие ошибок, записанных в счет чике б, определяется индикатором 7, при этом на выходе индикатора 7 будет сигнал, обуславливающий формирование в блоке 13 управления сигнала Блок памяти неисправен, который поредпотся в ВАКУ. На этом заканчивается обшпя проверка работоспособности блока 20. Для поразрядной локализации ошибок в заданном массиве блока 20 из ВАКУ в блок 16 сравнения вводится контрольная поразрядная сумма по модулю два всех чисел заданного массива, после чего происходит сравнение с поразрядной суммой по модулю два всех считанных чисел, зпфиксирова1гной в выходном регистре 15. Разрядь, в которых имелось почетное колггчество ошибок в считппной информации, определяются наличием сигналов па соответствующих разрядных выходах блока 16 сравнения (но гюказпны). Те разряды блока 20, в котор 1х имелось четное количество ошибок, и разряды, в которых не имелось пообшс искажений информации с помощью блока 10 сравненияобнаружить невозможно. Поэтому дальнейшаяпоразрядная локализация ошибок в блоке 2О происходит следующим образом. По Сигналу от ВАКУ леропаотся команда на последоватрлы1ую порпзряшгую проверку разрядов блока 2О, в которых зафиксированы ошибки по мопупю дпа. Процесс проверки блока 2О происходит аналогичпо описанному выиго, только, п этом случае, в счетчике О ко11Т)ольпого кода устанавливается коитрольЕшя сумма единиц .проверяемого разряда, п с помошыо коммутатора 18 подключается выход блока 20 проверяемого разряда к счетному входу счетчика У контрольного кода. При появлении одного из сит-нолов . Останов блок 13 управления нп один из входов элемоптп И 3 сигнал который открывает элемент И 3, после чего считанные единицы с .выхода коммутатора 18 поступают кпк по счотный вход счетчика 9, так и через элемент ИЛИ 5, элемент И 3 ип счетный пход счетчика 6 ошибок, при этом в счетчике 6 будет происходить вычитание ошибок проверяемого разряда вз общего количес ва ошибок всех разрядов, зафиксированных при общем контроле блока 2О, Посл получения второго сигнала Останов блок 13 управления снимает Сигнал с хода элемента И 3 и передает в ВАКУ сигнал об окончавви проверки;блока 2О по данному разряду. Получав этот сиг- нал, ВАКУ передает команду на проверку следующего разряда. После последовательной проверки всех разрядов в которых обнаружены ошибки пб модулю два, и если при этом счетчик 6 ошибок установился в нулевое состояние, обнаруживается индикатором 7, на выхо де индикатора 7 появляется сигнал Останов контроля, вря этом блок 13 управления передает в ВАКУсигнал Контроль БПП закончен в в 9тбм подтверждается безошибочность кон роля по модулю два. Если же в счетчщсе в ошибок аулевое состояние не ycTaHOBAeiabi, то это. показывает, что контроль по модулю два не точный и в блоке имеются разряды с чётным количеством ошибок. Для локализации ЭТИХ рйарядоб произ Вордатся поочередная проверка оставшихся разрядов блока 20. Проверка заканчивается тогда, когда ечетчик 6 ошибок установится в нулевое состояние. Даль- нейшая гфоверка БПП не вмеет смысла, так как локализованы все ошибки. В описанйом устройстве не тЬлько сокраоюется время на. локализацию ошиб но и отпадает необходимость контроля всех разрядов блока памяти. Формула изобретения Устройство для контроля памяти, содержащее выходной регистр, вход которого подключен к входу устройства, а выход - к одному из входов блока сравнения, счетчик адресов, выходы которого соединены с входами блока останова по заданному адресу и одним из выходов устройства, а вход - с блоком управления, коммутатор, входы которого подключены соответственно к выходу и Ъходу преобразователя кодов и входу устройства, а выход соединен с входом счетчика контрольного кода, выход которого подключен к входу блока останова по контрольному коду, другому входу блока сравнения и другому вькоду устройства, отличающееся тем, что, с целью повышени:я быстродействия устройства, ою) содержит счетчик ошибок, регистр адреса первой ошибки, индикатор нулевого состояния счетчика ошибок, элементы И и элементы ИЛИ, входы которых, подключены соответственно к выходам блока сравнения и коммутатора, выходы - к одним из входов элементов И, другие входы которых соедш1ены с вькодами блока управления, входы регистра адреса первой ошибки подключены соответствейно к выходу счетчика а {фесов, входу блока управления и выходу индикатора нулевого состояния счетчира ошибок, соединенного с счетчиком ошибок, входы которого подключень к выходё1М эпемён тов И, Источншш информации, гфинятые во внимание при экспертизе 1.Авторское свидетельство СССР N9 357584, кл. Q 11 С 29/00, 1969. 2.Авторское свидетельство СССР N9 41353О, кл. Q 11 С 29/ОО, 1972 (прототип).

Авторы

Даты

1980-02-05—Публикация

1977-09-26—Подача