1

Изобретение относится к области контроля запоминающих устройств и может быть использовано для контроля постоянных запоминающих устройств (ПЗУ) и кодовых жгутов в процессе их производства и эксплуатации.

Известно устройство для контроля постоянных запоминающих устройств, где контроль осуществляется методом последовательного суммирования чисел, заложенных в ПЗУ, и сравнением полученной суммы с контрольным числом, содержащее счетчик адресов, блок анализа, блок синхронизирующих импульсов.

Недостаток этого устройства состоит в невысокой достоверности контроля в проведении поиска неисправности, что приводит к больщим материальным затратам 1.

Известно устройство для контроля ПЗУ, содержащее блок ввода информации, блок согласования и ЭВМ (универсальную или специализированную). Указанное устройство сложно в эксплуатации и не обеспечивает контроля объекта в реальном масщтабе времени .

Известно также наиболее близкое к изобретению по технической сущности устройство для контроля постоянных запоминающих устройств 3, содержащее последовательно соединенные дещифратор адреса и коммутатор, подключенный к блоку анализа ощибок, основному адресному счетчику, генератору синхроимпульсов, к входу и выходу устройства, блок считывания, соединенный с адресным счетчиком и блоком управления, выходы которого подключены к генератору синхроимпульсов и блоку анализа ощибок.

Устройство имеет недостатки, такие как невысокое быстродействие и отсутствие динамических режимов проверки, исключающее возможность проверки в реальном масщтабе времени, что снижает достоверность и качество контроля.

Цель изобретения - повышение быстродействия контроля постоянной памяти и кодовых жгутов, что ведет к значительному сокращению времени контроля, универсальности самого процесса контроля на основе расщирения функциональных возможностей, так как процесс контроля в предлагаемом устройстве возможен несколькими методами одновременно, и

к значительному снижению материальных средств, расходуемых на контроль постоянной памяти и кодовых жгутов в процессе производства и эксплуатации. Это достигается в предлагаемом устройстве

тем, что в него введены последовательно соединенные дешифратор определения приоритета, распределитель и блок выборки адресов приоритета, регистр определения приоритета, блок ключей и дополнительный адресный

счетчик, соединенный с основным адресным

3

счетчиком, блоком управления и блоком выборки адресов приоритета, вход которого подключеп к блоку управления, выходы блока управления подсоединены к входам дешифратора определения приоритета, раеиределителя и блоку ключей, выход которого соединен с регистром определения приоритета, соединенным с блоком считывания и блоком анализа ошибок, выход распределителя связан с входом блока ключей.

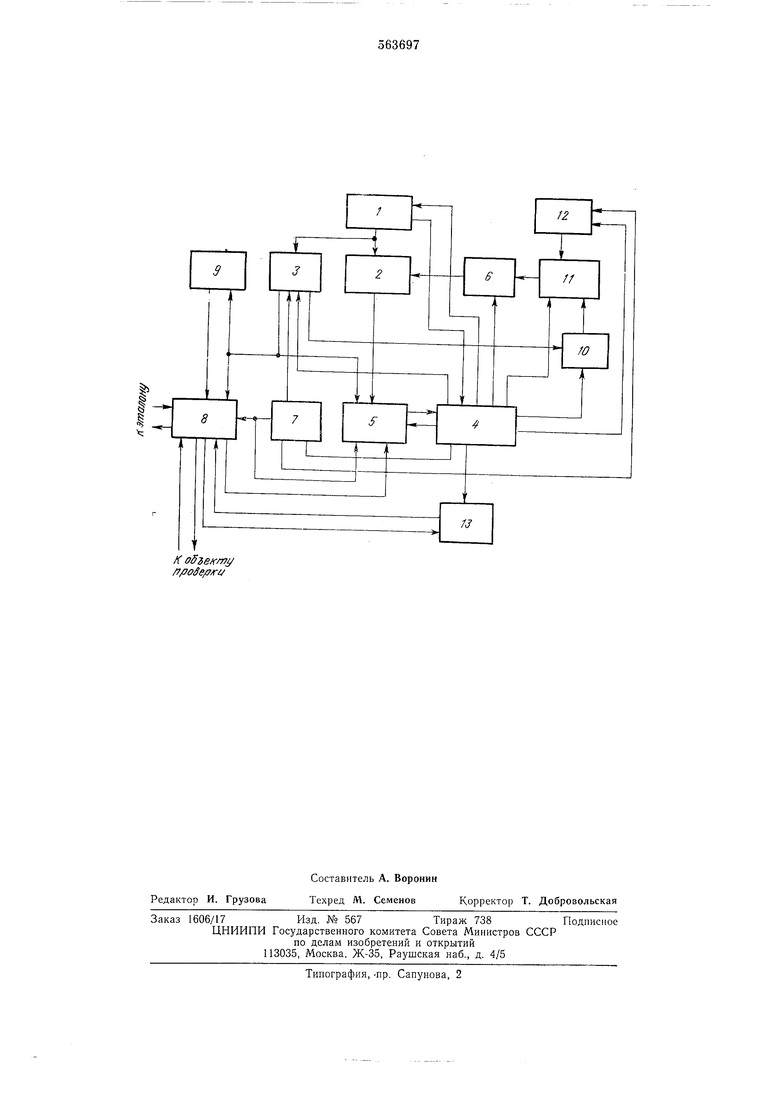

На чертеже представлена функциональная схема устройства.

Она содержит блок 1 считывания, соединенный с регистром 2 определения приоритета, с адресным счетчиком 3 и блоком 4 управления. Регистр 2 определения приоритета соединен с блоком 5 анализа опшбок и блоком ключей G, адрес}1ый счетчик 3 --- с донолнительным адресным счетчиком 7, коммутатором 8, дешифратором 9 адреса, дешифратором 10 определения приоритета, с блоком 4 управления и с блоком 5 анализа ошибок. Блок 4 управления связан с блоком 5 анализа , дополнительным адресным счетчиком 7, дешифратором 10 определения приоритета, распределителем И, блоком 12 выборки адресов приоритета и генератором 13 синхроимпульсов. Блок 5 анализа ошибок подключен к дополнительному адресному счетчику 7, коммутатору 8 и блоку 12 выборки адресов приоритета. Коммутатор 8 подсоединен к дешифратору 9 адреса, генератору 13 синхроимпульсов и имеет выходные шины для подключения к внешнему эталону и объекту проверки. Дешифратор 10 определения нриоритета соединен с распределителем 11, распределитель - с блоком 12 выборки адресов приоритета.

Устройство может работать в трех режимах: сравнение с контрольной нерфокартой; сравнение с эталоном; контрольное суммирование.

Работа устройства в релшме сравнения с контрольной перфокартой осугцествляется в следуюш,ей носледовательности.

При «ажатии на кнопку «Пуск вырабатывается сигнал в блоке управления, который включает блок 1 считывания, и начинается поступление перфокарт в поле считывания. Считанная с перфокарт информация в виде электрических сигналов попадает в адресный счетчик 3 и устанавливает в нем начальный адрес, по которому требуется прочитать информацию, заложенную в контролируемый блок. Одновременно с адресом через регистр 2 онределения приоритета в блок 5 анализа ошибок поступает числовая информация, а в блок 4 управления - управляющие сигналы. В блоке управления формируется сигнал, который подается в генератор синхроимпульсов, являющийся началом формирования временной диаграммы для работы контролируемого блока. Временная диаграмма строится при помощи регистров сдвига в соответствии с программой, заданной коммутатором.

Считанное с контролируемого блока число через коммутатор поступает в блок 5, где происходит анализ поступившей инфромации. В случае исправности выдается сигнал в блок 4 управления на продолжение работы. Контроль работы по одной перфокарте производится в естественном порядке, для чего из блока управления на входы адресного счетчика 3 и дополнительного адресного счетчика 7 поступают сигналы, увеличивающие адрес в каждом счетчике на единицу. При обнаружении ошибки в блоке 5 вырабатывается сигнал, который проходит в блок 4 управления, прерывающий контроль.

При этом закрывается счетный вход адресного счетчика, запоминая адрес номера ячейки памяти, в которой была обнаружена ошибка. В блоке 4 управления вырабатывается команда, по которой начинают работать блок 12 выборки адресов приоритета, подключенный к младшим разрядам адресного счетчика 7, раснределителя 11 и блоку ключей 6.

Изменение состояний адресного счетчика 7 при поступлении на его вход единичного сигнала через блок выборки адресов приоритета, распределитель и ключи обеспечивает размещение информации, считываемой с программоносителя в регистре 2 определения приоритета.

После регистрации 01иибки с блока управления поступает сигнал, запрещающий работу блока выборки адресов приоритета, закрывается счетный вход адресного счетчика 7, открывается счетный вход адресного счетчика 3 п выдается разрешение на работу дешифратора 10 определения приоритета, который подключен к выходу младщих разрядов адресного счетчика. Дешифратор определения приоритета через распределитель 11 и ключи 6 начинает управлять поступлением информации, размещенной в регистре 2 определения приоритета, на вход блока 5 анализа ошибок. Одновременно с каждым выводом числа из регистра определения приоритета дается приращение в адресный счетчик 3 для выборки числа из объекта проверки. После вывода последнего числа и сравнения кодов адресного счетчика 3 и дополнительного 7 в блоке анализа ошибок происходит прерывание работы дешифратора 10 определения приоритета и распределителя 11. Ключи 6 закрываются, информация с блока 1 считывания начинает поступать через регистр определения приоритета на вход блока анализа ошибок и работа продолжается в соответствии с изложенным. Работа устройства ирекращается но окончании вынолнения программы или остановом оператора.

В режиме работы сравнения с эталоном, который как и объект проверки подключается к коммутатору 8, устройство работает следующим образом. При нажатии на кнопку «Пуск из блока 4 управления в генератор синхроимпульсов поступает сигнал, по которому формируются импульсы в соответствии

с временной диаграммой, заданной программой коммутатора 8. При воздействии на входы контролируемого и эталонного блоков ответная реакция с них в виде числовой информации через коммутатор проходит в блок анализа ошибок и при ее соответствии выдается сигнал на онрос следующего адреса, который увеличивается на единицу нутем прибавления ее в адресные счетчики 3 и 7. Введение дополнительного адресного счетчика 7 для задания адресов в режиме контроля с эталонным блоком исключает возможность пропуска массивов или отдельных адресов, так как одинаковый сбой мало вероятен, а расхождение в адресах или числовой информации представляется как сбой в работе, который вызывает прекращение проверки с анализом причины иесовпадонии кодов.

Проверка ведется в реальном масштабе времени работы контролируемого объекта и продолжается до адреса, заданного оператором. Применение самопрограммирования, основанного ia в;шимосвязях объекта проверки, коммутатора и генератора синхроимпульсов, практически дает возможиость иеограниченного расширения номенклатуры проверяемых блоков иостоянной памяти и кодовых жгутов.

В режиме контрольного суммирования проверяются блоки, предварительно ирошедшие проверку на правильность размещения в них информации в режиме сравнения с контрольной перфокартой.

Проверка в режиме контрольного суммирования необходима для контроля работы иостояниой иамяти в диламическом режиме в реальном масштабе времени и ирименяется в случае отсутствия эталоиных блоков при изготовлении в производстве первых образцов, а так}ке может быть использована для профилактических нроверок памяти в процессе эксплуатации.

В режиме контрольного суммироваиия устройство работает следующим образом. При нажатии на кнопку «Пуск из блока управления в генератор синхроимпульсов поступает сигнал, по которому происходит формирование импульсов в соответствии с временной диаграммой, заданной программой в коммутаторе 8. Считанная информация с объекта проверки через коммутатор подается в блок 5 анализа , после чего происходит повторение цикла. Каждый раз, с поступлением информации в блок анализа ошибок, происходит сложение в}швь поступившего числа с суммой ранее поступивших чисел, в результате чего иронсходит накапливание суммы чисел, считанных с контролируемого блока ири каждом обрашении к нему. После сложения числа, считанного с последнего адреса, нолученная сумма сравнивается с контрольным числом, которое вводится в блок анализа ошибок после оироса последнего адреса, и в случае совпадения выдается сигнал исправности контролируемого блока и вырабатывается

команда «останов. В это.м режиме ири проверке блоков памяти, емкость которых ие ирепышаст возможностей выборки адресных счетчиков 3 и 7, они работают параллельно,

обеспечивая повышенную надежность контроля.

В случае контроля блоков памяти с большой емкостью накопителя адресные счетчики 3 и 7 могут быть подключены последовательно,

что значительно увеличивает разрядность адресности устройства.

Предложенное устройство позволяет повысить быстродействие контроля в три, четыре раза и получить достоверность проверки,

близкую к единице, что значительно сокраи ает время технологического процесса выцуска блоков постоянной памяти, иовышает производительность труда и качество выпускаемых приборов.

Кроме того, внедрение предлагаемого контролирующего устройства обеспечит сокращение номенклатуры испытательной аппаратуры для контроля различных тнпов блоков постоянной памятп и кодовых жгутов в два-

три раза, что составит экономию расходов па контроль норядка сто тысяч рублей.

Формула и 3 о б р е т е н п я

Устройство для контроля постоянных заиоMHiiaionuix устройств, содержащее последовате„1ьно соединенные дешифратор адреса и комм татор, подключенный к блоку анализа ошибок, основному адресному счетчику, генератору сиихроимпульсив, к входу и выходу устройства, блок считывания, соединенный с адресным счетчиком п блоком управления, выходы которого подключены к генератору синхроимпульсов и блоку анализа ошибок,

отличающееея тем, что, с целью повышения быстродействия устройства, в него введены последовательно соедпнепные дешифратор определения приоритета, распределитель и блок выборки адресов приоритета, регистр

определения приоритета, блок ключей и дополнительный адрееный счетчнк, соединенный с основным адресным счетчиком, блоком управления и блоком выборки адресов приоритета, вход которого иодключен к блоку управления, выходы блока управления подключены к входам дешифратора определения приоритета, распределителя и блоку ключей, выход которого соединен с регистром определения нриоритета, соединенным с блоком считынаПИЯ и блоком анализа ошибок, выход распределителя сосдииеп с входом блока ключей.

Источники информации, принятые во внимание нри экспертпзе:

1.Авторское свидетельство СССР Л 235106, кл. G ПС 29/00, 1967.

2.Авторское свидетельство СССР Л 384139, кл. G ПС 17/00, 1973.

3.Авторское свидетельство СССР Л1230 21, кл. G ПС 29/00, 1967.

К oSzefffTjj flflo e/7ffj

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для контроля постоянных запоминающих устройств | 1976 |

|

SU622175A2 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1411838A2 |

| Устройство для контроля постоянной памяти | 1984 |

|

SU1191944A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU936036A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1345212A1 |

| Устройство для контроля печатных плат | 1986 |

|

SU1472929A1 |

| Устройство для управления блоком памяти | 1982 |

|

SU1164718A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

Авторы

Даты

1977-06-30—Публикация

1976-04-06—Подача