Предложение относится к области вычислительной те.хники.

Известно матричное арифметическое устройство, выполненное на модулях, соединенных каналамисвязи со своими четырьмя соседями. Однако это устройство ироводит арифметические онерации иоследовательно поразрядно, что увеличивает время выполнения арифметической операиии.

Предложенное матричное арифметическое устройство отличается тем, что каждая ячейка матрииь состоит из .7-разрядных сумматоров и одного выходного «-разрядного преобразователя полярности числа, соединенных каскадиоиоразрядно, причем каждая из ячеек матрицы связана четырьмя информационными каналами с соседними ячейками и входным канало.м с оперативным запоминающим устройством (). Быстродействие ири выполнении операции умножения повышается благодаря введению дешифратора умножения-дешифратора иостоянного сдвига, выходы которого служат управляюшими входами вентилей, связанных е ОЗУ. При операции деления - благодаря иаличию дешифратора деления, состоящего из логических ко бииационных схем ввода взвешенного делителя и передачи промежуточного результата, соответствующих каждой линейке матрицы, и схемы масштабирования делителя, содержащей схему автоматического сдвига чиела, схему определения масштабных коэффициентов, дешифратор постоянного сдвига, логические комбинационные схемы связаны одной групиой входов с ячейками матрицы, а другой груииой входов - с выходами дешифратора постоянного сдвига, подключены также к устройству автомагического сдвига числа, входами которого служат выходы ячеек матрицы, соединенных, кроме того, со схемой ойределения маси1табного коэффициента. Выходы последнего, а также вторая группа выходов логических комбинационных схем через выходно дешифратор образуют выход|,1, соответств)ющие зезультатам деления.

В предложенном матричном арифметическом устройстве повышение б1)1стродействия достигается за счет исиользования CBOIICTB отрнцательной системы счисления. В связи с тем, что при сложении двух чисел в системе счисления с ocиoвaниe (-2) перенос из млади1его разряда в старший носит двойственный характер, т. е. единица переноса может быть как субстрактивной, так и аддитивной, в сумматоре имеют место два типа переносов - субстрактивный и аддитивиый.

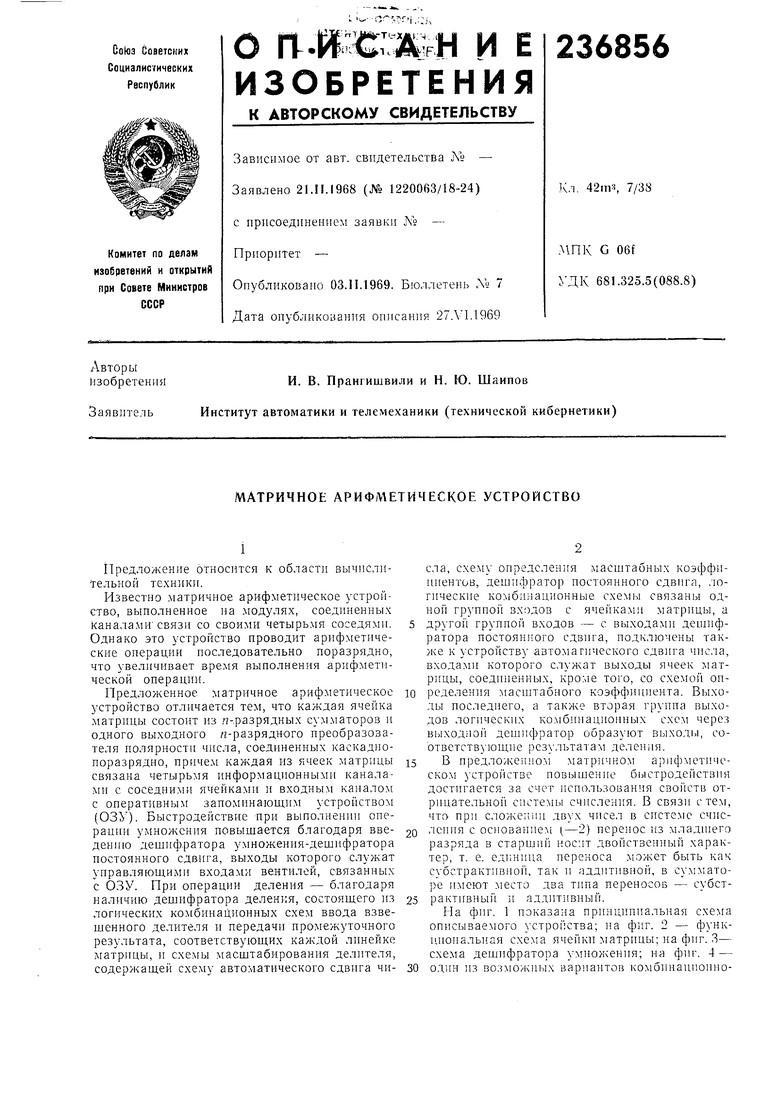

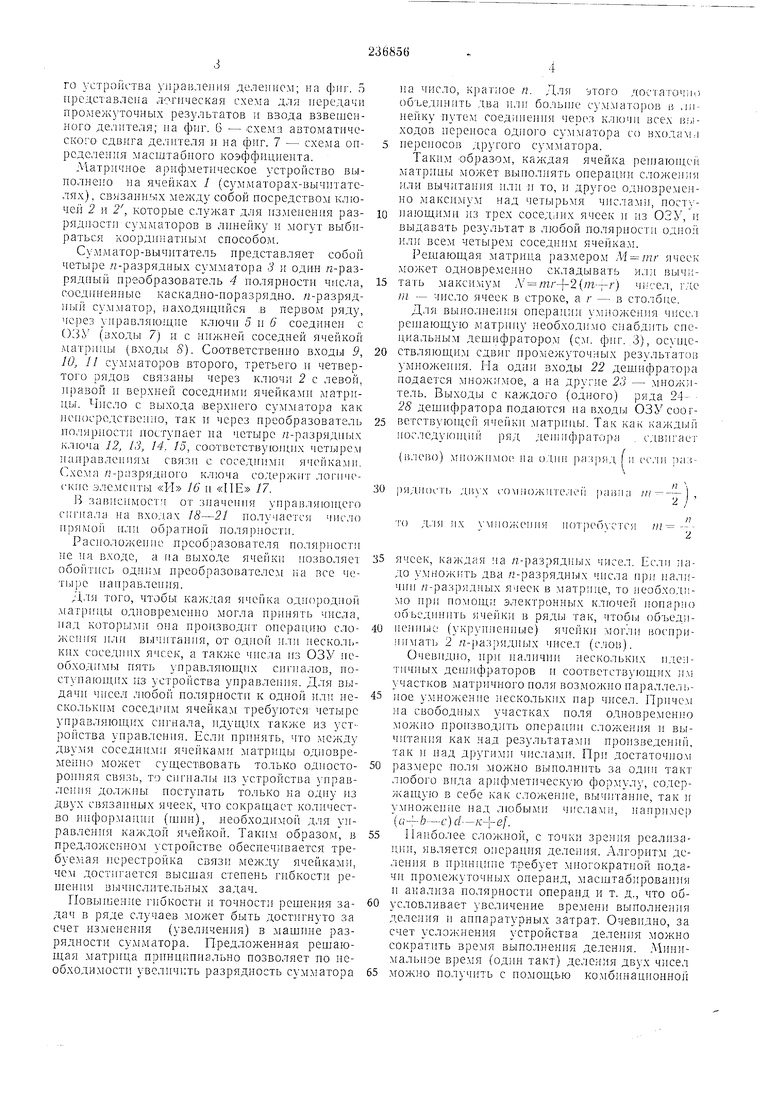

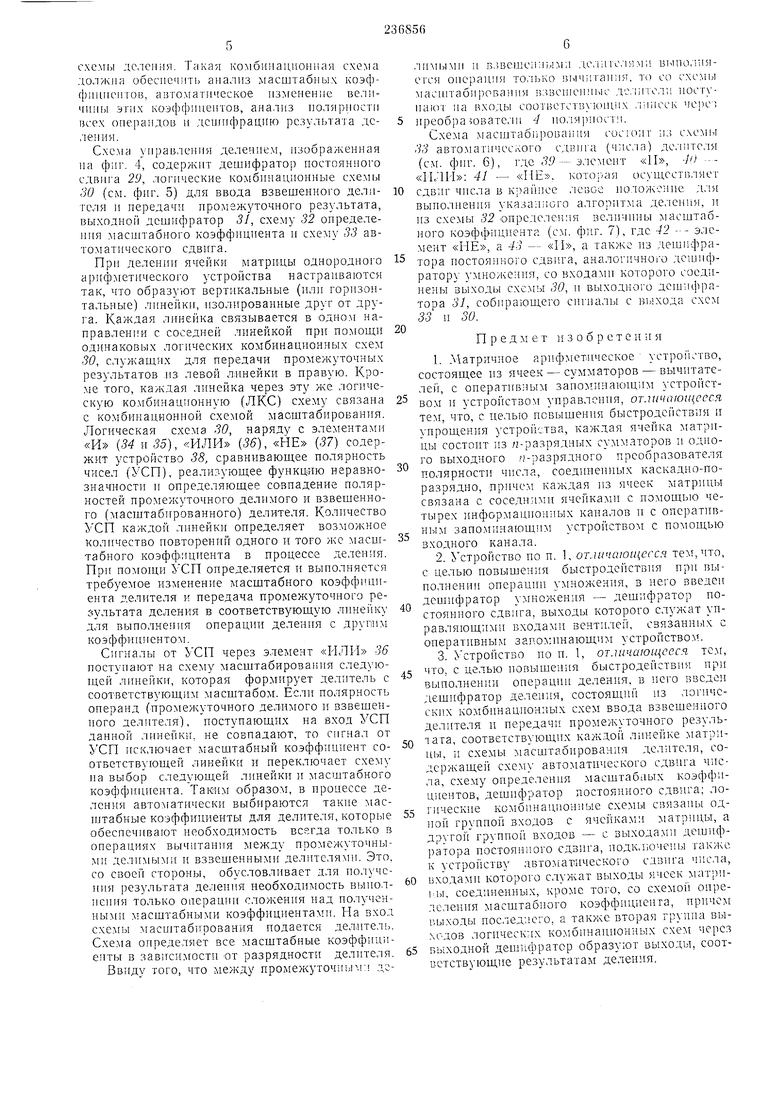

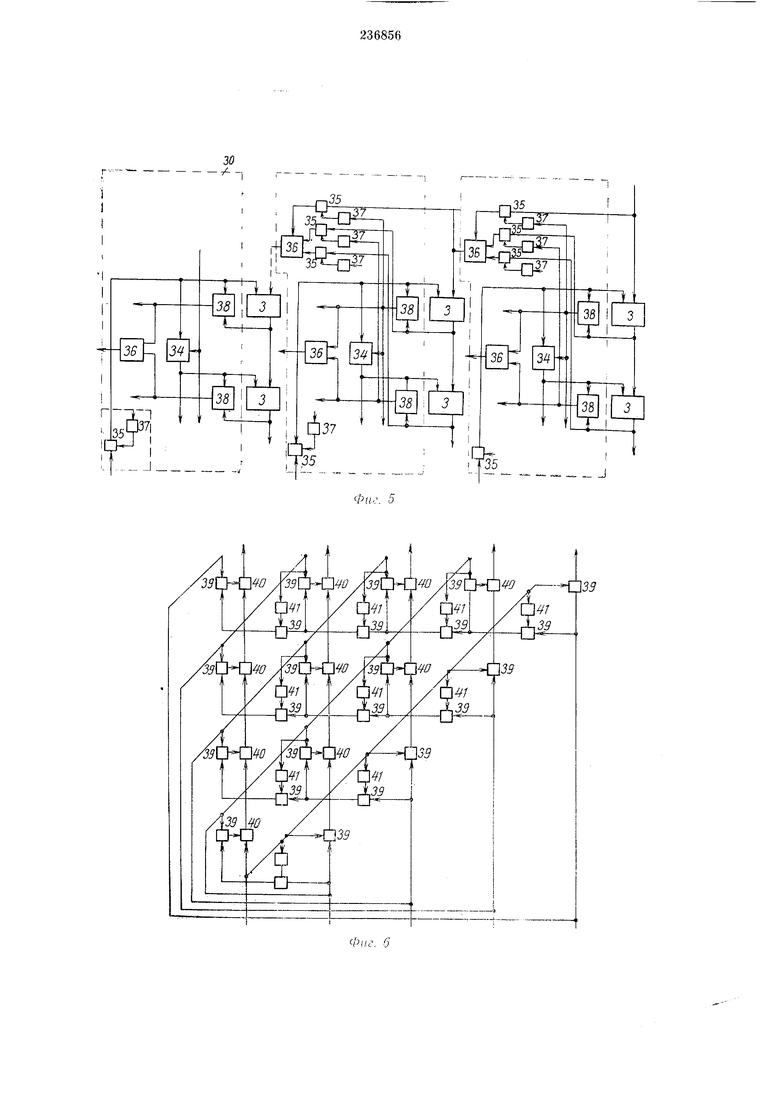

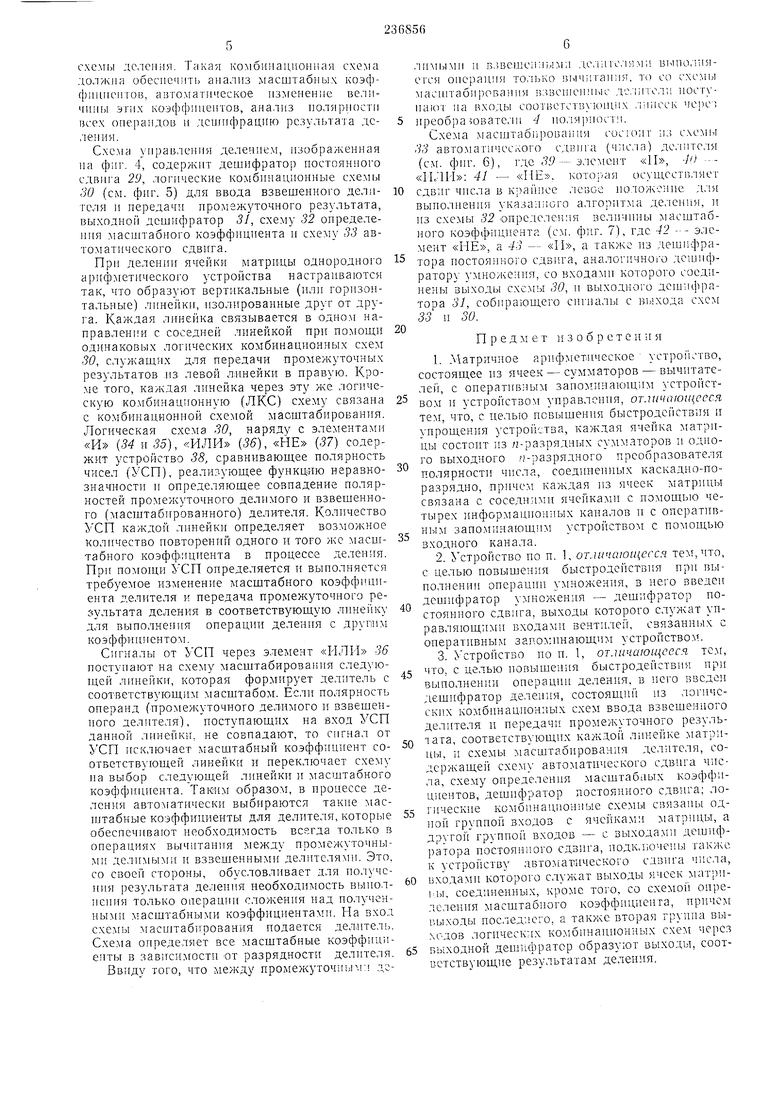

Па фиг. 1 иоказана принциииальиая cxcNta описываемого устройства; иа фиг. 2 - функциональная схе.ма ячейки матрицы; на фиг. 3- схема дешифратора умножения; иа фиг. 4 - один из возможных вариантов комбииаиионного устройства унраиления делением; на фнг. 5 представлена лотическая схема для нередачн нромежуточных результатов и ввода взвешенного делителя; на фиг. 6 - iCxe.MSi автоматического сдвига делителя и на фпг. 7 - схема онределения масштабного коэфф1тцне)1та.

Матричное а)иф 1етическое устройство выиолнено на ячейках / (сумматорах-вычитателях), связанных между собой посредством ключей 2 и 2, которые служат для из.меиення разрядности сумматоров в линейку и могут выбираться коордниатиыл способом.

Сумматор-вычитатель представляет co6oi i четыре л-разрядных сумматора 3 и один л-разрядный преобразователь 4 иолярностп числа, соединенные каскадно-поразрядно. /г-разрядиый еул1матор, находящийся ,в первом ряду, через уиравляющ.ие ключи 5 и 6 соединен с () (входы 7) и е нижней соседней ячейкой матрицы (входы 5). Соответствепно входы 5, 10, 11 сумматоров второго, третьего и четвертого рядов связаны через ключи 2 с левой, иравой и верхней соседними ячейками Л1атриды. Число с выхода верхнего сумматора как )()средст1зенно, так и через преобразователь по.чярности поступает па четыре /г-разрядпых ключа 12, 13, 14. 15, соответствующих четырем направлениям связи с соседпимн ячейками, (хема /г-рпзрядно1о ключа содержит ло1Ч1чоскис элемс1ггы «I-i 16 п «НЕ 17.

зависимости от значения уира1 ляюи1,его сигнала иа вхол.ах 18-21 иолучается число прямо пли об :1атной ноля)ности.

Расиоложеиие преобразователя полярности не на входе, а tia выходе ячейки иозволяет обо11тись нреобразователе.м на все четы|)е направления.

Для того, чтобы каждая ячейка одн()родио11 Л1. одиовремеиио могла ир1П1ять числа, над которьрли она нропзводит операцию слоЖСИ1ГЯ или выиггаиия, от одной или нескол)ких соседних ячеек, а также чис.та из ОЗУ необходимы пять управляющих сигналов, поступакпцих из устройства управления. Для выдачи чисел любой полярпостп к одной или иесколькнм соседпнм ячейкам требуются четыре управляюн 1,их снгнала, ндущих также из устpoiiCTBa управленпя. Если прпнять, что между соседнилгп ячейками матрицы одиовременпо может существовать только одиостороиияя связь, то сигнал) из устройства унравлеиия должны поетупать только на из двух связа ных ячеек, что сокращает количество инфор-Ашиии (гний), необходимо для управления каждой ячейкой. Таким образом, в предложенном устр011стве обеспеч вается требуемая )ерестройка связ) ячейками, че дост1 гается высшая стеиень гибкости реП1ения Б лч 1слительн з1х задач.

Повьииение ибкостп и точности решения задач в ряде случаев может быть достигнуто за счет изменения (увеличепия) в машппе разрядности су,Д1матора. Предложенная решаюгцая матрица принципиально позволяет цо неoбxoди ocти увеличить разрядность сумматора

па число, кратное п. Для этого достаточно объедин.ить два сумл аторов н лииейку путем соединеп Я через всех в;,ходов одного сул матора со входами

другого сумматора.

Таким образом, каждая ячейка матриць может выполнять операции сло/ ;ен1 я или вычитан я или ц то, 1 другое одновременно макснл ум над четырьмя ч 1слал И, посту)ающимп из трех соседних ячеек ) из ОЗУ, i выдавать результат в любой полярпости одно) или всем четырем соседним ячейкаль

Решающая 1)азмером М пг ячеек молует одновременно складывать или вычитать максимул A mr-f-2(m-rr) , где til число ячеек в строке, а г - в столб 1е.

Для вь о;п-1ения умножения .i ре цающую .у необход П о снабдить специальным дешифратором (c. . 3), осуп,ествля ощи,м сдвиг промежуточнь х результате) умножен 1я. На одни входы 22 дешифратора подается множимое, а на другие 23 - множитель. В з1ходы с каждого (одного) ряда 24- 25 дешифратора подаются ia вход ОЗУсоогветствуюпдсй ячейк .. Так как 1 оследую ц11й ряд де 1нфратора . сдвнгаст

ячеек, каждая а /г.-разряд 1ых чисел. Есл1 надо умнож ть два «-разрядных при иалиЧ 1 /7-разрядпых ячеек в л атрице, то .чеобход МО Нр ЭлеКТрОННЫХ

обьед П1Ть ячейки в ряд) так, чтобы обтзеди 1еИ 1)1С (уКруПИеИ Ые) ЯЧеЙК Ю( 2 /г-разряд 1 1х чисел (слов).

, рИ 1аЛПЧП 1 НеСКОЛЬК Х ДеНтнч ых де1пифраторов i соответствуюших и.

участков матричного поля возмож 10 нараллел,лое умножен 1е несколькнх нар чисел.

иа свободиых участках поля oдиoвpe eн o

ПрО 13ВОДИТЬ ОПерац СЛОЖеН1 Я и ВЫчита П1я как над результатами ироизведеипй, так над другидп чпеламп. При достаточ о.м

цоля можно выполнить за ОД1П такт л обого вида ариф гетическую формулу, содержащ чо в себе как , выч 1таи1 е, так ir умиожеи е aд любым ч(с.там11, аирил ер (G--/;-- C)f/-/с-{-е/.

11а 1более сложтюй, с точки зрения реалнзаЦ, является оиерация делеи 1Я. Алгоритм деле я в ц)ин,иие требует м Югократ1Ю11 подач промежуточных операнд, мас цтабпрова П я апалпза полярности операнд и т. д., что обусловливает увеличенпе времеп т вь нолпения деления и аппаратурных затрат. , за счет усложнения устройства деления можно сократ ть время выполнения деления. М Щпмаль ое время ( такт) деления двух чисел

схемы деления. Такая комбинационная схема должна обеснечнть анализ масштабных коэффнинентов, автоматическое нз reнeниe величины этих коэффнцентов, анализ полярности ijcex онерандов и дени|фрацию результата деления.

Схе.ма унравлеиия деленне.м, изображенная на фиг. 4, содержит дешифратор постоянного сдвига 29, логические комбинационные схемы SO (см. фиг. 5) для ввода взвешенного делителя и передачи промежуточного результата, выходной дешифратор 5/, схему 32 определения масштабного коэффициента и схему 33 автоматического сдвига.

При делении ячейки матри.цы однородного арифметического устройства настраиваются так, что образуют вертикальные (или горизонтальные) линейки, изолированные друг от друга. Каждая линейка связывается в одном направлении с соседней линейкой при помощи одинаковых логических комбинационных схем 30, служагцих для передачи промежуточных результатов из левой лтшейки в правую. Кроме того, каждая линейка через эту же логическую комбинационную (ЛКС) схему связана с комбинационной схемой масштабирования. Логическая схема 30, наряду с элементами «И (34 и 55), «ИЛИ (36}, «НЕ (57) содержит устройство 38, сравниваюш,ее полярность чисел (УСП), реализующее функцию неравнозначности и определяющее совпадение полярностей промежуточного делимого и взвешенного (масштабированного) делителя. Количество УСП каждой линейки определяет возможное количество повторепий одного и того же масштабного коэфф:ициеита в процессе деления. При помощи УСП определяется и выиолняется требуемое измеиение масштабного коэффициента делителя и передача промежуточного реГАльтата деления в соответствующую лтшейку для выполнения операции деления с другим коэффициентом.

Сигналы от УСП через элемент «ПЛИ 36 поступают на схему масштабирования следующей линейки, которая формирует делитель с соответствующим масштабом. Если полярность операнд (промежуточного дедилюго и взвешенного делителя), поступающих на вход УСП данной линейки, не совпадают, то сигнал от УСП исключает масштабный коэффициент соответствующей линейки и переключает схему на выбор следующей линейки и масштабного коэффициента. Таким образом, в процессе деления автоматически выбираются такие масП-1табные коэффициенты для делителя, которые обеспечивают иеобходимость всегда только в операциях вычитан1тя между иро гежуточны п делимыми и взвешенными делителями. Это, со своей стороны, обусловливает для иолучеиия результата делеиия необходимость выиолнсния только операции сложения пад иолученными масштабными коэффициентами. На вход схемы масштабирования подается дел итель. Схема определяет все масштабные коэффициенты в зависимости от разрядности делителя.

.)1МИ и Б.шешсшплмл дспиго.к-ши .шяется операция тол1зко вьпппаиия, то со cxcMbt масштабир овании г звси1сииыс дсл1ггол;1 иостуиают иа входы соответств юии1х /пшсок чсрсч иреобратоватсли 4 ио.чяриогП.

Схема Агаси 1табпрова1П1я cocio;ir из схемы 33 автоматического сдвига () дс.читсля (см. фиг. 6), где 5..9 - элемент «П, -10 --«НЛП : 41 - «НЕ, которая осуществляет сдвиг числа в к айнес левое иоложоние для выиолпения указанного алгоритма деления, и из схемЕз 32 ОПределсния величииы масщтабиого коэффициента (см. фиг. 7), где 42 -- элемент «НЕ, а 43 - «Н, а также из дешг1фратора постоянного сдвига, аналогично1о дешифратору умножения, со входами которого соединены выходы схс.мы 30, и выходного дсигифратора 3/, собирающего сигналы с выхода схем 33 и 30.

Предмет изобретения

1.Матричное ари.фметическое устроГктво, состоящее из ячеек - сумматоров - вычитатслей, с оцератцв}1ым запоминающим устройст5вом и устройством управлспия, отличающееся тем, что, с целью повышения быстродс1 |ствия и упрощения устройства, каждая ячейка матрицы состоит из /г-разрядных сумматоров и одного выходного ,г-разрядного преобразователя

0 полярности числа, соединеииых каскадно-поразрядио, причем каждая из ячеек матрицы связана с соседними ячейками с помощью четырех информационных каналов и с оперативным запоминающим устройством с помощью

5 входного канала.

2.Устройство по п. 1, от,п1ча1ощссся тем, что, с целью повышения быстродействия прп выполнении операции умножения, в иего введен дешифратор умножения - дешифратор по0стояипого сдвига, выходы которого служат управляющими входами вентилей, связанных с оперативным запо пшающим ycтpoйcтвo.

3.Устройство по п. 1, отличающееся тем, что, с целью повышения быстродействия при

5 выиолнецци операццц деления, в иего введеп дешифратор делеиия, состоящий из логических комбинашюниых схем ввода взвешенного делителя и передачи промежуточного результата, соответствующих каждой линейке матри0цы, и схемы масщтабирования делителя, содержащей схему автоматического сдвига числа, схему определения масштаб11ых коэффициентов, дешифратор иостояи}юго сдвига; логические комбинационные схемы связаны од5ной групиой входов с ячейками матригщ, а другой группой входов - с выходами дегиифратора постоянного сдвига, иодключеиы также к устройству автоматического сдвига числа, входами которого служат выходы ячеек матри0гы, соединениых, кроме того, со схемой определения масштабиого коэффициеига, причем выходы последнего, а также вторая rpyuua вы чодов логических комбинаииониых схем через выходной дешифратор образуют выходы, соотистствующие результатам деления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| Матричное вычислительное устройство | 1978 |

|

SU750484A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

.

3 rAnlU... Л I

J.::

f,

,ffl

/5,

H

НГ - - гяр -- ;

// т т

gp/g $pg HT/g ,,L.,,. .... .

5-5

5

F 1-Ф

г4

0000

78

-D

177/7

-гггЭ-j

1 -+44&Y

f

, ,

/5j

J7

kbLui

„.Ц-J J 1

-0

-:/

Cy .2 А. Ь-Х%Ьag:

«и.,

22 22 i22i; l22

.3

Даты

1969-01-01—Публикация