Изобретение относится к области вычислительной техники и может быть использовано в арифметических устройствах цифровых вычислительных машин.

Для построения известных двоичных сумматоров требуется большое количество оборудования.

Предложенный сумматор отличается от известных тем, что эмиттеры двух транзисторов через обш,ий резистор соединены с источником смещения, база второго транзистора заземлена, а база первого транзистора через резистор подключена к источнику смеш,ения и через диод, включенный в прямом направлении - ко входу схемы, который через резистор соединен с коллектором первого транзистора.

Коллекторы первого и второго транзисторов являются выходами суммы и переноса соответственно.

Такое отличие позволяет упростить схему сумматора и повысить его технологичность.

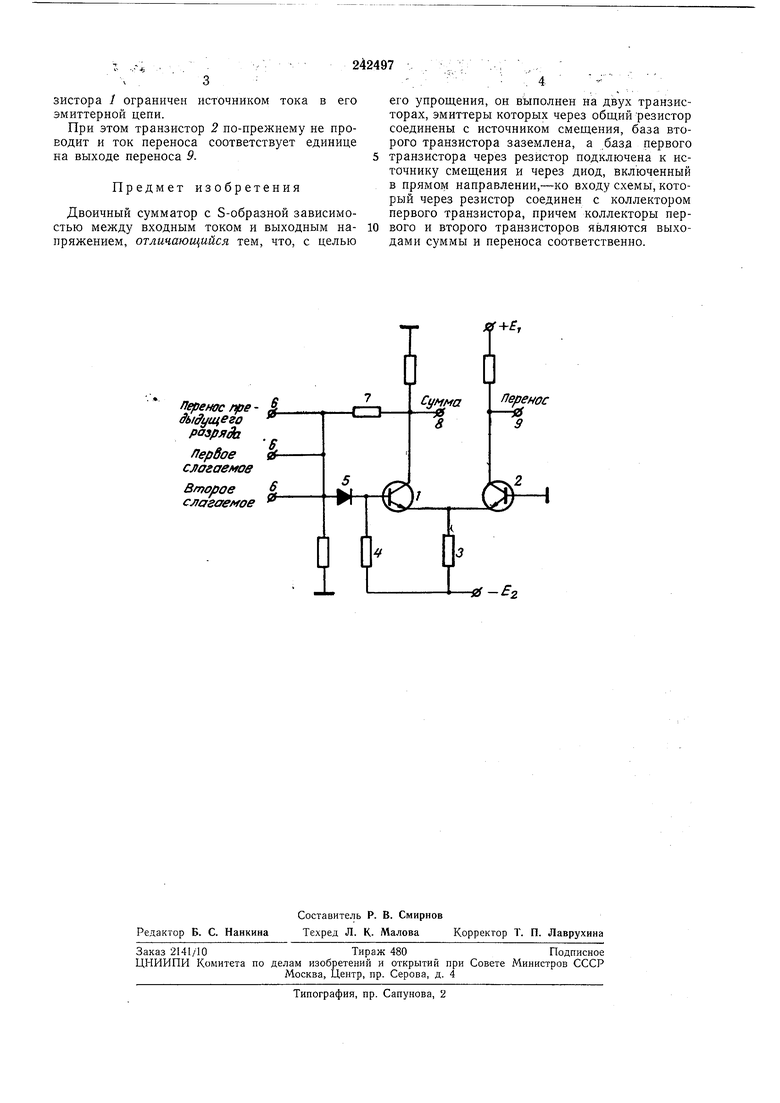

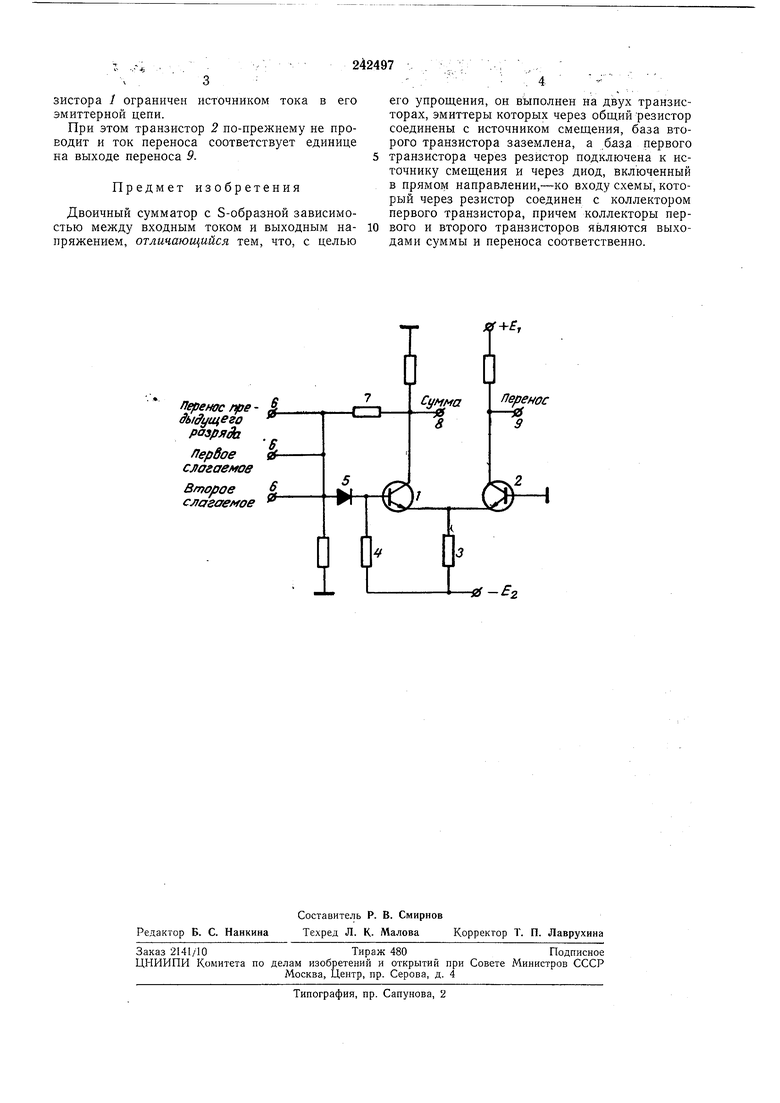

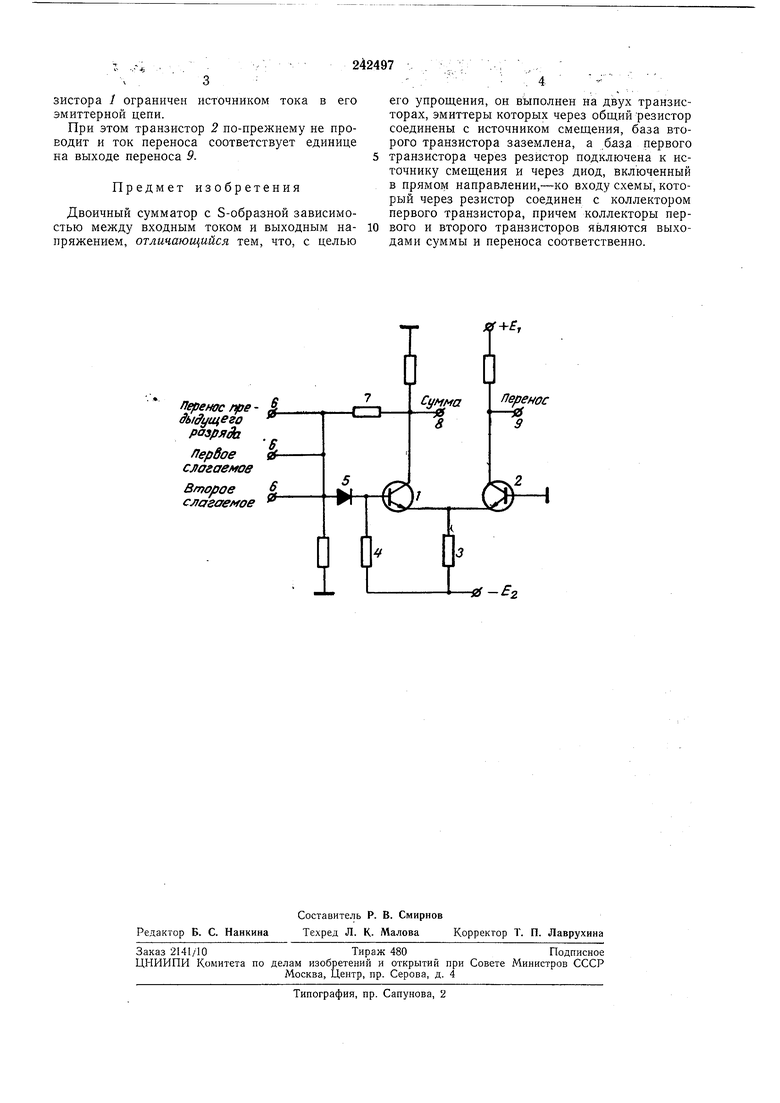

На чертеже приведена схема описываемого двоичного сумматора.

Сумматор выполнен на двух транзисторах / и 2, эмиттеры которых через общий резистор 3 соединены с источником смещения -Е. База транзистора 2 заземлена, а база транзистора 1 через резистор 4 иодключена к источнику смешения и через диод 5, включенный в прямом направлении - ко входу схемы б,

через резистор 7 соединенному с коллектором транзистора 1. Выходами суммы 8 и переноса 9 являются соответственно коллекторы транзисторов / и 2.

Сумматор работает следующим образом.

Если все три входных сигнала (два слагаемых и перенос) равны нулю, то транзистор 1 закрыт, а транзистор 2 открыт. При этом потенциал коллектора транзистора 1 близок к нулю и ток переноса равен нулю. Если хотя бы один входной сигнал отличен от нуля (iвк } то напряжение на коллекторе закрытого транзистора 1 определяется делителем, состоящим из коллекторной нагрузки и резистора 7, и соответствует единице на выходе суммы. При этом транзистор 2 открыт и ток переноса равен нулю.

Если на входе имеется два входных сигнала (вх 2г), то транзистор 1 открывается и потенциал на его коллекторе падает до нуля вследствие протекания коллекторного тока по резистору 7 обратной связи. Транзистор 2 закрывается, ток переноса на выходе сумматора равен /, что соответствует единице переноса.

Отсутствие напряжения на нагрузке означает нуль суммы.

зистора / ограничен источником тока в его эмиттерной цепи.

При этом транзистор 2 но-прежнему не проводит и ток переноса соответствует единице на выходе переноса 9.

Предмет изобретения

Двоичный сумматор с S-образной зависимостью между входным током и выходным напряжением, отличающийся тем, что, с целью

его упрощения, он выполнен на двух транзисторах, эмиттеры которых через общий резистор соединены с источником смещения, база второго транзистора заземлена, а база первого транзистора через резистор подключена к источнику смещения и через диод, включенный в прямом направлении,-ко входу схемы, который через резистор соединен с коллектором первого транзистора, причем коллекторы первого и второго транзисторов являются выходами суммы и переноса соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛНЫЙ ДВОИЧНЫЙ СУММАТОР ФУНКЦИОНАЛЬНОГОТИПА | 1971 |

|

SU299844A1 |

| Усилитель низкой частоты | 1971 |

|

SU576979A3 |

| Триггерный сумматор по модулю два | 2018 |

|

RU2700195C1 |

| Четырехуровневый одноразрядный сумматор | 1982 |

|

SU1095174A1 |

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1971 |

|

SU319077A1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ 2И-ИЛИ/2И-ИЛИ-НЕ | 2024 |

|

RU2829649C1 |

| Триггерный логический элемент 2И/ИЛИ | 2024 |

|

RU2826617C1 |

| Триггерный логический элемент 2И-ИЛИ-НЕ | 2024 |

|

RU2826843C1 |

| МНОГОЗНАЧНЫЙ СУММАТОР ПО МОДУЛЮ k | 2014 |

|

RU2546082C1 |

| Одноразрядный сумматор | 1988 |

|

SU1599854A1 |

Переносffеды ущегоразряда

Первое слагаемое

Второе слагаемое

+,

-sn -EZ

Даты

1969-01-01—Публикация