Изобретеиие относится к области цифровой вычислительной техники, и более точнее к однотактным цифровым арифметическим устройствам, в которых все операции осуществляются за один такт местного управления.

Известно однотактное цифровое арифметическое устройство, содержаш,ее входные и выходные регистры, узел управления, формирователь знаков, несколько множительных блоков для умножения сомиожителей, имеющих формат, меиьший максимального, узел для заключительного сложения, вьшолнениый в виде преобразователя многорядного кода в двухрядный и многоформатного сумматора с распространением переноса.

Целью изобретения является обеспечение возможности одновременного умножения нескольких пар сомножителей немаксимального формата и обеспечение возможности ocyniecTвления многоместных операций суммирования оиерандов и суммирования париых прои.зведений иемаксимального формата.

Для достижения этого предлагаемое устройство дополнительно содержит входные коммутаторы старщей и младшей частей миогоформатного сумматора, входной коммутатор преобразователя многорядного кода в двухрядный, узел коррекции для вычитания «единицы с весом младшего разряда операнда и для суммирования «единиц, соответствующих знаковым разрядам отрицательт1ых слагаемых и имеющих вес их младщего разряда, узел иивертирования двухрядного кода и коммутатор результата; одни входы входных коммутаторов многоформатного сумматора соединены с выходами блоков умножения, другие входы входных коммутаторов старшей части многоформатиого сумматора соединены С выходами преобразователя миогорядного

кода, другие входы входных коммутаторов младщей части миогоформатпого сумматора соединены с выходом узла иивертирования двухрядного кода; входной коммутатор преобразователя многорядного кода соединен с

выходами блоков умножения и выходом узла коррекции, входы которого соединены с выходами знаковых разрядов входных регистров; входы узла инвертирования двухрядного кода соедииеиы с выходами преобразователя

многорядного кода в двухрядный, информационные входы коммутатора результата соединены с выходами младщей и старшей частей многоформатного сумматора, управляющие входы - с выходами знаковых разрядов

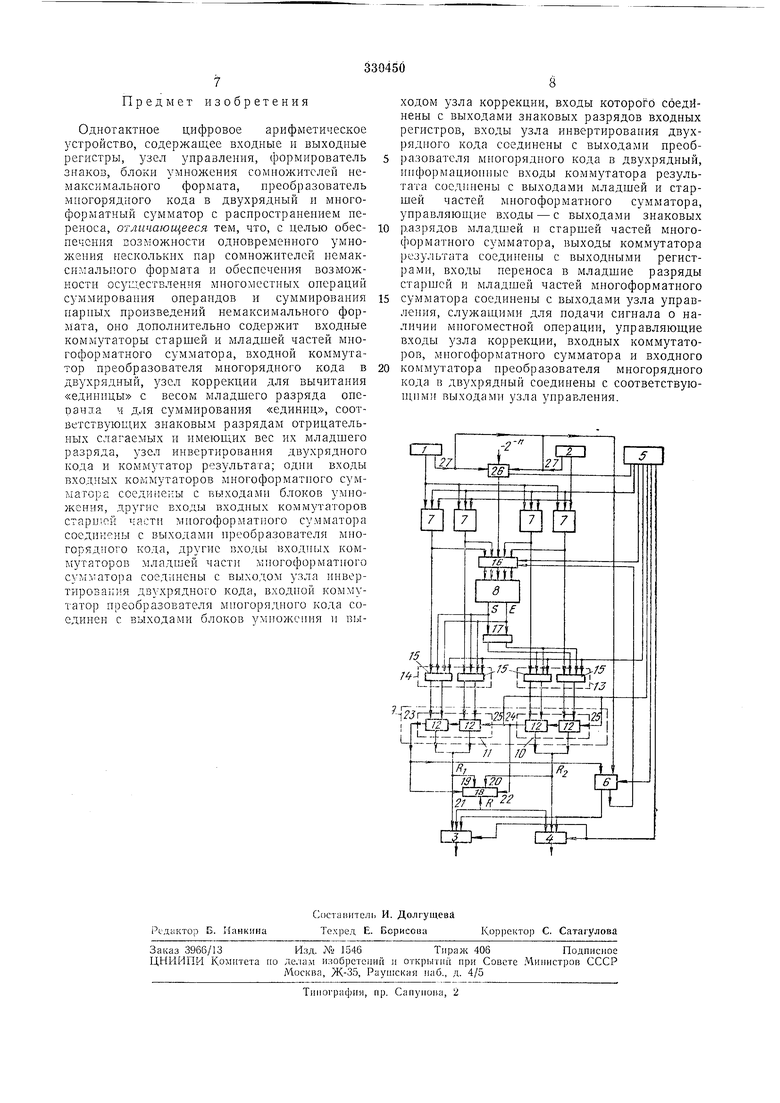

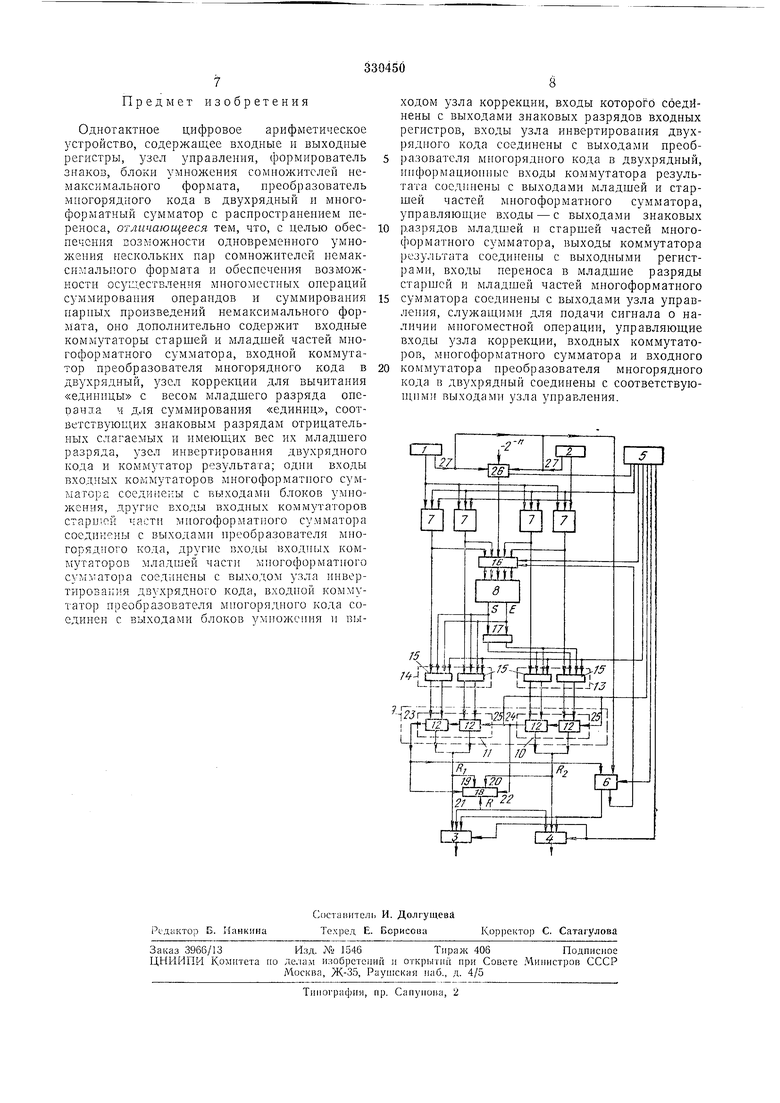

младшей н старщей частей многоформатного сумматора; выходы коммутатора результата соединены с выходными регистрами, входы переноса в младшие разряды старшей и младшей частей миогоформатного сумматора жащйми для подачи сигнала О наличии многоместной операции, управляющие входы узла коррекции, входных коммутаторов, многоформатного сумматора и входного коммутатора преобразователя многорядного кода в двухрядный соединены с соответствующими выходами узла управления. Блок-схема предлагаемого устройства представлена на чертеже. Устройство содержит входные регистры / и 2, выходные регистры 3 и 4, узел 5 управления, формирователь 6 знаков, несколько множительных блоков 7 для умножения сомножителей, имеющих формат, меньщий максимального, узел для заключительного сложения, выполненный в виде преобразователя 8 многорядного кода в двухрядный и многоформатного сумматора 9 с распространением переноса, сумматор 9 разделен на младшую часть 10 и старщую часть 11, каждая из которых разбита на части 12 для сложения и умножения операндов малого формата. На входе младщей части 10 и старщей части И сумматора 9 установлены соответственно коммутаторы 13 и 14, у которых информационные входы соединены с выходами блоков 7 и выходами преобразователя 8, а управляющие входы - с выходами узла 5 управления, служащими для подачи сигналов о форматах операндов в различных операциях. Коммутаторы 13 и 14 разбиты на части 15 для подачи чисел малого формата в части 12 сумматора 9. Выходы блоков 7 поданы на входы частей 15 коммутаторов в однорядном или двухрядном коде. Между выходами блоков 7 и входами преобразователя 8 установлен коммутатор 16 для передачи положительных чисел в прямом, а отрицательных - в инверсном коде со сдвигом, необходимым для умножения операндов максимального формата и для многоместных операций (операции суммирования исходных операндов и операции суммирования произведений исходных операндов) над операндами меньшего формата. Коммутатор 16 управляется формирователем 6 знаков и узлом 5 управления. Коммутаторы 14 старшей части сумматора соединены непосредственно с выходами преобразователя 8, между коммутаторами 13 младщей части сумматора и выходами преобразователя 8 установлены инверторы 17, между выходами обеих частей // и 10 сумматора 9 и выходными регистрами 5 и 4 установлен коммутатор 18 для выбора результата с выходов частей 7 и 11 в прямом коде; информационные входы 19, 20 коммутатора 18 соединены с выходами частей 11 и 10, а управляющие входы 21, 22 коммутатора 18 соединены с выходами 23, 24 знаковых разрядов частей // и 10 сумматора 9. личию многоместной операции. На входе коммутатора 16, соединенного со входом преобразователя 8, установлен узел ко эрекции 26 для вычитания «единицы с весом (2) младшего разряда операнда и для суммирования «единиц, соответствующих знаковым разрядам отрицательных слагаемых и имеющих вес (2-) их младшего разряда, а входы узла 26 соединены с выходами 27 знаковых разрядов входных регистров 7 и .2. Узел 26 представляет собой набор одноразрядных сумматоров, соединенных для сложения и вычитания единиц одинакового веса. Для формирования указанных единиц служат входные цепи узла 26, причем формирование положительных единиц производится по знакам операндов, поступающим со входов 27 регистров / и 2, и по сигналам кода операции, поступающим из узла 5 управления. Отрицательная единица с весом 2-« (т. е. число -2) в дополнительном коде закоммутирована на входах узла 26. Устройство работает следующим образом. Умножение чисел максимального формата Два сомножителя из регистров 1 н 2 подаются в блоки 7, каждый из которых перемножает множимое (или его часть) на группу разрядов множителя. Число групп разрядов множителя зависит от количества блоков 7. Частичные произведения с выходов блоков 7 в однорядном или двухрядном коде подаются через коммутатор 16 в преобразователь 8 со сдвигом, необходимым для сложения этих произведений с соответствующими весами. Преобразователь 8 преобразует многорядный код, образованный частичными произведениями, в двухрядный код произведения. Двухрядный код произведения с выхода преобразователя 8 поступает через коммутаторы 14 в старщую часть // сумматора 9, который преобразует двухрядный код произведения в однорядный. Готовое произведение поступает в регистры 5 и 4. Умножение чисел малого формата В каждом из регистров 1 и 2 располагается столько чисел малого формата, сколько имеется блоков 7. В каждом блоке 7 перемножается одна пара сомножителей малого формата, поступающих из регистров 1 и 2. Таким образом, по одной команде одновременно выполняется столько независимых операций умножения, сколько имеется блоков 7. Произведение с выхода каждого блока 7 в однорядном или двухрядном коде поступает в соответствующую данному блоку 7 часть 15 коммутатора, а из него через части 12 сумматора- в регистры 3 и 4. Е этой операции сумматор 9 разделен на независимые части (сумматоры) 2, каждый из которых служит для получения одного произведения. Многоместные операции К многоместным операциям над операндамирования парных произведений, определяемые формулой

.|«Л-,(1)

и операцпя суммировапия всех исходных операндов, определяемая формулой

-i(a; + c,.),(2)

где R - результат операции; / - номер операнда малого формата в каждом входном регистре У и 2; k - максимальное количество операндов малого формата в каждом входном регистре / и 2; oj-/-и операид в регистре }, Cj-;-й операнд в регистре 2.

Обе эти операции выполняются в предлагаемом устройстве за один такт следующим образом.

При операции суммирования парных произведений каждый блок 7 формирует произведение одной пары сомножителей так же, как и при операции умножения чисел малого формата. Произведеиия из блоков 7 иодаются через коммутатор 16 в преобразователь 8 с одинаковыми весами (при умножепии чисел максимального формата веса нескольких частичных произведений, поступающих в преобразователь 8, неодинаковы).

При этом отрицательные ироизведеиия инвертируются ь коммутаторе 16 и подаются в преобразовател :, 8 в ииверсном (обратном) коде, а неотрицательные произведения пропускаются через коммутатор 16 в прямом коде. В узел 26 (корректор) с весом (2-) младшего разряда произведения поступают положительные единицы, каждая из которых формируется для одного отрицательного произведения, и одна отрицательная единица тоже с весом 2-.

Узел 26 формирует алгебраическую сумму этих единиц, дополнительный код которой через коммутатор 16 иоступает в преобразователь 8. Преобразователь 8 алгебраическп суммирует поступившие в пего коды, преобразуя многорядпый код слагаемых в двухрядный представленный кодом S норазрядной суммы и кодом Е переносов.

Сумма прямых и инверсиых кодов произведений и положительпых единиц, подаваемых в узел 26, представляет собой дополиительиый код суммы парных произведенпй:

R, (2 + I)mod2,(3)

где R определяется формулой (1). (Если , то если , то ). С учетом отрицательной едииицы, подаваемой в узел 26 с весом 2, двухрядиый код на выходе преобразователя 8 соответствует величине

5 + - - 2- (2 + / - 2-) mod2 (4)

через инверторы 17 - в коммутаторы 13 младшей части сумматора.

Из коммутаторов 14 прямой двухрядный код подается в старшую часть // сумматора, а из коммутаторов 13 инверсный двухрядный код - в младшую часть 10 сумматора. Иа входы 25 частей W и 11 сумматора поданы величпны 2- в качестве слагаемых.

Па выходе части // получается величина:

/, S + E + 2-.(5)

Подставим выражение (4) в уравнение (5), получим:

(2 + / - 2-) + 2- (2 + R) mod2. (6)

На вход части 10 каждая из величин S п Е поступает в обратном коде:

с - с - 1 с 9-п

(7)

-обр - - i - - - (8)

обр - i с 2

Здесь считается, что , .

Па выходе части 10 получается величина:

/,z.5o6p + o6p + 2-.(9)

Подставпм выражепия (7) и (8) в уравнение (9):

(1 - 5 - 2-«) + (- - 2-) + 2-

(10)

2(S + E) - .

Подставим выражение (4) в уравнение (10), нолучим:

/,, - 2 - (2 + / - 2-) mod 2 - 2- 2 -

-(2 + /)mod2.(П)

Если , то согласно выражениям (6) и (12)

R,R; ;, -2 -/.(12)

Если R.0, то

/. : :.. 2 /, /.(13)

Прямой код R результата выбирается коммутатором 18 п поступает в регистры 3 или 4. Если , то через коммутатор 18 передается код RI из части 10 сумматора.

При операции суммирования всех исходных операндов в соответствии с выражением (2) на выходе каждого блока 7 формируется сумма одной пары онерандов, прпчем отрицательные оиераиды подаются в блоки 7 в обратпом коде.

В узел 26 с весом (2) младшего разряда операнда подаются положительные единицы, каждая из которых формируется для одного отрицательного операнда.

Через коммутатор 16 в преобразователь 8 без инверсии подаются слагаемые из всех блоков 7 и узла 26. В остальном выполнение этой операции ничем не отличается от выполнения операции суммирования парных

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| СОЮЗНАЯ Iмшшда^'"""ЙИБЛИОТЕК^ | 1972 |

|

SU331386A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения чисел | 1988 |

|

SU1658147A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Арифметическое устройство | 1985 |

|

SU1305662A2 |

| Устройство для умножения | 1977 |

|

SU695364A1 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

Авторы

Даты

1972-01-01—Публикация