(54) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| КОМБИНАЦИОННЫЙ СУММАТОР | 1969 |

|

SU236858A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Устройство для умножения чисел | 1991 |

|

SU1797112A1 |

| Устройство для деления | 1986 |

|

SU1478212A1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| Устройство для умножения | 1979 |

|

SU868751A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 1972 |

|

SU330451A1 |

| Устройство для деления | 1988 |

|

SU1541598A1 |

| Устройство для деления | 1985 |

|

SU1322264A1 |

Изобретение относится к вычислительной технике и может быть использовдно в вычислительном устройстве специализированного процессора.

Известно многовходовоёсуммирующее устройство, содержащее в каждом разряде сумматоры, сгруппированные в линейки, выходы Сумма каждого сумматора младших линеек соединены с входами-сумматоров последующих линеек, шины всех слагаемых каждого разряда подключены к входам сумматоров первой линейки, а выходы переноса сумматоров младших линеек соединены с одним из входов сумматоров последующих линеек соседнего старшего разряда Ц.

Однако этот сумматор обеспечива- , ет параллельное суммирование многих чисел за счет распараллеленного в пространстве перёноса, но множество слагаемых должно быть одного знака, что существенно ограничивает функциональные возможности.

Наиболее близким к предлагаемому является устройство для суммирования, работающее в системе счисления (-2), содержащее блоки поразрядного сложения и блоки выборки первой, второй, третьей и,т.д. ступеней, причем входы слагаемых каждого разряда подключены к блоку поразрядного Сложения, представляющего собой комбинационную логическую схему первого типа, каж- дан из групп выходов которой соответствует условной сумме, аддитивному и субстрактному переносам, причем блок поразрядного сложения слагаемых первого разряда содержит

10 одну группу выходов и выход, соответствующий условной сумме, служит выходом первого разряда полной суммы; выходы блока поразрядного сложения второго разряда подключены к блоку

15 выборки первого уровня, состоящему из трех комбинационных логических схем второго типа, входами каждой из которых служат выходы, соответстГвующие аддитивным переносам,условным

20 ;суммам и субстрактивным переносам, блока поразрядного сложения второго разряда, управляющие входы подключены к выходам, соответствующим аддитив ному и субстрактивному переносам, 25 блока поразрядного сложения первого разряда, выход соответствующий условной сумме, блока выборки первого уровня служит выходом второго разряда полной суммы, а выходы, соответст30вsaoщиe аддитивному и субстрактивному

переносам, служат управляющими входами для блока выборки второго уровня; выходы блока поразрядного сложения последующих четных разрядов подключен к трем блокам выборки первого уровня, каждый из которых состоит из трех комбинационных логических схем второго типа, причем на рход каждой из них подключены выходы соответствующие условным суммам, аддитивным и субстрактивным переносам, а управляющие входы всех трех комбинационных схем второго типа каждого блока выборки первого уровня подключены к выходам, соответствующим субстрлктивному и аддитивному переносамодной из трех групп выходов блока поразрядного сложения предыдущего нечетного разряда; блок выборки второг уровня состоит из четырех комбинационных логических схем второго типа, причем на входы одной из них подключены выходы, соответствующие условHba i суммам, блока поразрядного сложения третьего разряда, а на входы остальных - выходы, соответствующие а 1;дитивный и субстрактивным переносам и условным суммам, служащие выходами трех блоков выборки первого уровня, соответствующих четвертому разряду слагаемых; выходы двух соответствующих логических комбинационных схем второго типа блока выборки второго уровня служат выходами третьего и четвертого разрядов полной суммы, а выходы, соответствующие аддитивным и субстрактивным пареносам, служат управляющими входами для блока выборки третьего уровня, состоящего из шести комбинационных логических схем второго типа, входами котоЕИХ служат выходы, соответствуюka,viG условным суммам блоков выборки первого уровня, а выходы, соответствующие аддитивным и субстрактивным переносам и условньм суммам, блоков

выборки второго уровня; выходы COOTветствующих комбинационных логических схем блока выборки третьего уров ня служат выходами, соответствующими пятому, шестому, седьмому и восьмому разрядам полной суммы 2.

Применение кода по основанию (-2) к алгебраическому сложению чисел позволяет отказаться от фиксированного представления знакового разряда что позволяет производить алгебраи, ческое суммирование чисел с перемен ной разрядностью. Однако известное устройство производит алгебраическое суммирование только двух слагаемых в кодах с основанием (-2). При суммировании Нп -разрядных чисел время работы его сильно возрастает с ростом числа N i

Цель изобретения - повьшение быстродействия при суммировании чисел..

Поставленная цель достигается те что устройство для суммирования, содержащее сумматор чисел по основани (-2), содержит два преобразователя N-рядного кода в двухрядный, преобразователь четырехрядного кода в двухрядный знакоразрядный, преобразователь двухрядного знакоразрядног кода в однорядный знакоразрядный и преобразователь однорядного знакорарядного кода в двухрядный код с основанием (-2), причем входы первого .преобразователя N -рядного кода в двухрядный соединены с входами четных разрядов N суммируемых чисел устройства, а входы второго преобразователя N-рядного кода в двухрядный соединены с входами нечетных разрядов N суммируемых чисел устройства, входы каждого разряда преобразователя четырехрядного кода в двухрядный знакоразрядный соединены с выходами соответствующих разрядов первого и второго преобразователей N-рядного кода в двухрядный, входы каждого разряда преобразователя двухрядного знакоразрядного кода в однорядньй знакоразрядный соединены с выходами соответствующего разряда преобразователя четырехрядного кода в двухрядный знакоразрядный и выходами переноса предьщущего разряда преобразователя двухргщного знакоразрядного в однорядный знакоразрядный, выход каяодого разряда которого соединен с входами соответствующего разряда преобразователя однорядного знакоразрядного кода в двухрядный код с основанием (-2), первый выход каждого разряда которого соединен с первым входом соответствующего разряда сумматора чисел по основанию (-2), а второй выход - с вторым входом соседнего последующего разряда сумматора чисел по основанию (-2).

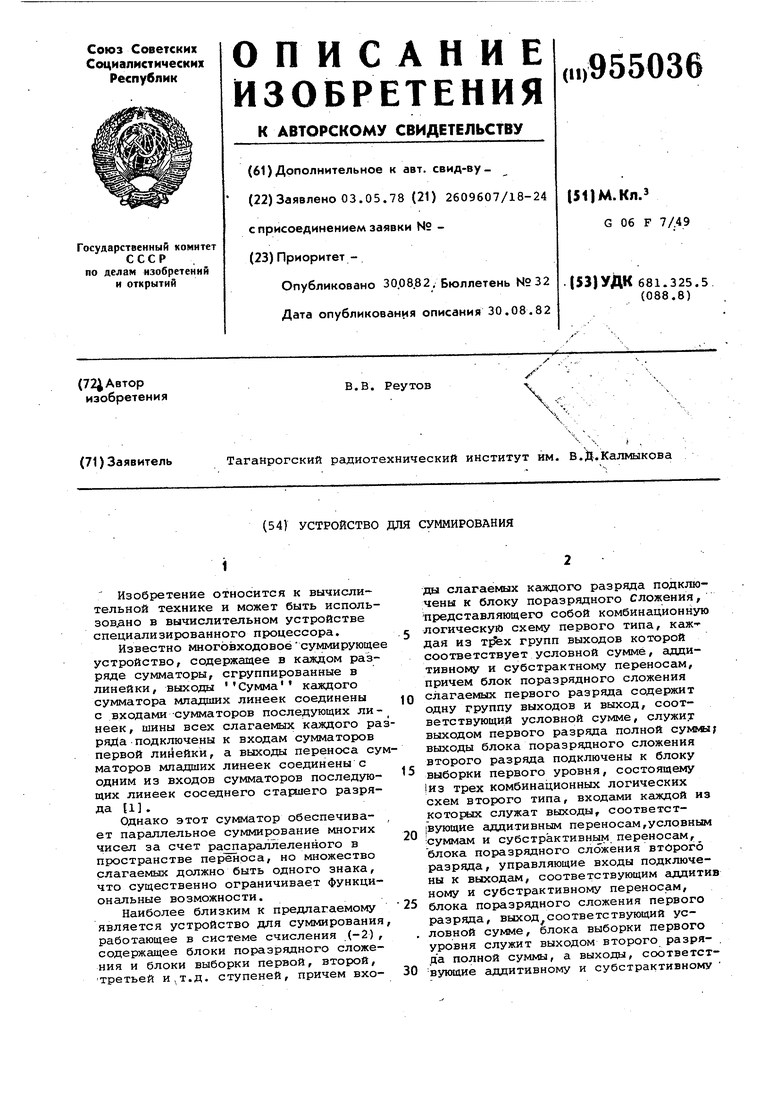

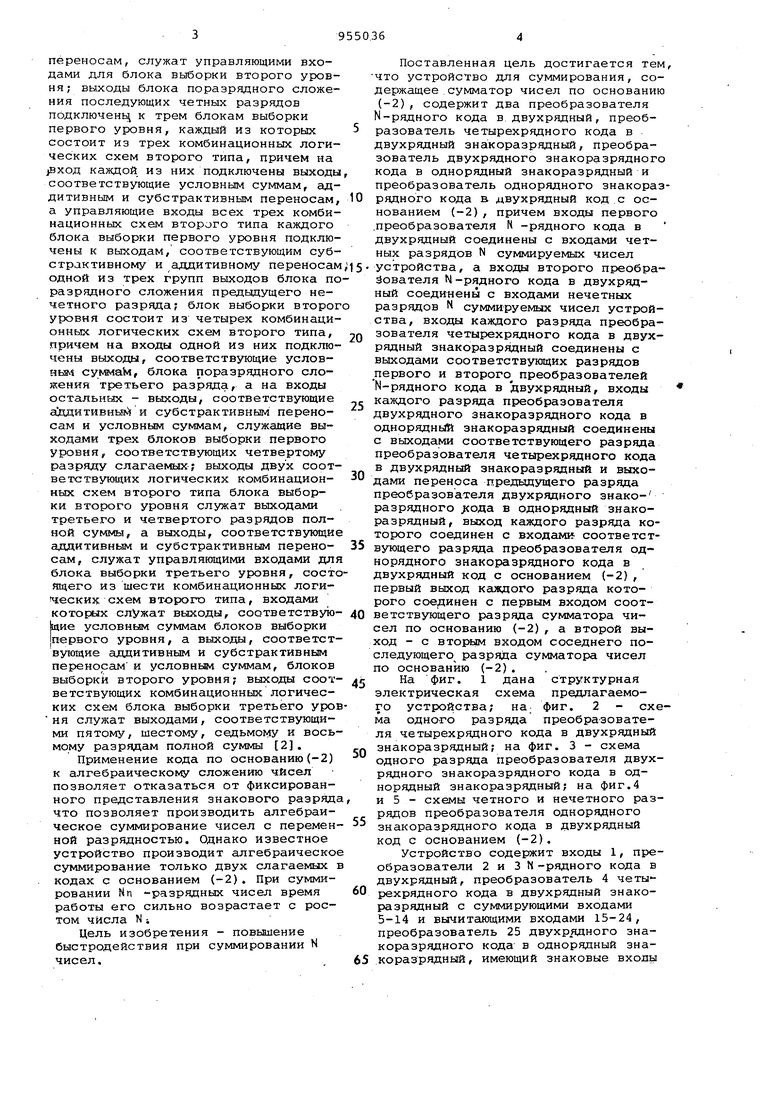

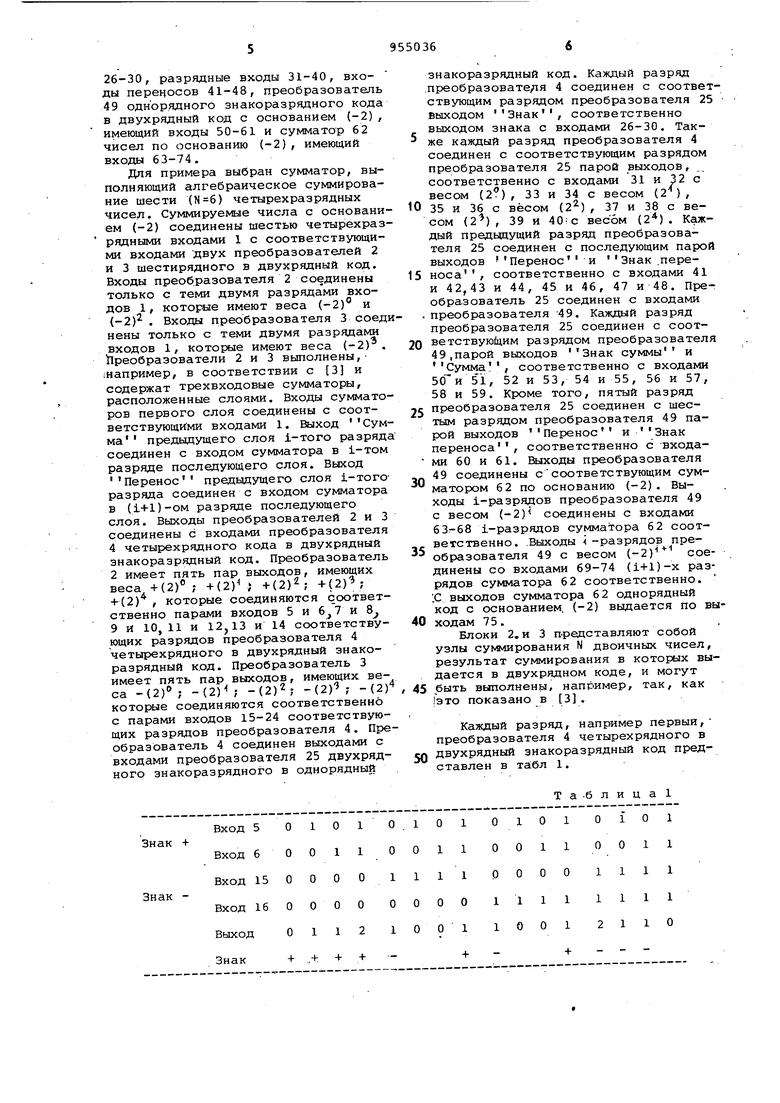

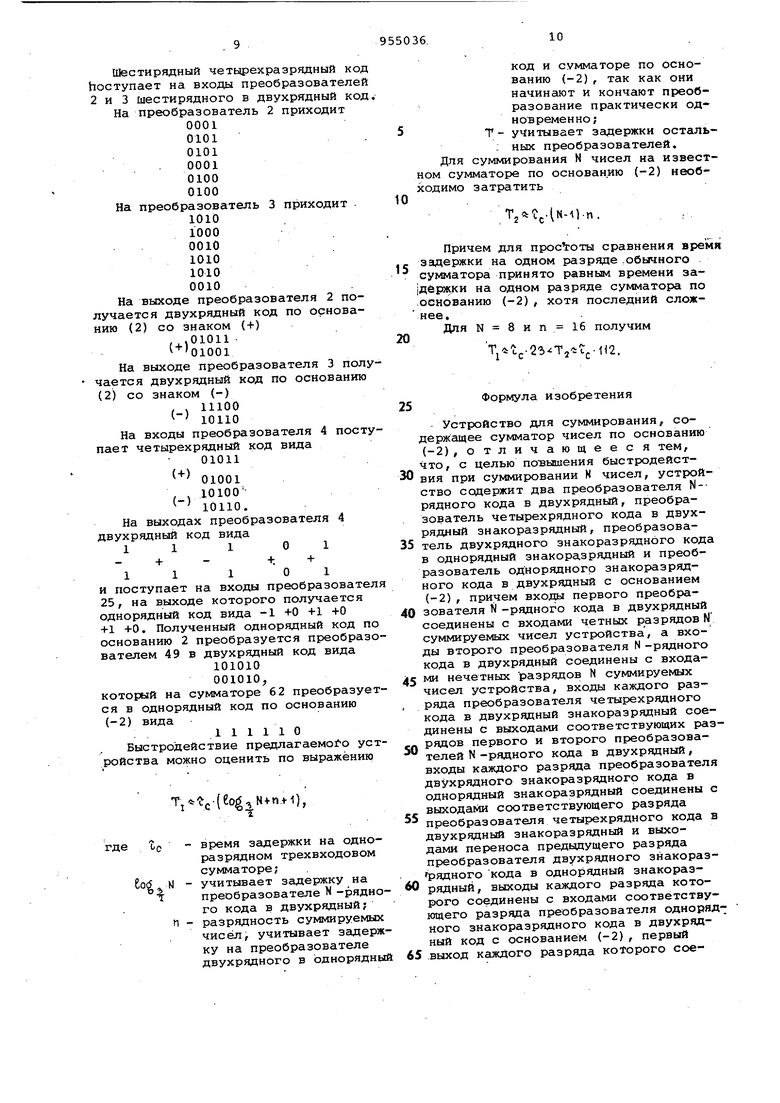

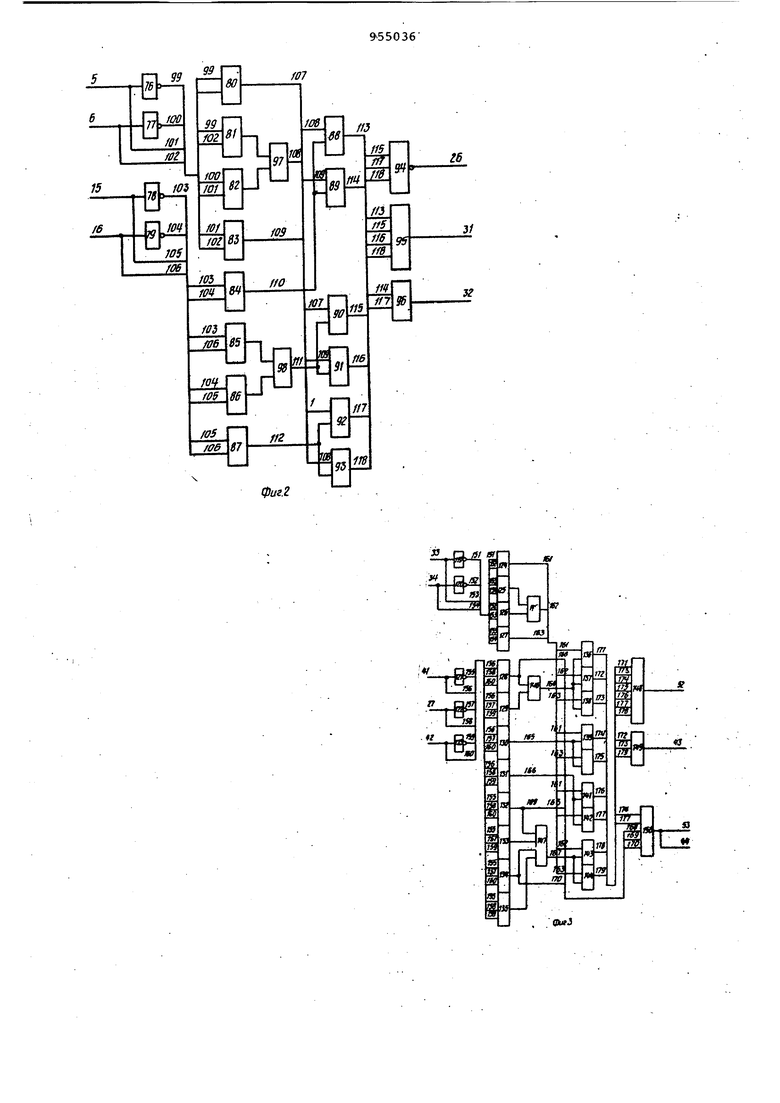

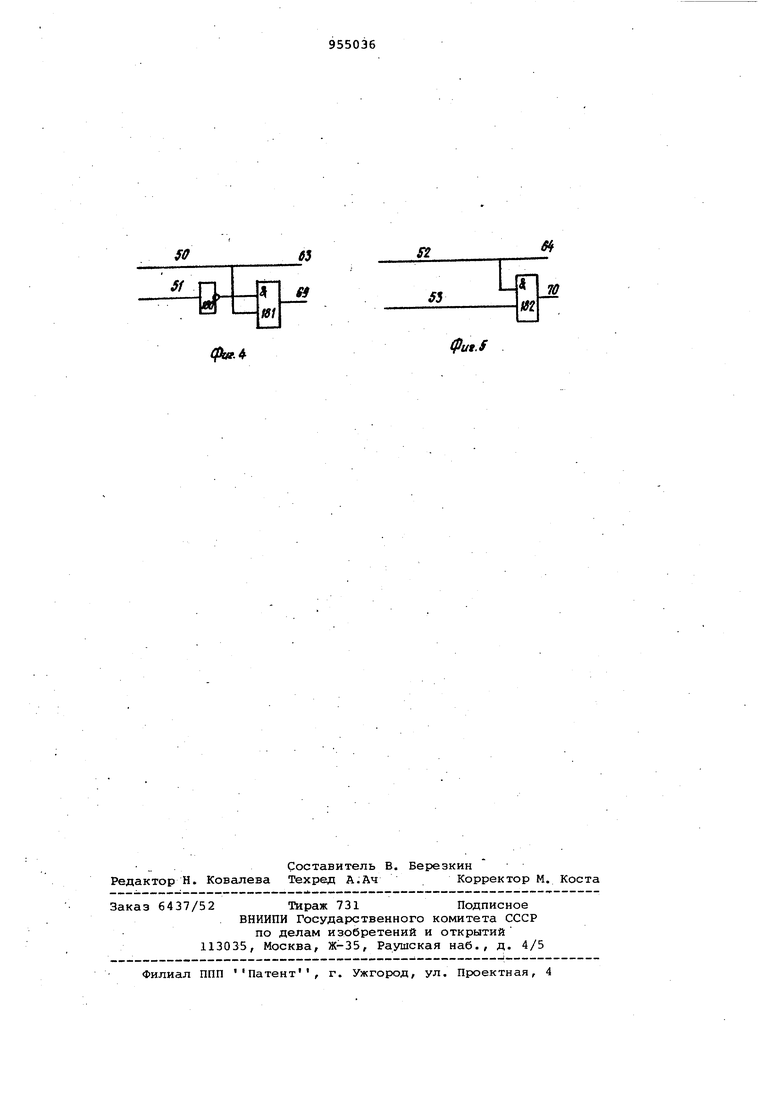

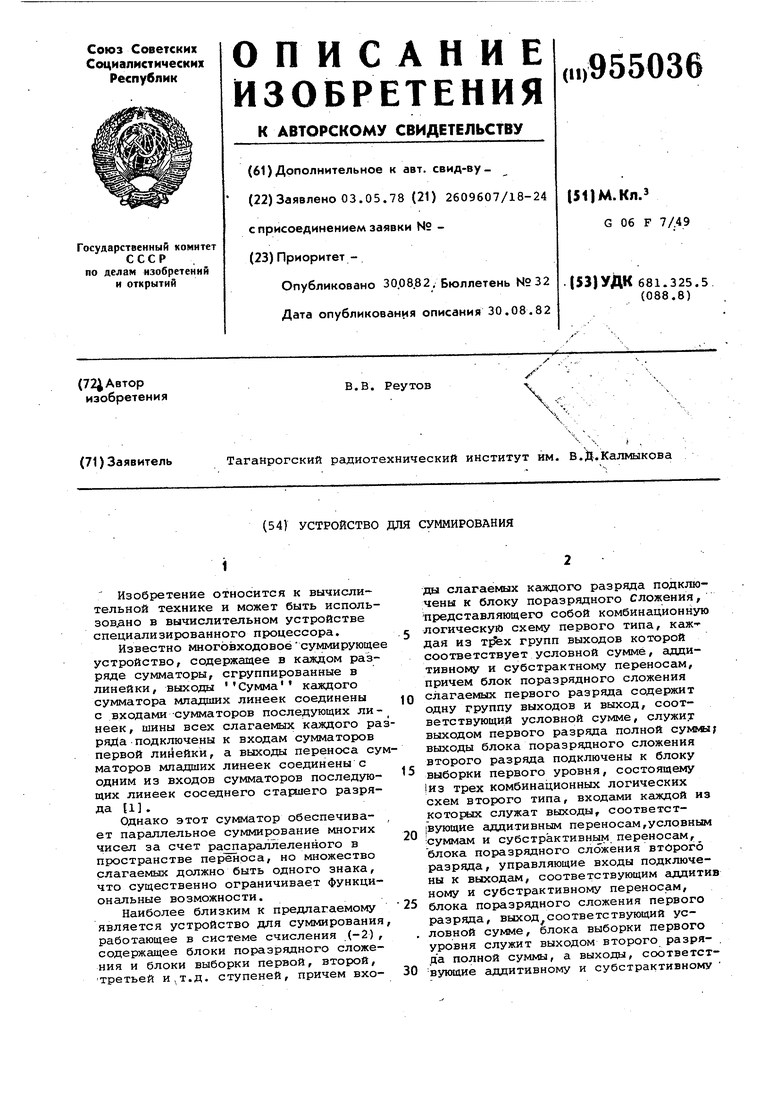

На фиг. 1 дана структурная электрическая схема предлагаемого устройства; на- фиг. 2 - схма одного разряда преобразователя четырехрядного кода в двухрядный знакоразрядный; на фиг. 3 - схема одного разряда преобразователя двухрядного знакоразрядного кода в однорядный знакоразрядный; на фиг.4 и 5 - схемы четного и нечетного разрядов преобразователя однорядного знакоразрядного кода в двухрядный код с основанием (-2).

Устройство содержит входы 1, преобразователи 2 и 3 N-рядного кода в двухрядный, преобразователь 4 четырехрядного кода в двухрядный знакоразрядный с суммирующими входами 5-14 и вычитающими входами 15-24, преобразователь 25 двухрядного знакоразрядного кода в однорядный знакоразрядный , имеющий знаковые вхолы 26-30, разр5щные входы 31-40, входы перечосов 41-48, преобразователь 49 однор.ядного знакоразрядного кода в двухрядный код с основанием (-2), имеющий входы 50-61 и сумматор 62 чисел по основанию (-2), имеющий входы 63-74. Для примера выбран сумматор, выполняющий алгебраическое суммирование шести () четырехразрядных чисел. Суммируемые числа с основани ем (-2) соединены шестью четырехраз рядными входами 1 с соответствующими входами двух преобразователей 2 и 3 шестирядного в двухрядный код. Входы преобразователя 2 соединены только с теми двумя разрядами входов 1, которые имеют веса (-2) и (-2) . Входы преобразователя 3 соед нены только с теми двумя разрядами входов 1, которые имеют веса (-2). Преобразователи 2 и 3 выполнены, :например, в соответствии с 3 и содержат трехвходовые сумматоры, расположенные слоями. Входы суммато ров первого слоя соединены с соответствующими входами 1. йлход Сум ма предыдущего слоя i-того разряд соединен с входом сумматора в 1-том разряде последующего слоя. Выход Перенос предыдущего слоя i-того разряда соединен с входом сумматора в (i+l)-OM разряде последующего слоя. Выходы преобразователей 2 и 3 соединены с входами преобразователя 4 четырехрядного кода в двухрядный знакоразрядный код. Преобразователь 2 имеет пять пар выходов, имеющих веса +(2)°; +(2)) +(2); +(2); +(2) , которые соединяются соответственно парами входов 5 и и 8 9 и 10,11 и 12jl3 и 14 соответствующих разрядов преобразователя 4 четырехрядного в двухрядный знакоразрядный код. Преобразователь 3 имеет пять пар выходов, имеющих веса -(2}° , -(2) ; -(2)2 -(2) ; -(2) которые соединяются соответственно с парами входов 15-24 соответствующих разрядов преобразователя 4. Пре образователь 4 соединен выходами с входами преобразователя 25 двухрядного знакоразрядного в однорядный

Та -б лица 1 знакоразрядный код. Каждый разряд ,преобразователя 4 соединен с соответствующим разрядом преобразователя 25 Выходом Знак, соответственно выходом знака с входами 26-30. Также каждый разряд преобразователя 4 соединен с соответствующим разрядом преобразователя 25 парой выходов, соответственно с входами 31 и 32 с весом (2), 33 и 34 с весом (2), 35 и 36 с весом (2) , 37 и 38 с весом (2) , 39 и 40.:с весом (2). Каждый предыдущий разряд преобразователя 25 соединен с последующим парой выходов Перенос и Знак .переноса, соответственно с входами 41 и 42,43 и 44, 45 и 46, 47 и 48. Преобразователь 25 соединен с входами преобразователя 49. Каждый разряд преобразователя 25 соединен с соответствую цим разрядом преобразователя 49,парой выходов Знак суммы и Сумма, соответственно с входами 5i, 52 и 53, 54 и 55, 56 и 57, 58 и 59. Кроме того, пятый разряд преобразователя 25 соединен с шестым разрядом преобразователя 49 парой выходов Перенос и Знак переноса , соответственно с входами 60 и 61. Выходы преобразователя 49 соединены ссоответствующим сумматором 62 по основанию (-2), Выходы i-разрядов преобразователя 49 с весом (-2) соединены с входами 63:-68 i-разрядов сумматора 62 соответственно. .Выходы ч-разрядов преобразователя 49 с весом (-2)соединены со входами 69-74 (i+l)-x разрядов сумматора 62 соответственно. 1C выходов сумматора 62 однорядный код с основанием. (-2) выдается по выходам 75. Блоки 2.и 3 представляют собой узлы су1 мирования N двоичных чисел, результат суммирования в выдается в двухрядном коде, и могут быть выполнены, например, так, как это показано в 3 . Каждый разряд, например первый, преобразователя 4 четырехрядного в двухрядный знакоразрядный код представлен в 1.

Один из возможных вариантов функциональной схемы, реализующей табл.1, приведен на фиг. 2. Каждый разряд преобразователя 4 содержит элементы НЕ 76-79, элементы И 80-93, элемент ИЛИ-НЕ 94, элементы ИЛИ 95-98. Вхо-. ды 5 и 6и выходы элементов НЕ 80-83 соединены по шинам99-10.2 с входами элементов И 80-83 Входы 15 и 16 и выходы элементов НЕ 78 и 79 соеди- . . нены по шинам 103-106 с входами элементов И 84-87. Выходы элементов И 80

вхо2) +

О О

О О О

1111 122 3 112 + + + . + 01 О 1

О +

и 34) О О 0011 Один из возможных вариантов функ циональной схемы, реализующей табл.2, приведен на фиг. 3. Каждый разряд преобразователя 25 содержит элементы НЕ 119-123, элементы И 124-144, элементы ИЛИ 145-150. Входы 33, 34,. 41, 42, 27 и выходы элементов НЕ 124-144 по шинам 151-160 соединены с входами элементов И 124-135. йаходгл элементов И 124,.127, 130, 131 и элементов ИЛИ 145-147 соединены по шинам 161,167 с входами элементов И 136-144. Выходы элементов И 128 ,132,134,136144 по шинам 168-179 соединены с входс1Ми элементов ИЛИ 148-150,выходы ко83, 84 и 87 и элементов ИЛИ 97 и 9В соединены по шинам 107-112 с входами элементов И 88-93, выходы которых 170 шинам J.13-118 соединены с вхйда;мй элемента ЙЛЙ-НЕ 94 и элементов ИЛИ 95 и 9€, выходы .KOTOptix являются выходами данного разряда преобразователя 4

Каждый разряд, например второй, преобразователя 25 двухрядного знакоразрядного в однорядный знакоразрядный код представлен Б табл. 2.

Таблица2

0 о о о

1111

0112

1001

f

tf

0101

0101 0011 о 01 1 торых являются выходами данного разряда преобразователя 25. На фиг. 4 и 5 показаны варианты выполнения четнога и нечетного разрядов преобразователя 49, например для i О и i .1. Каждый четный разряд преобразователя 49 содержит один -элемент НЕ 180 и один элемент И 181, а каждый нечетный - один элемент И 182. П р и .м-е р. Будем одновременно суммировать числа: -9; -3; +3; -9; -6; +2. Их запись в коде с основанием (-2) приведена ниже

Шестирядный четырехразрядный код Поступает на входы преобразователей 2 и 3 шестирядного в двухрядный код На преобразователь 2 приходит 0001 0101 0101 0001 0100 0100

На преобразователь 3 приходит 1010 1000 0010 1010 1010 0010

На выходе преобразователя 2 получается двухрядный код по орнованию (2) со знаком {+) . .01011. 01001

На выходе преобразователя 3 получается двухрядный код по основанию (2) со знаком (-) , . 11100 10110

На входы преобразователя 4 поступает четырехрядный код вида 01011

01001 , , 10100 10110.

На выходах преобразователя 4 двухрядный код вида

11 1 01 - + - +. +

11 1 01 и поступает на входы преобразовател 25, на выходе которого получается однорядный код вида -1+0+1+0 +1 +0. Полученный однорядный код по основанию 2 преобразуется преобразователем 49 в двухрядный код вида 101010 001010,

который на сумматоре 62 преобразуется в однорядный код по основанию (-2) вида

111110

Быстродействие предлагаемого устройства можно оценить по выражению

(,

Т

де ьо - время задержки на одноразрядном трехвходовом сумматоре;

бой , W - учитывает задержку на Тпреобразователе М-рядного кода в двухрядный; И - разрядность суммируемых чисел, учитывает задержку на преобразователе двухрядного в однорядный

код и сумматоре по основанию (-2), так как они начинают и кончают преобразование практически одновременно;Т- учитывает задержки осталь: ных преобразователей. Для суммирования N чисел на известном сумматоре по основанию (-2) необходимо затратить

Tj vii - b Причем для простоты сравнения время задержки на одном разряде.обычного сумматора принято равным времени задбрж,ки на одном разряде сумматора по основанию (-2) , хотя последний сложнее.

Для N 8 и п 16 получим

Tj4tj..25 T2it|..ll2.

Формула изобретения

25

Устройство для суммирования, содержащее сумматор чисел по основанию (-2), отличающееся тем, что, с целью повышения быстродейстВИЯ при суммировании N чисел, устройство содержит два преобразователя N-рядного кода в двухрядный, преобразователь четырехрядного кода в двухрядный знакоразрядный, преобразователь двухрядного знакоразряднбго кода в однорядный знакора.зрядный и преобразователь однорядного знакоразрядного кода в двухрядный с основанием (-2), причем входы первого преобразователя N-рядного кода в двухрядный соединены с входами четных разрядов N суммируемых чисел устройства , а входы второго преобразователя N-рядного кода в двухрядный соединены с входами нечетных разрядов N суммируемых чисел устройства, входы каждого разряда преобразователя четырехрядного кода в двухрядный знакоразрядный соединены с выходами соответствующих разрядов первого и второго преобразователей N-рядного кода в двухрядный, входы каждого разряда преобразователя двухрядного знакоразрядного кода в однорядный знакоразрядный соединены с выходами соответствующего разряда

преобразователя четырехрядного кода в двухрадный знакоразрядный и выходами переноса предыдущего разряда преобразователя двухрядного знакоразрядного кода в однорядный знакоразрядный, выходы каждого разряда которого соединены с входами соответствующего разряда преобразователя однорядного знакоразрядного кода в двухрядный код с основанием (-2) , первый

.выход каждого разряда которого соедйнен с первым входом соответствующего разреда сумматора чисел по основанию (-2), а второй выход - с втот рым входом соседнего последующего разряда сумматора чисел по основа нию (-2) .

Источники информации, принятые во внимание при экспертизе

Й9

f07

П

J

фиг.г

гб

SO SI

a

I

ff

4

(putJ

Авторы

Даты

1982-08-30—Публикация

1978-05-03—Подача