Предлагаемое устройство относится к области вычислительной техники и может быть использовано в цифровых вычислительных машинах.

Известно устройство умножения чисел в ЦВМ со сдвигом частных произведений вправо, анализом множителя, начиная с младших разрядов, и сохранением младшей части произведения в регистре множителя.

Однако наряду с минимальным количеством оборудования, необходимого для осуш,ествления умножения, в таком устройстве младшая часть произведения получается неточной и выходит за пределы разрядной сетки сумматора, если абсолютные значения разрядов множителя, начиная с младших, равны нулю, а само произведение имеет отрицательный знак.

Предлагаемое устройство отличается тем, что, с целью повышения его точности, в его устройство управления введена логическая схема, входы которой соединены с выходами знаковых разрядов регистра множимого и регистра множителя и с младшим разрядом регистра множителя, а выходы соединены с шинами прямой и инверсной передачи регистра множимого в сумматор.

АУ содержит следующие элементы в цепи: регистр / для хранения множимого; ключи 2 для прямой передачи множимого в сумматор 5; ключи 4 для инверсной передачи множимого в сумматор; шины 5 для передачи частного произведения из сумматора в регистр 6 результата; шины 7, служащие для передачи частного произведения на вход сумматора 3; сдвигающий регистр 8 для хранения и сдвига

множителя; шину 9, служащую для передачи содержимого сдвинутого разряда регистра 6 в старший разряд мантиссы регистра множителя; шину 10 для передачи значения знакового разряда множителя на логическую схему,

вырабатывающую сигналы прямой и инверсной нередачи множимого в сумматор 3; шину // для передачи значения младшего разряда множителя на логическую схему; шину J2 для нередачи значения знакового разряда множимого на логическую схему; логическую схему 13, вырабатывающую сигналы прямой или (и) инверсной передачи множимого в сумматор 3; шину 14, служащую для связи выхода логичесской схемы 13 анализа сомножителей со входом схемы 15 формирования сигнала инверсной передачи множимого в сумматор; шину 16, служащую для связи выхода логической схемы 13 со входом схемы 17 формирования сигнала нрямой передачи множимого в сумма3рующий сигнал, разрешающий, передачу множимого в сумматор; шину 19 для подачи управляюш:его сигнала прямой лередачи множимого в сумматор; шину 20 для подачи управляющего сигнала инверсной передачи множимого в сумматор. Перечисленные операции выполняются при работе устройства следующим образом. Множимое хранится на регистре /. Множитель хранится в сдвигающем регистре 8. В сдвигающем регистре 6 хранится частное произведение. В каждом цикле умножения производится либо прямая и (или) инверсная передача множимого на вход сумматора, либо множимое не передается. На второй вход сумматора по Ц1ине 7 поступает частное произведение, хранимое в регистре 6 и полученное в предыдущих циклах умножения. Сформированная сумма по шинам 5 передается из сумматора в регистр 6, где затем сдвигается на одип разряд вправо. Выпадающий за пределы разрядной сетки регистра 6 разряд частного произведения по щине 9 поступает в старший разряд регистра множителя. Этот разряд до этого был освобожден при сдвиге информации в регистре 8 на один разряд вправо, выполняемом одновременно с суммированием множимого и частного произведения в сумматоре. Логическая схема 13 вырабатывает управляющие сигналы, поступающие на выходы схем формирования прямой или инверсной передачи множимого в сумматор. Сигналы, управляющие этой передачей, поступают в АУ по шинам 19 и 20, раз.решая передачу прямого или инверсного кода мнол имого через ключи 2 и 4 на вход сумматора. Логическая схема реализует логические функции РПК и ик , являющиеся признаками для начала формирования соответственно сигналов прямой и инверсной передачи множимого в сумматор: f „,4нЛ5,у(,)Л(5зн+4н); /ик 5з„Л5д/(5з„)Л(5з„+4„).

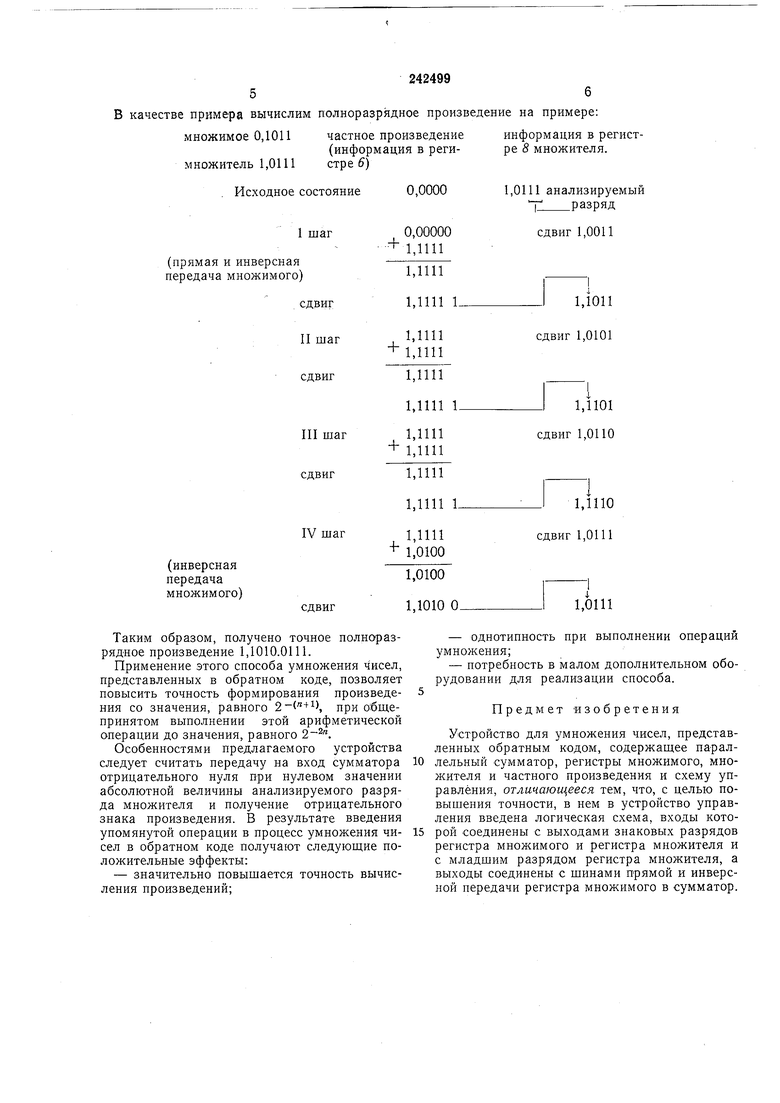

. 4 где Л за -значение знакового разряда множимого;-значение знакового разряда множителя;-значение анализируемого разряда множителя, соответствующего t-му шагу выполнения операции умножения. Таблица истинностей дополняет логические формулы для функций f ПК и /ик Очевидно, что дополнительный член (Взн -бг) Д (5зн + Лн) в формулах для F и и играет корректирующую роль при выполнении умножения, поскольку при осуществлении обычного умножения чисел в обратных кодах функции Р„к и f „к выглядят в следующем виде: пк - -SjH Л i, ик 5з„ЛЙ в случае равенства пк 1 выполняется одновременная передача прямого и инверсного кода множителя на вход сумматора, т. е. подается мащинный (отрицательный) нуль. При этом, если первые частные произведения становятся равными уже не положительному, а отрицательному нулю, при сдвиге частного произведения вправо сдвигаемый в регистр 8 разряд регистра 6 будет иметь (в случае неавнозначных сомножителей) единичное значение в соответствии с точным значением полноразрядного произведения. 5 В качестве примера вычислим

частное произведение (информация в регистре 6)

стояние

информация в регистре 8 множителя.

0,0000

1,0111 анализируемый Ц разряд полноразрядное произведение на примере: 242499 6

| название | год | авторы | номер документа |

|---|---|---|---|

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| Множительно-сдвиговое устройство | 1978 |

|

SU805307A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1972 |

|

SU357561A1 |

| Устройство для умножения | 1989 |

|

SU1732341A1 |

| Устройство для умножения чисел | 1980 |

|

SU920713A1 |

| Устройство для вычисления сумм произведений | 1975 |

|

SU561963A2 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО МАТЕМАТИЧЕСКОЙ МАШИНЫ ПОСЛЕДОВАТЕЛЬНОГО ДЕЙСТВИЯ | 1964 |

|

SU164716A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU369590A1 |

(прямая и инверсная передача множимого)

сдвиг

IIшаг сдвиг

IIIшаг

сдвиг

IVшаг

(инверсная

передача

множимого)

Таким образом, получено точное полноразрядное произведение 1,1010.0111.

Применение этого способа умножения чисел, представленных в обратном коде, позволяет повысить точность формирования произведения со значения, равного 2 ), при обшепринятом выполнении этой арифметической операции до значения, равного 2.

Особенностями предлагаемого устройства следует считать передачу на вход сумматора отрицательного нуля при нулевом значении абсолютной величины анализируемого разряда множителя и получение отрицательного знака произведения. В результате введения упомянутой операции в процесс умножения чисел в обратном коде получают следующие положительные эффекты:

- значительно повышается точность вычисления произведений;

-однотипность при выполнении операций умножения;

-потребность в малом дополнительном оборудовании для реализации способа.

Предмет изобретения

Устройство для умножения чисел, представленных обратным кодом, содержащее параллельный сумматор, регистры множимого, множителя и частного произведения и схему управления, отличающееся тем, что, с целью повышения точности, в нем в устройство управления введена логическая схема, входы которой соединены с выходами знаковых разрядов регистра мнол ;имого и регистра множителя и с младшим разрядом регистра множителя, а выходы соединены с шинами прямой и инверсной передачи регистра множимого в сумматор.

Даты

1969-01-01—Публикация