(SA) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

| Устройство для умножения чисел | 1979 |

|

SU817702A1 |

| Последовательное множительное устройство | 1980 |

|

SU888110A1 |

| Последовательное множительное устройство | 1981 |

|

SU987620A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

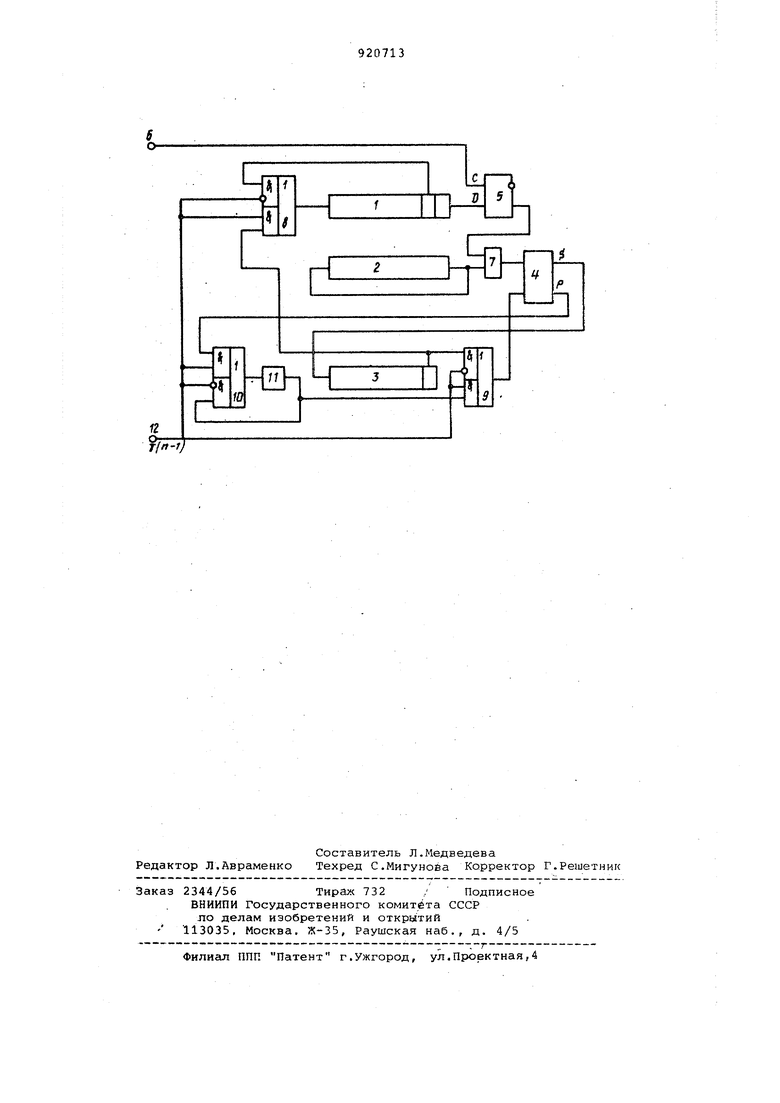

Предлагаемое устройство относится к вычислительной технике и пожет л быть использовано при построении цифровых специализированных вычислитель- ных машин последовательного действия Известно устройство для умножения последовательного типа, содержамее регистры множителя, множигюго и прои ведения, одноразрядный суквлатор последовательного действия, блок управления логические элементы И, и Принцип работы такого устройства не позволяет в полной мере использовать в нем динамические регистры с большой степенью интеграции, что приводит к росту аппаратурных затрат и габаритов. . Наиболее близким по техническому решению к пpeдлaгae юмy являетсяустройство для умножения чисел последо вательного типа, выполненное на дина мических регистрах, содержащее динамические регистры множителя, множимого и произведения, одноразрядный сумматор, D-триггер и логический .эл,е мент Й-ИЛИ и логический элементИ, причем вход синхронизации D-триггера соединен с первой такто-вой шиной, информационный вход D-триг гера соединен а выходом, первого разряда динамического регистра множителя, выход второго разряда которого соединен с первым входом первого логического элемента И-ИЛИ, выход которого соединен с входом диналшческого регистра множителя, выход динамического регистра множимого соеди- нен со своим входом, выходом сугимы одноразрядного сумматорасоединен со входом динамического регистра произведения 21 . Результат умножения - знак и произведение - в таком устройстве формируется через п циклов, разрядность регистров равна п (п - разрядность операндов, включая один знаковый разряд) .. Знак формируется в Отдельном п-м цикле с помощью сумматора, что приводит к усложнению входных схем сумматора и уменьшению быстродействия. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для умножения введены динамический регистр и два логических элемента И-ИЛИ, причем выход 0-триггера соединен с первым входом логического элемента К, втогюй вход которого соединен с выходом динамического регистра множимого, а выход - с первым входом одноразрядного сумматора, второй вход которого соединен с выходом второго лопгческого элемента И-ИЛК, выход переноса одноразрядного сумматора соединен с первым входом третьего логического элемента И-ИЛИ, выход которого соединен с входом динамического регист ра, вторые и третьи входы первого и третьего логических элементов ИИЛИ, первый и второй входы второго логического элемента И-ИЛН объегдине ны и подключены к второй тактовой шине, выход динамического регистра, соединен с третьим входом второго ло гического элемента И-ИЛИ и четвертым входом третьего логического элемента И-ИЛИ, выход динамического ре гистра п-роизведения соединен с четвертыми входами первого и второго логических элементов И-ИЛИ, второй вход первого, третий вход третьего и первый вход второго логических эле ментов И-ИЛИ выполнены инверсными. На чертеже представлена блок-схема устройства. Устройство содержит ()-разрядвые регистры множителя 1, множимого 2 и 2(п-1)-разрядный регистр произведения 3, {п-1)- разрядность мантисс сомножителей}, одноразрядный сумматор последовательного действия D-триггер 5, D-вход которого подключен к выходу первого разряда регист,ра 1, первая тактовая шина б, логический элемент И 7, логические элементы И-ИЛИ 8, 9 и 10, динамический регистр 11, вторая тактовая шина 12 Вход синхронизации D-триггера 5 соединен с первой тактовой шиной 6, информационный вход D-триггера 5 сое динен с выходом первого разряда динамического регистра мнол ителя 1, выход второго разряда которого соеди нен с первым входом логического элемента И-ИЛИ 8, выход которого соединен со входом динамического регистра (ителя 1, выход динамического регистра множимого 2 соединен со сво им входом, выход суммы одноразрядного сумматора 4 соединен со входом динамического регистра произведения 3, выход D-триггера 5 соединен с пер вым входом логического элемента И 7 второй вход которого соединен с йыходом динамического регистра множимого 2, а выход .- с первым входом одноразрядного сумматора 4, второй Бход которого соединен с выходом логического элемента И-ИЛИ 9, выход переноса одноразрядного сумматора 4 соединен с первым входом логического элемента И-ИЛИ 10, выход которого соедиЕ ен с входом динамического регистра 11,,вторые и третьи входы ло гических элементов И-ИЛИ В и 10, пер вый и второй входы логического элеме та И-ИЛИ 9 объединены и подключены к второй тактовой 1аине 12, выход динамического регистра 11 соединен с третьим входом логического элемента И-ИЛИ 9 и четвертым входом логического элемента И-ИЛИ 10, выход динамического регистра произведения 3 соединен с четвертыми входами логических элементов И-ИЛИ 8 и 9, первый, второй,третий входы соответствующих логических элементов И-ИЛИ 9, 8 и 10 выполнены инверсньв.и. Устройство работает следующим образом. Работа устройства осуществляется по циклам, равным Едиклам циркуляции информации в регистрах 1, 2 и 3, длительность которых равна (п-1) тактов Считаем,ЧТО когда на выходах первого разряда динамических регистров 1 и 2 в режиме хранения находятся первые разряды записанных в них чисел, на первой тактовой шине 6 появляется еддиничный сигнал Т 1, соответствующий началу цикла. Когда на выходах первого разряда регистров 1 и 2 находятся последние разряды чисел, на рторой тактовой шине 12 появляется единичный сигнал Т (п-1) , соответствующий концу цикла. Умножение мантисс двух чисел осуществляется за (п-1) циклов. Результат умножения представляется 2-(п-1)-разрядной майтиссой произведения. В исходном состоянии в регистрах 1 и 2 записаны пряглые коды мантисс множителя и множимого младшими разрядами вперед, в регистре 3 - нулевой код. Рассмотрим работу устройства в i-M цикле. В начале i-ro цикла состояние узлов следующее. В регистре 1записан сдвигнутый на (i-1) - разряд вправо код множителя, в регистре 2- код множимого,В регистрах ii и 3 сформированы (п-3.) старших разрядов, а в (1-1) старших разрядах регистра 11 - (i-1) младших разрядов (1-1)-й суммы частичных произведений. В такте Т 1 на D-триггер 5 записывается i-H цифра множителя. Очередная i-я сумма частичных произведений формируется следующим образом. На один из входов cyMrviaTopa 4 через элемент И 7, управляе1 1ый триггером 5, поступает код множимого, умноженный на i-ю цифру множителя. Цепь циркуляции регистра произ-ведения 3 при умножении замыкается через сумматор 4 и содержит (п-2) разряда, что обеспечивает сдвиг вправо старших (п-1) разрядов (i- 1)-и суммы частичных произведений и ее сложение с кодом, поступающим на первый вход сумматора 4. В первых (п-2) тактах i-го цикла цепь циркуляции регистра 11 коммутируется -на режим хранения записанного в нем старшего разряда (i-I)-n cyMi-TtJ частичных про изведений. В такте Т (п-1) его информация вьщается на сумматор, а на вход регистра 11 поступает значение старшего разряда (перенос) i-и суммы Старший разряд i-n суммы частичн произведений всегда равен переносу, вырабатываемому при сложении него разряда мантиссы множимого со сдвинутой вправЪ U- 1)-и суммой час тичных произведений. Сформированная таким образом i-я сумма частичных произведений записывается в регистр З..Цепь циркуляции регистра 1 комму тируется с выхода его второго разря да, что обеспечивает сдвиг множител в каждом цикле на один разряд вправо В такте Т (п-1) на выходе первого р ряда регистра 3 появляется К-я цифра 1-й суммы частичных произведений являющаяся i-й цифрой младших разрядов произведения. Подача ее на вход сумматора блокируется, -а в такте Т (п-1)через элемент И-ИЛИ 8 Она записывается в освобождающийся при сдвиге вправо разряд регистра 1. Таким образом, после выполнения :(п-1) -циклов в регистре 1 формируется (п-1) младших, а в регистрах 11 и 3 - (п-1) старших разрядов произведе ния. В режиме хранения цепи циркуляции регистров 11 и 3 объединяются и они рассматриваются как один (п-1)-разрядный регистр результата. Знак результата в предлагаемом устройстве необходимо формировать отдельной схемой, например, с помощью Т-триггера при приеме операндов. По сравнению с известным в данном устройстве для умножения.разрядность динамических регистров которого на единицу меньше, получается выигрыш в оборудовании, определяемый величиной L 3Wp где WP - аппаратурные затраты на один разряд динамического регистра. При использовании устройства в специализированных ЦВМ с сок.ращенным (п-1)-тактным машинным циклом упрощается блок местного управления умножением, так как цикл схемы устройства, совпадает с машинным циклом СЦВМ, Такой сокращенный машинный цикл может быть в СЦВМ с диапазоном представления входных, выходных и промежуточных переменных, ограниченН.ОМ только положительными числами, В таких ЦВМ обрабатывать знаки чисел нет необходимости, в памяти хранятся только (п-1)разрядные мантиссу чисел, Цикл работы известного устройства составляет п тактов и для работы в вычислительном устройстве с сокращенным машинным циклом требуются дополнительные затраты при построени:и блока местного управления, а также умножение в нем осуществляется за п тактов, В данном устройстве произведение формируется на (п-1) тактов , Таким образом, время выполнения операции умножения уменьшается на 2п-1 такт, т.е. быстродействие увепичивйется, Формула изобретения Устройство для умножения чисел, содержащее динамические регистры множителя, множимого и произведения, D-триггер, одноразрядный сумматор, логический элемент И-ИЛИ и логический элемент И, причем вход синхронизации О-триггера соединен с первой тактовой шиной, информационный вход р-триггера соединен с выходом первого разряда динамического регистра множителя , выход второго разряда которого соединен с первым входом первого логического эл&мента И-ИЛИ,выход которого соединен с входом динамического регистра множителя, выход динамического регистра множимого соединен с своим входом, выход суммы одноразрядного сумматора соединен с входом динамического регистра произведения, отличающееся тем, что с целью повышения быстродействия, в него введены динамический регистр и два логических элемента И-ИЛИ. причем выход D-триггера соединен с пер;вым входом логического элемента И. ; второй вход которого соединен с вы- ходом- динамического регистра множимого, а вЕЛход - с первым входом одноразрядного сумматора,второй вход которого соединен с выходом второго логического элемента И-ИЛИ, выход переноса одноразрядного сумматора соединен с первым входом третьего логического элемента И-ИЛИ, выход которого соединен с входом динамического регистра, вторые и третьи входы первого и , третьего логических элементов И-ИЛИ, первый и второй входы второго логического элемента И-ИЛИ объединены и подключены к второй тактовой шине, выход динамического регистра соединен с третьим входом второго логического элемента И-ИЛМ и четвертым входом третьего логического элемента И-ИЛИ, выход динамического регистра произве-. дения соединен с четвертыми входами первого и второго логических элементов И-ИЛИ, второй вход первого, третий вход третьего и первый вход второго логических элеентов И-ИЛИ выполнены инверсными. Источники информации, ринятые во внимание при экспертизе 1. Авторское свидетельство СССР № 608157, кл,С Об F 7/39. 1978, 2 Авторское сви,14етельство. СССР о заявке № 2761786/24-18, кл. G06 F.7/52, 1979 (прототип)

Авторы

Даты

1982-04-15—Публикация

1980-07-04—Подача