Предлагаемое устройство относится к области вычислительной техники и может быть использовано в универсальных вычислительных машинах.

Известны устройства для суммирования и вычитания чисел .коМбинационного типа со сквозным распространением переноса и заемо.в, состоящие из суммирующие-вычитающих разрядов, содержащих полусумматор частичной суммы, Полусумматор разрядной суммыразности, логический узел и коммутатор.

В известных суммирующих-вычитающих устройствах наблюдается повышенный расход элементов, в частности транзисторов, изза необходимости формирования в каждом разряде не только прямых кодов частичной суммы S, переноса Р и заемов , 2-, но и их обратных кодов S, Р, , Z.

Предлагаемое устройство отличается тем, что оно выполнено в виде двух последовательно чередующихся суммирующе-вьгчитающих разрядов, в одном из которых шины прямых кодов первого и второго чисел соединены с первыми и вторыми входами логического узла и полусумматора частичной суммы, имеющего только один выход, подсоединенный к первому входу полусумматора разрядной суммы-разности. Шины обратных кодов первого и второго чисел соединены- с третьими и

четвертыми входами полусумматора частичной суммы и логического узла. Во втором разряде щина обратного кода первого числа соединена с первыми входами полусумматора частичной сумимы и логического узла, щина обратного кода второго числа соединена с четвертым входом полусумматора частичной суммы и вторым входом логического узла. Шина прямого кода первого числа соединена с третьими входами полусумматора частичной суммы и логического узла, шина прямого кода второго числа соединена со вторым входом полусумматора частичной суммы и четвертым входом логического узла, второй 5 вход полусумматора разрядной суммы-разности соеяинен с единственным выходом коммутатора.

Это повыщает быстродействие и надежность устройства.

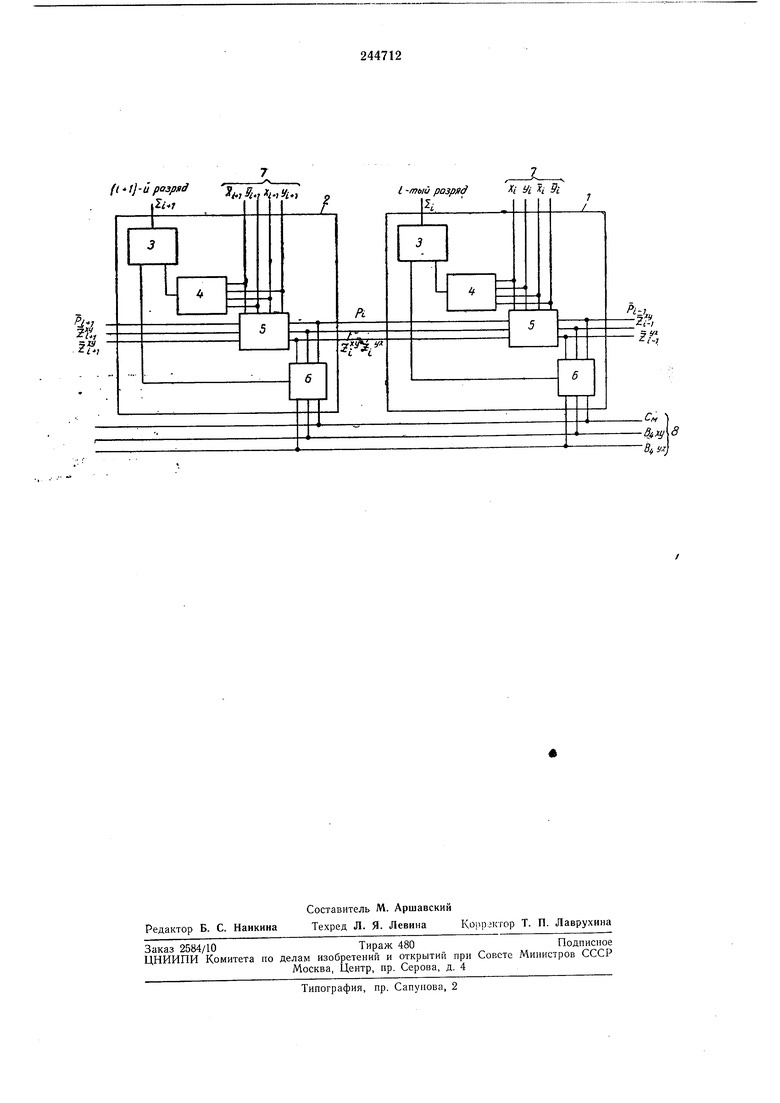

На чертеже изображена бло.к-схема предлагаемого устройства на два разряда (i-тый и (/+ 1)-й).

В состаВ суммирующе-вычитающего устройства входят суммирующе-вычитающий разряд / первого вида, суммирующе-вычитающий разряд 2 второго вида, полусумматор

Суммирующе-вычитающее устройство выполнено из чередующихся между собой суммирующе-вьгчитающих разрядов иервого и второго Вида, о.бщее количество которых равно п.

В каждом суммирующе-вычитающем разряде управляющие входы коммутатора 6 соединены с упра1вляющими шинами 8. Выходы переноса и заемов логического узла 5 младшего разряда соединены со входами переноса и заемов логического узла и коммутатора .последующего, более старшего разряда; выходы коммутатора и полусумматора 4 частичной суммы соединены с различными входами полусумматора 3 разрядной суммыразности.

В суммирующе-вычитающем разряде 1 первого вида, например в г-том, шины орямых кодов i-тых разрядов лервото и второго чисел соединены а- первыми и вторыми входами полусумматора частичной суммы и логического узла 5 соот1ветственно; шины обратных .кодов -тых разрядов первого и второго чисел соединены с третьими и четвертыми входами полусумматора частичной суммы и логического узла соответственно. В суммирующе-вычитающем разряде второго вида, например в (i)-yi разряде, шина обратного кода (f+ 1)-го разряда первого числа соединена с первыми входами .полусумматора 4 и логического узла 5, шина обратного кода (i+ 1)-го разряда второго числа соединена с чепвертым входом .полусумматора частичной суммы 4 и вторым входом логического узла 5, шина прямого кода (/+ 1)-го разряда первого числа соединена с третьими входами полусумматора 4 частичной суммы и логического узла, шина прямого кода (i + 1)-;го разряда второго числа соединена со вторым входом -полусумматора частичной суммы 4 и четвертым входом логического узла 5.

Предлагаемое сум миру юще-вычитающее устройство работает следующим образом.

В суммирующе-вычитающем разряде первого вида, например в f-том разряде, из поступающих по разрядным шина.м 7 на вход нолусумматора 4 частичной суммы .прямых и обратных кодов г-тых разрядов двух чисел Ui y-i В полусумматоре 4 формируется прямой код частичной суммы Si данных разрядов этих чисел в соответствии с выражением:

Si + .

Этот сигнал подается на один из входов полусумматора 3 разрядной суммы. На другой день вход полусумматора 3 с выхода коммутатора 6 подается сигнал С, который формируется в коммутаторе из сигналов Я(1, Zfli. под воздействием управляющих сигналов С„, Btxy, , поступающих с управляющих шин

5, ,в соответствии с выражением:

Ci ,xy + ZiliB,yx.

Смысл этого выражения заключается в том, что при наличии одного из управляющих сигналов, определяемого производимой

арифметической операцией сложением или вычитанием и соотношением чисел по абсолютной величине, на выходе коммутатора 6 появляется сигнал С, равный либо прямому каду переноса Pt-i-, либо одному из прямых

кодов заемов Z}L 2/1ь поступающих из соседнего, младшего (/-1)-го разряда.

Полусумматор разрядной суммы-разности из поступающих на его входы прямого кода частичной суммы Si и сигнала с выхода коммутатора 6 С, являющегося прямым кодом одного из сигналов или переноса Pi-i или одного из заемов , ZlLi в зависимости от производимой арифметической операции - сложения или вычитания, формирует сигнал

, который является либо прямым кодом разрядной суммы, либо прямым кодом разрядной разности i-тых разрядов двух чисел с учетом переноса или заемов из младшего (i-1)-го разряда, в соответствии с вырал еиием;

Е, S,Q + S, + С,.

-Из прямых и обратных кодов t-тых разрядов обоих чисел Xi, у, х, у, поступающих на входы логического узла 5 с разрядных шин 7, и обратных кодов переноса Pi-i и заемов , Z;li, поступающих из младшего (i-1)-го разряда, логическим узлом 5 формируются прямые коды переноса Р/ и заемов ZP, Zf в соответствии с выражениями:

PI iJi + iPi-i + yiPi-i,

zf 3

Zf ,y, + x;zfli+i/,Zrib

С соответствующих выходов логического узла 5 прямые коды переноса Р и заемов ZP, Zr передаются в последующий, более старший, (1+1)-й разряд.

iB ((-f-l)-M разряде, являющемся суммирующе-вычитающим разрядом 2 второго вида, из прямых и обратных кодов (i + 1)-х разрядов двух чисел , , , , поступающих на вход полусумматора 4 частичной суммы по разрядным шинам 7, в полусумматоре 4 ф ормируется обратный код частичной суммы Si,i данных разрядов этих чисел в соответствии с выражением:

Этот сигнал подается на один из входов полусумматора 3 разрядной суммы. На другой вход полусумматора 3 с выхода коммутатора 6 подается сигнал Сгчь -который формируется .в ком.мутаторе из сигналов PI, Z, ZT ;под Воздействием управляющих сигналов С„, , Влух, поступающих с управляющих :11шн S, 3 соответствии с выражением:

Ci , РгС„ + ZP5,(/ + zrB,yx.

Смысл этого выражения заключается в том, что При наличии одного из управляющих сигнало-в, определяемого производимой арифметической операцией - сложением или вычитанием - и соотношением чисел по абсолютной величине, на выхоае коммутатора 6 существует сигнал С/ i равный либо обратному -коду переноса Pj либо обратному коду одного из заемов Zt, Zf поступающих из соседнего, младшего г-того разряда.

Полусумматор 3 разрядной суммы-разности -из поступающих на его входы обратного кода частичной суммы Si-, i и сигнала с выхода коммутатора 6 Ci.i, являющегося либо обратным кодом переноса PI, либо обратным кодом одного из заемов 2/ ,Zf в зависимости от производимой арифметической операции - сложения или вычитания, формирует сигнал гчь который является или прямым кодом разрядной суммы, или прямым кодом разрядной разности (/-f-l)-x разрядов двух чисел с учетом переноса или заемов из младшего /-того разряда, в соот;ветствии с выражением:

-гЧ1 - Sfi Si + i + Сг + ь

логическое значение -которого эквивалентно выражению (1).

Из поступающих с разря-дных шин 7 на входы логического узла 5 прямых и обратных кодов (i+1)-х разрядов обоих чисел /.. i, г/г ь fi ii yi и прямых КОДОВ нереносз PI и заемов Z}, Zf из младшего г-того разряда логическим узлом 5 формируются обратные коды переноса P;: 1 и заемов Z}ti Zf11 в Соответствии с выражениями:

. /(-, 1 -Ь Xi..iPi + yi,

Z. гT V

1л.1 - Xi4 If/Ml + Xi Zi + г/г. iZ,;

Zfi 1 xi, , 1 + д:/.: 1 Zf + yt, 1 Zf.

v соответствующих выходов логического

узла 5 обратные -коды переноса Ягц и зае-мов Zi+i, Zf+i передаются в после-дующий, более старший (г-|-2)-й разряд.

Такая последовательность чередования суммирующе-вычитающих разрядов первого и второго ви-дов, лде в разря-дах -первого вида полусумматором 3 разрядной суммы и логическим узлом 5 формируются прямые коды частичной суммы, переноса и заемов соответственно, а в разрядах второго вида аналогичными узлами формируютея обратные коды частичной суммы, переноса и заемов, сохраняется во -всех разрядах суммирующего устройства.

Предмет изобретения

Устройство для суммирования и вычитания чисел комбинационного типа со сквозньгм распространением переноса и заемов, состоящее из суммирующе-вычитающих разрядов,

содержащих полусумматор частичной суммы, полусумматор разрядной суммы-разности, логический узел и коммутатор, отличающееся тем, что, с целью сокращения элементов, повышения быстродействия и надежности, оно

выполне-но в виде двух последовательно черсдующ.ихся суммирующе-вычитающих разрядов, В о-дном из которых :шины Прямых кодов первого и второго чисел соединены с первыми и вторыми входами логического узла и

полусумматора частичной суммы, имеющего только один выход, подсоединенный к первому входу полуеумматора разрядной суммыразности, а шины обратных кодов первого и второго чисел - с третьими и четвертыми

входами полусумматора частичной суммы и логического узла, а во втором шина обратного кода первого числа соединена с первыми входами полусумматора частичной су.ммы и логического узла, шииа обратного кода второго числа соединена с четвертым входом полусумматора частичной суммы и вторым -входом логического узла, шина прямого кода Первого числа соединена с третьими входами полусумматора частичной сум.мы и логического узла, шина прямого кода второго числа соединена со вторьгм входом -полусумматора частичной суммы и четвертым входом логического узла, второй вход полусумматора разрядной суммы-разности соединен с едияственным выходом коммутатора.

{i i -upa3p d % - :;ir:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания десятичных чисел | 1975 |

|

SU607216A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления чисел | 1985 |

|

SU1247862A1 |

| Устройство для деления чисел | 1985 |

|

SU1429109A1 |

| Устройство для деления | 1988 |

|

SU1541598A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Суммирующе-вычитающее устройство | 1977 |

|

SU667967A1 |

Даты

1969-01-01—Публикация