ИзОбретение предназначено для использования IB системах автоматизации учета и оперативного управления с лрименением электронных вычислительных машин.

Устройства ввода с преобразованием десятичного кода в двоично-десятичный код, содержащие регистр устройства ввода, коммутатор, шифратор, блоки автономного управления, блок оперативной памяти, выходной регистр, клапаны и схемы сборки, известны.

Однако из вестные устройства имеют низкое быстродействие и большое количество оборудования.

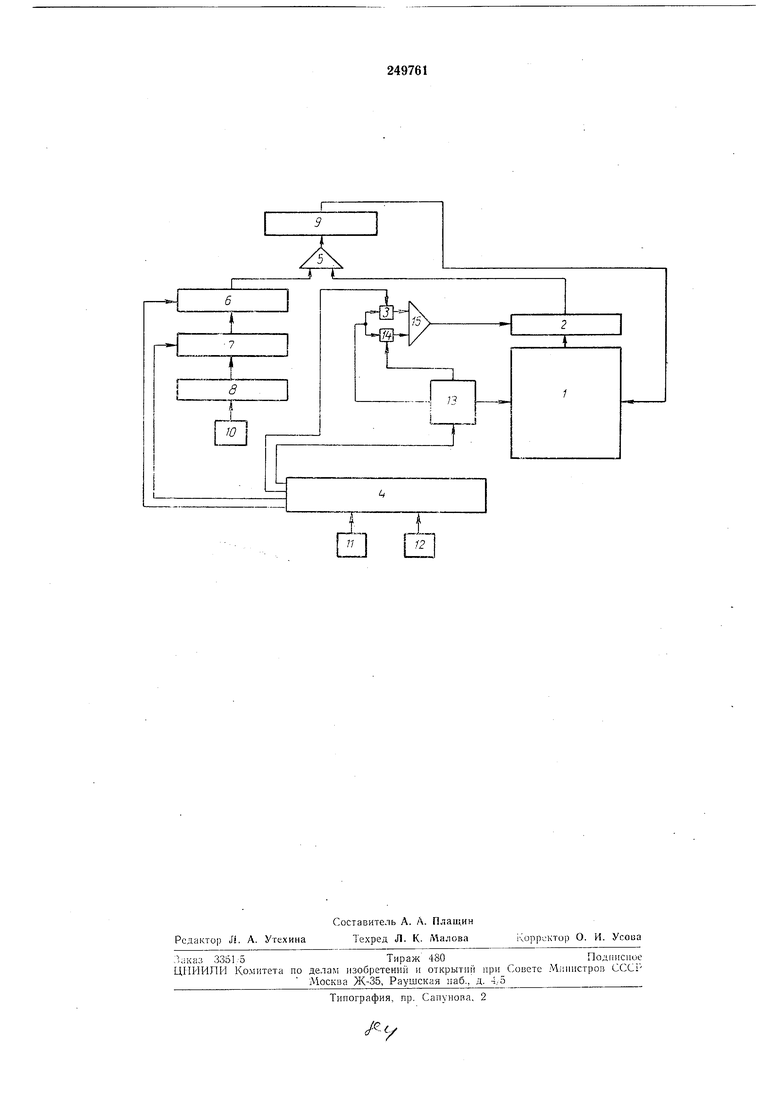

Предложенное устройство отличается от известных тем, что, с целью повышения быстродействия устройства и его упрош,ения, в нем выход шифратора подключен к одному входу схемы сборки, другой вход которой соединен с выходными клапанами блока о-перативной памяти, выход схемы сборки подключен к выходному регистру блока оперативной памяти, выходы блоков автономного управления устройства преобразования и блока оперативной памяти Подключены соответственно ко входам клапана, выходы которого через схему сборки соединены со входами стробирования выходных клапанов блока оперативной памяти.

В устройстве между схемой выработки сигнала стробирования выходных клапанов оперативной памяти иа ферритах НФ 1 и выходными клапанами 2 НФ 1 ЭЦВМ включен клапан 5, управляемый от блока 4 автономного управления. Устройство снабжено диодной сборкой 5, входы которой подключены к -выходным клапанам 2 и через шифратор 6 и коммутатор каналов 7 - к буферному регистру 8, а выход - к выходному регистру 9 НФ ; ЭЦВМ.

Предположим, что информацию, считываемую с десятичной карты 10 следует записать в двоично-десятичном коде в группу ячеек

оперативной памяти (oi, а, ..., а„, ..., Предположим, что ячейка оперативной памяти .состоит из т тетрад (при работе устройства это условие несущественно).

Предположим далее, что перепись информации из буферного регистра 8 в оперативную память осуществляется после считывания каждой строки карты (это имеет место в большей части машин).

При обращении к устройству ввода на регистр адреса блока 4 автономного управления устройства преобразования из устройства управления И ЭЦВМ заносится адрес начальной ячейки. После считывания пулевой строки карты

передается сигналом управления -с блока 12 в блок 4, НФ 1 получает адрес из регистра адреса блока 4.

Число, которое должно быть занесено на регистр 9 для записи в куб, получается еледующим образом. Коммутатор каналов 7 подключает к шифратору 6 первые т разрядов регистра 8. На шифратор 6 также подается вес позиции (в двоично-десятичном коде) со счетчика позиций перфокарты, и на регистр 9 заносится в двоично-десятичном коде информация, считанная с первых т колонок нулевой строки, которая записывается IB НФ / по адресу 3i в первом такте 1работы НФ 1. Сигнал окончания такта НФ ) меняет адрес на регистре адреса НФ / на «1 (обычно в вычислительных машинах регистр адреса НФ представляет собой счетчик), переключает коммутатор каналов 7 и снова запускает блок 13 автоматического управления НФ. Теперь по адресу а записывается в двоично-десятичном коде информация, считанная со вторых т колонок перфокарты и т. д. Этот процесс продолжается до полной переписи всей перекодированной нулевой строки в ячейки (QI, fla, . - , а„, ..., Qf,). Затем снова запускается ЭЦВМ. После считывания первой (второй по счету) строки карты ЭЦВМ вновь останавливается, и запускается бло-к 13. Цри этом на регистр адреса НФ 1 вновь заносится адрес a-i из регистра адреса блока 4. Но теперь при переписи информации в НФ / из регистра 8 сигнал блока 4, поступая на клапан 3, разрешает стробирование выходных клапанов 2 оперативной памяти при записи. Клапан 3 открывается каждый раз при переписи содержимого пОСледних девяти строк (с первой по девятую включительно).

Благодаря этому при записи любых /п„ разрядов (/+ 1)-й строки перфокарты в ячейку «д сначала на выходной регистр 9 через сборку 5 выбирается из НФ 1 содержимое

ячейки йд, соответствуюнгее поразрядной логической сумме содержимого /п„ разрядов всех строк перфокарты с О по /-ую включительно. Затем через другие входы сборки 5 заносится перекодированное содержимое от„-х разрядов ()-й строки, т. е. содержимое этих разрядов как бы корректируется, и суммарный результат автоматически регенерируется в ячейке а„. Носле переписи в НФ ,1 всех строк перфокарты в ячейках ui, Сг,

а получаем

информацию, считанную с перфокарты, преобразованную в двоично-десятичный код.

Клапан 14 открывается сигналом «чтения, разрешая стробирование выходных клапанов 2 при выборке чисел и команд из НФ / в арифметическое устройство и устройство управления ЭЦВМ. Сигналы после клапанов 3 и 14 объединяются на сборке 15.

Предмет изобретения

Устройство для ввода информации с преобразованием десятичного кода в двоично-десятичный код, содержащее буферный регистр устройства ввода, соединенный через коммутатор с шифратором, блоки автономного управления, блок оперативной памяти, выходной регистр блока оперативной памяти, клапаны и схемы сборки, отличающееся тем, что, с целью повышения быстродействия устройства и его упрощения, в нем выход шифратора подключен к одному входу схемы сборки, другой вход которой соединен с выходными клапанами блока оперативной памяти, выход схемы сборки подключен к выходному регистру блока оперативной памяти, выходы блоков автономного управления устройства преобразования и блока оперативной памяти подключены соответственно ко входа.м клапана, выходы которого через схему сборки соединены со входами стробирования выходных клапанов блока оперативной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВАЯ МАШИНА ДЛЯ ЦЕНТРАЛИЗОВАННОГО КОНТРОЛЯ | 1968 |

|

SU210492A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Многоканальное устройство для регистрации и индикации аварийных ситуаций | 1990 |

|

SU1796907A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Многокоординатная система числового программного управления | 1972 |

|

SU448435A1 |

| Устройство для вычисления углеродного потенциала | 1984 |

|

SU1257660A1 |

| Устройство отсчета времени в цвм | 1977 |

|

SU691828A1 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Устройство для выфода данных цифровой интегрирующей структуры | 1974 |

|

SU506849A1 |

Даты

1969-01-01—Публикация